Receiver circuit, semiconductor integrated circuit, and test method

A receiver and circuit technology, used in digital circuit testing, electronic circuit testing, receiver monitoring, etc., can solve the problems of impedance mismatch measurement error and accuracy degradation of transmission lines.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Embodiments will now be described with reference to the drawings, wherein like reference numerals refer to like elements throughout.

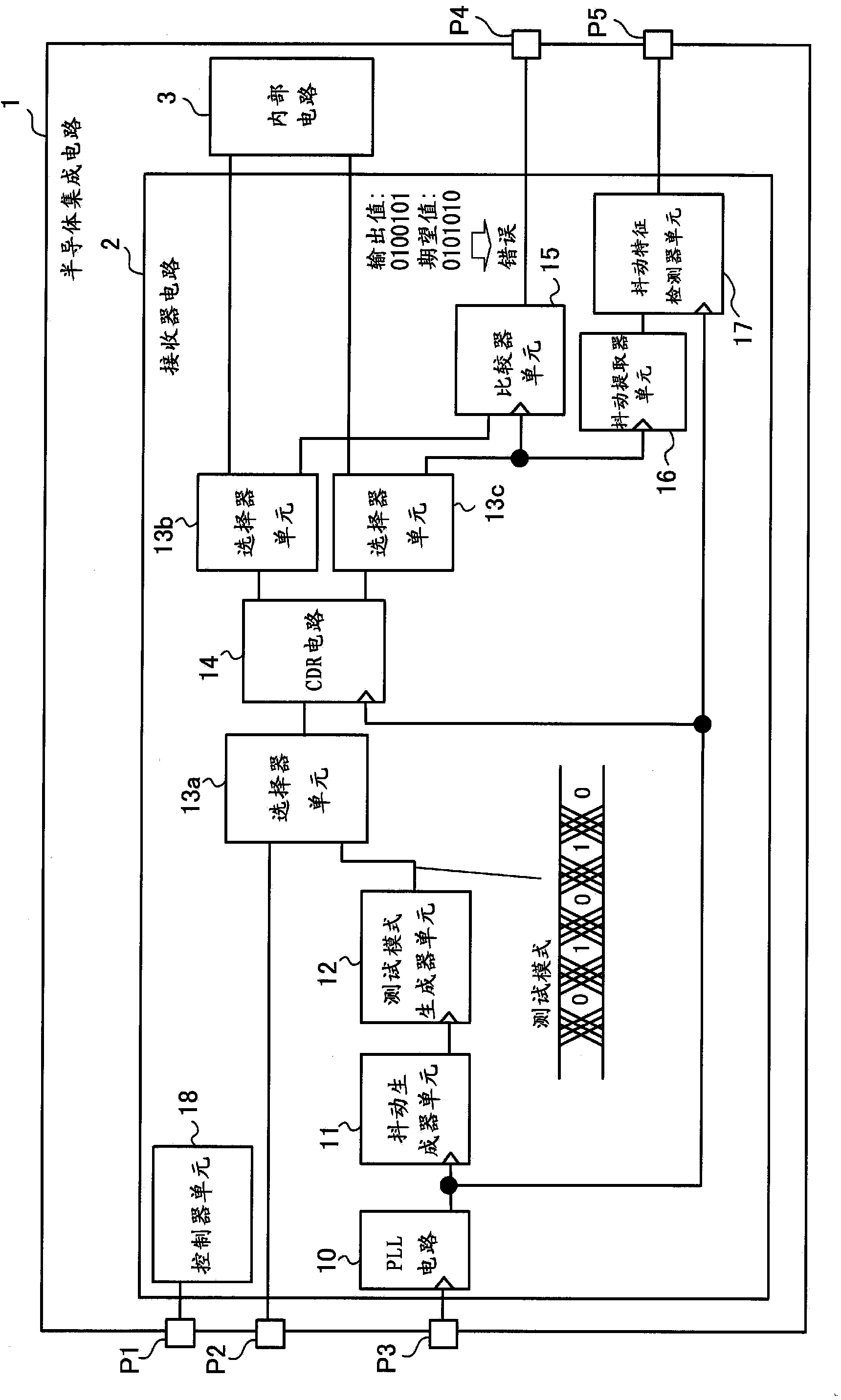

[0030] figure 1 is an example of the semiconductor integrated circuit according to the embodiment.

[0031] The semiconductor integrated circuit 1 includes: a receiver circuit 2; an internal circuit 3 that performs determination operations based on data and clocks received by the receiver circuit 2; and terminals P1, P2, P3, P4, and P5 that input and output various signals.

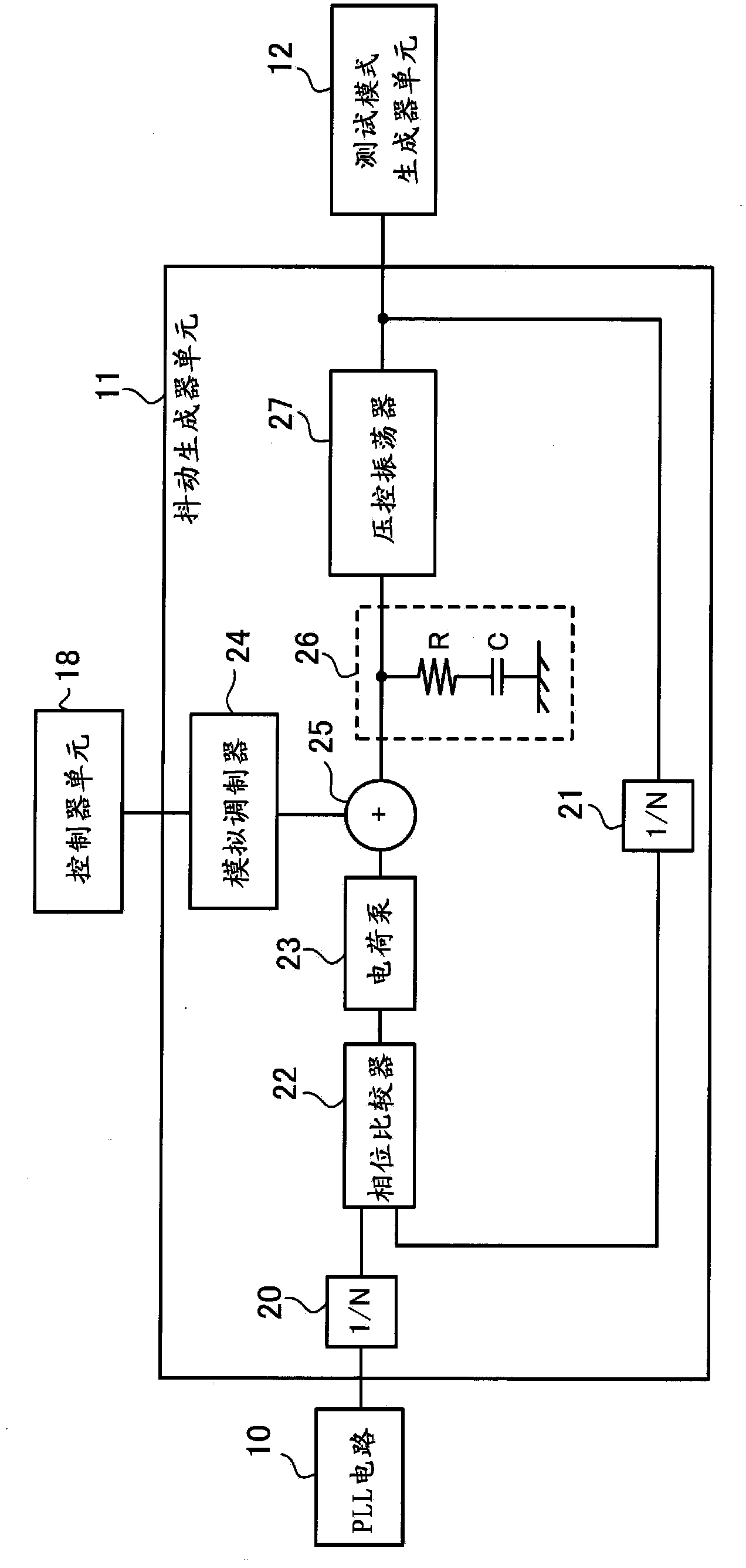

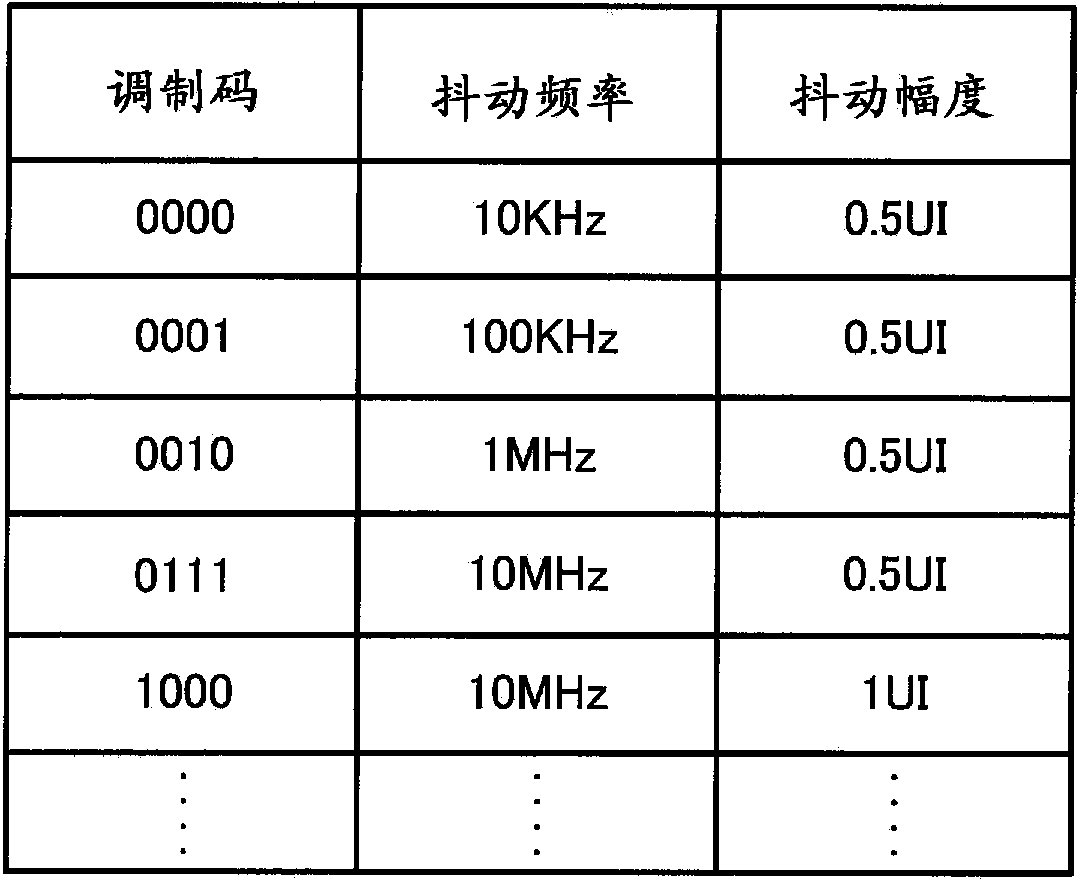

[0032] The receiver circuit 2 includes: a phase locked loop (Phase Locked Loop, PLL) circuit 10, a jitter generator unit 11, a test pattern generator unit 12, selector units 13a, 13b and 13c, a CDR circuit 14, a comparator unit 15, A jitter extractor unit 16 , a jitter signature detector unit 17 , and a controller unit 18 . Each of the jitter generator unit 11, the test pattern generator unit 12, the selector units 13a, 13b, and 13c, the comparator unit 15, the ji...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com