Semiconductor Device And Method Of Manufacturing Same

A semiconductor and lattice position technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as deep energy levels, difficult to reduce resistance, and low solid solution limit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach )

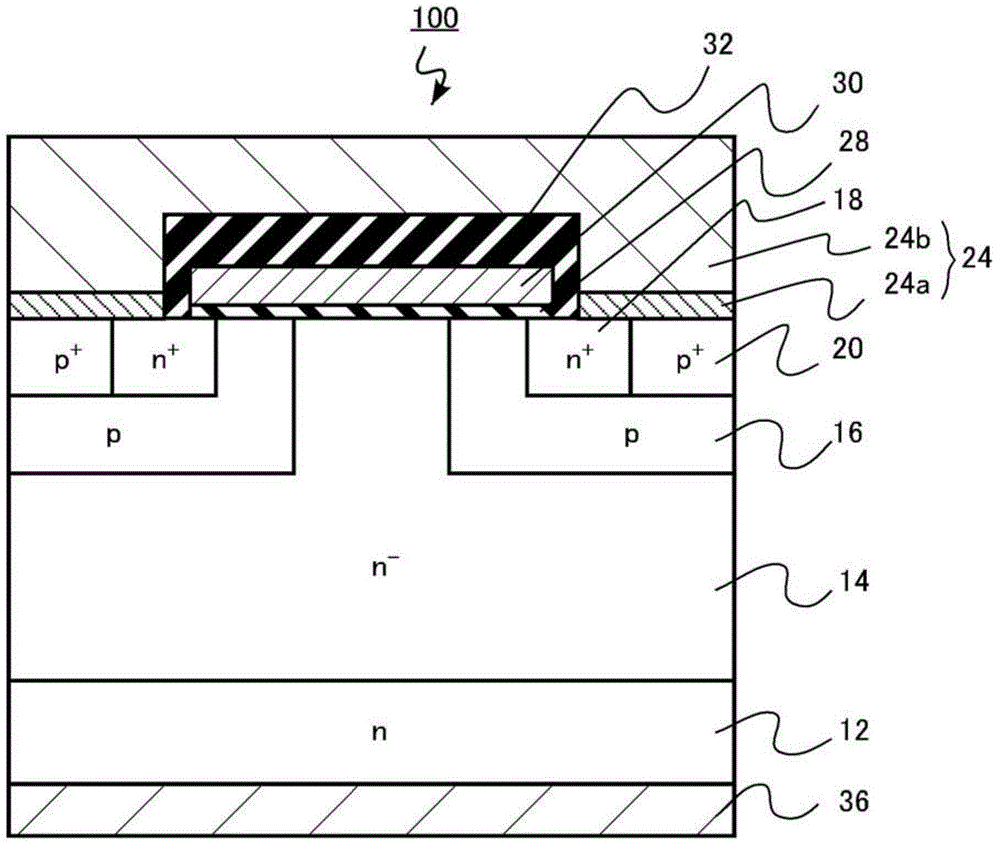

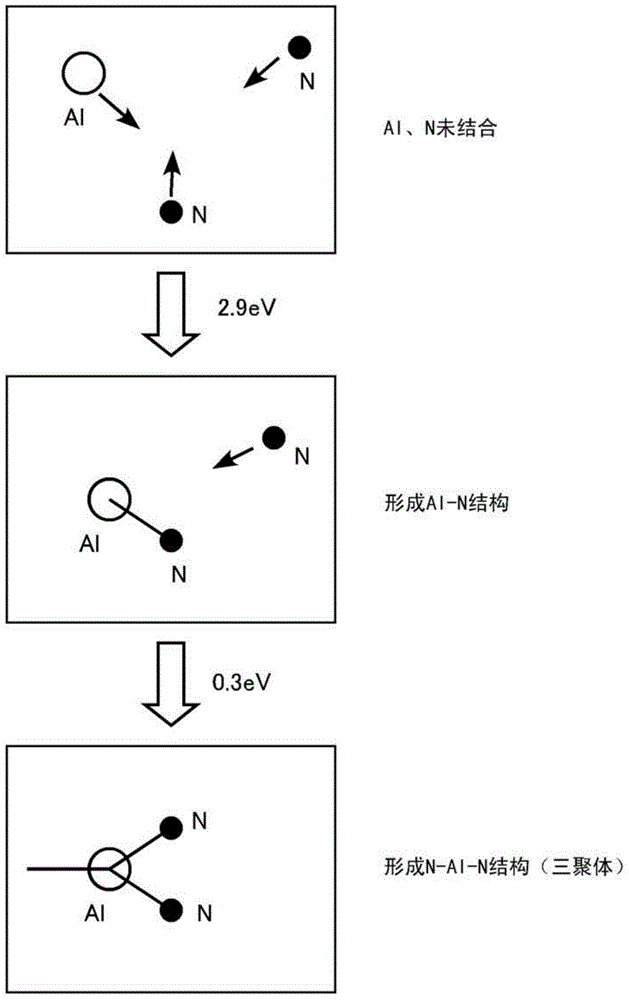

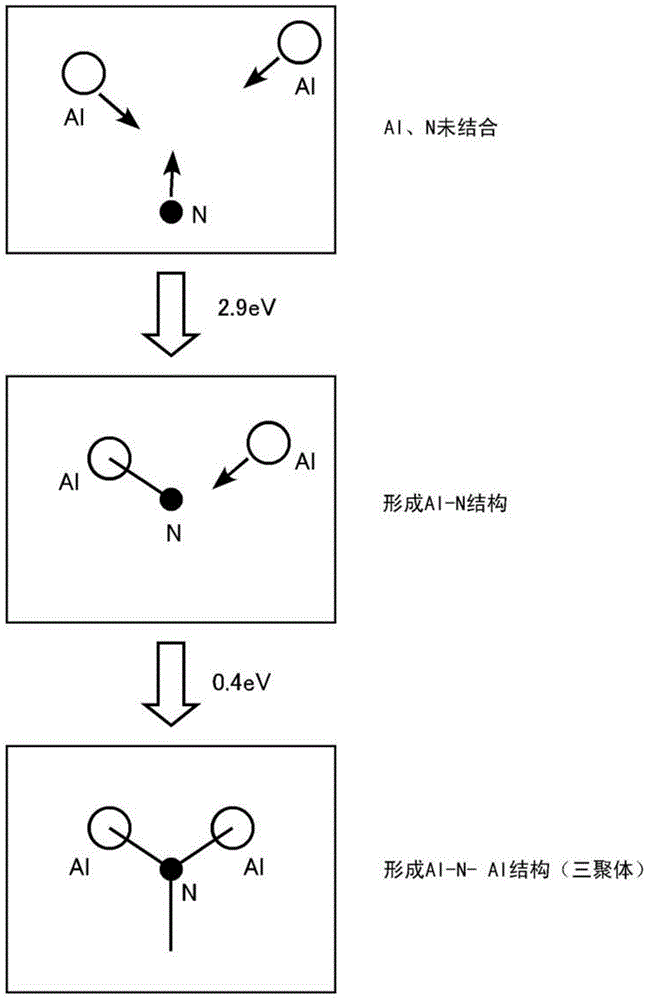

[0037] The semiconductor device of this embodiment includes an n-type SiC substrate having a first surface and a second surface, an n-type SiC layer provided on the first surface side of the SiC substrate, and a p-type first SiC layer formed on the surface of the SiC layer. A SiC region and an n-type second SiC region formed on the surface of the first SiC region. In addition, a p-type third SiC region is provided. The p-type third SiC region is formed on the surface of the first SiC region and contains p-type impurities and n-type impurities. When recorded as element D, the combination of element A and element D is at least one of the combination of Al (aluminum), Ga (gallium), or In (indium) and N (nitrogen), and the combination of B (boron) and P (phosphorus). A combination in which the ratio of the concentration of element D to the concentration of element A (concentration D / concentration A) that constitutes the above combination is greater than 0.33 and less than 0.995, a...

no. 2 approach )

[0160] except in n + The semiconductor device of this embodiment is the same as that of the first embodiment except that the p-type impurity and n-type impurity are also co-doped in the second SiC region. Therefore, the description of the contents overlapping with the first embodiment will be omitted.

[0161] In the semiconductor device of this embodiment mode, in figure 1 MOSFET100, the n + Type second SiC region (source region) 18 is co-doped with p-type impurities and n-type impurities. Also, when the p-type impurity in the second SiC region (source region) 18 is denoted as element A and the n-type impurity is denoted as element D, the combination of element A and element D is Al (aluminum), Ga (gallium) Or at least one combination of a combination of In (indium) and N (nitrogen) and a combination of B (boron) and P (phosphorus). For example, element A is Al and element D is N.

[0162] In the MOSFET of this embodiment, at n + The second SiC region (source region) 18...

no. 3 approach )

[0182] The semiconductor device of this embodiment includes an n-type SiC substrate having a first surface and a second surface, and an n-type SiC layer provided on the first surface side of the SiC substrate. In addition, a p-type SiC region is provided. The p-type SiC region is formed on the surface of the SiC layer and contains p-type impurities and n-type impurities. When the p-type impurity is expressed as element A and the n-type impurity is expressed as element D, The combination of element A and element D is at least one of the combination of Al (aluminum), Ga (gallium) or In (indium) and N (nitrogen), and the combination of B (boron) and P (phosphorus), forming the above The ratio of the concentration of element D in combination to the concentration of element A (concentration D / concentration A) is greater than 0.33 and less than 0.995, and the concentration of element A constituting the above combination is 1×10 18 cm -3 Above and 1×10 22 cm -3 the following. Fur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More