Bonding alignment mark and method for calculating offset

An alignment mark and offset technology, applied in semiconductor/solid-state device testing/measurement, electrical components, electrical solid-state devices, etc., can solve the problems of poor control of the bonding process and results, and improve production quality and quality. rate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

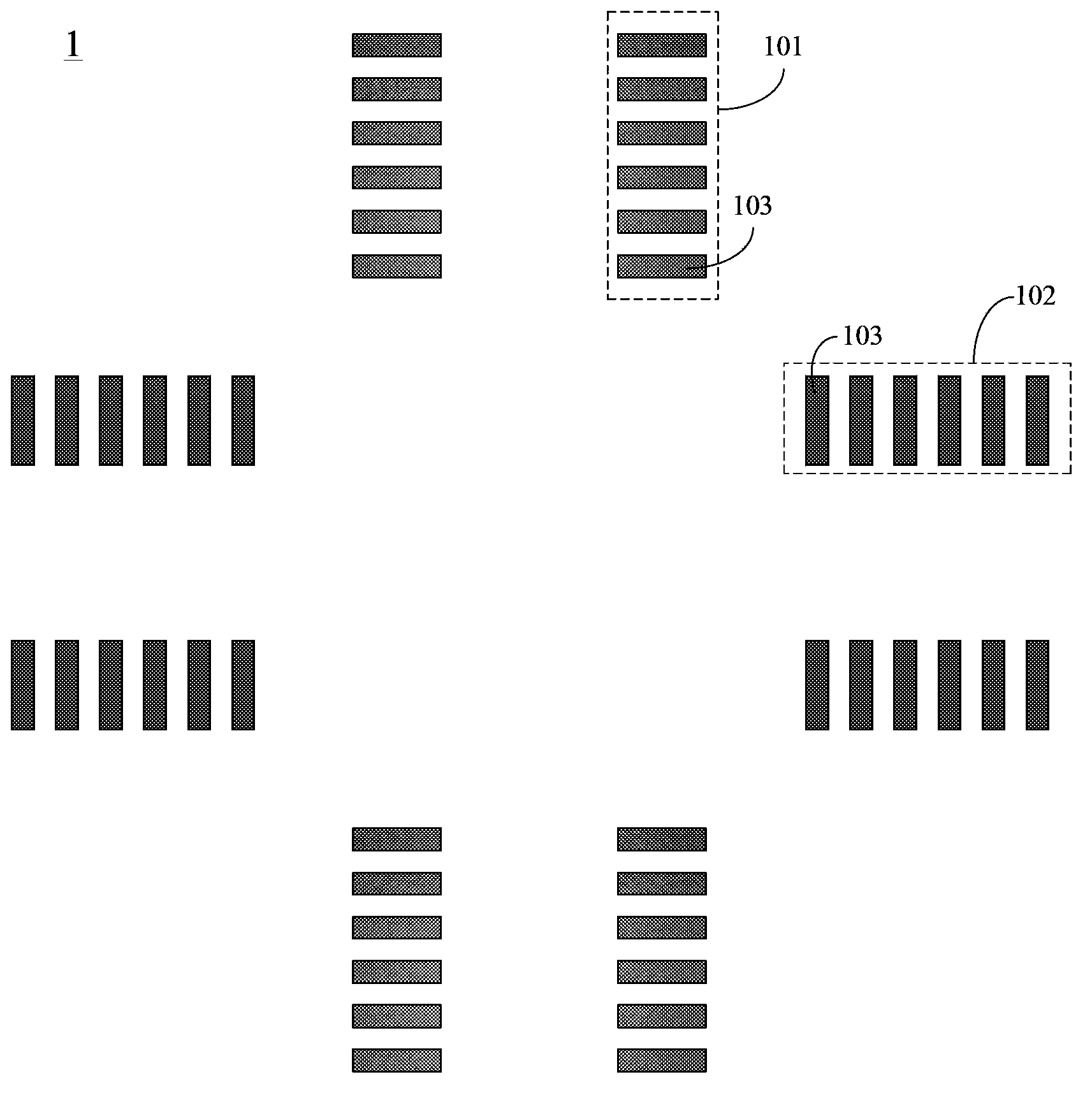

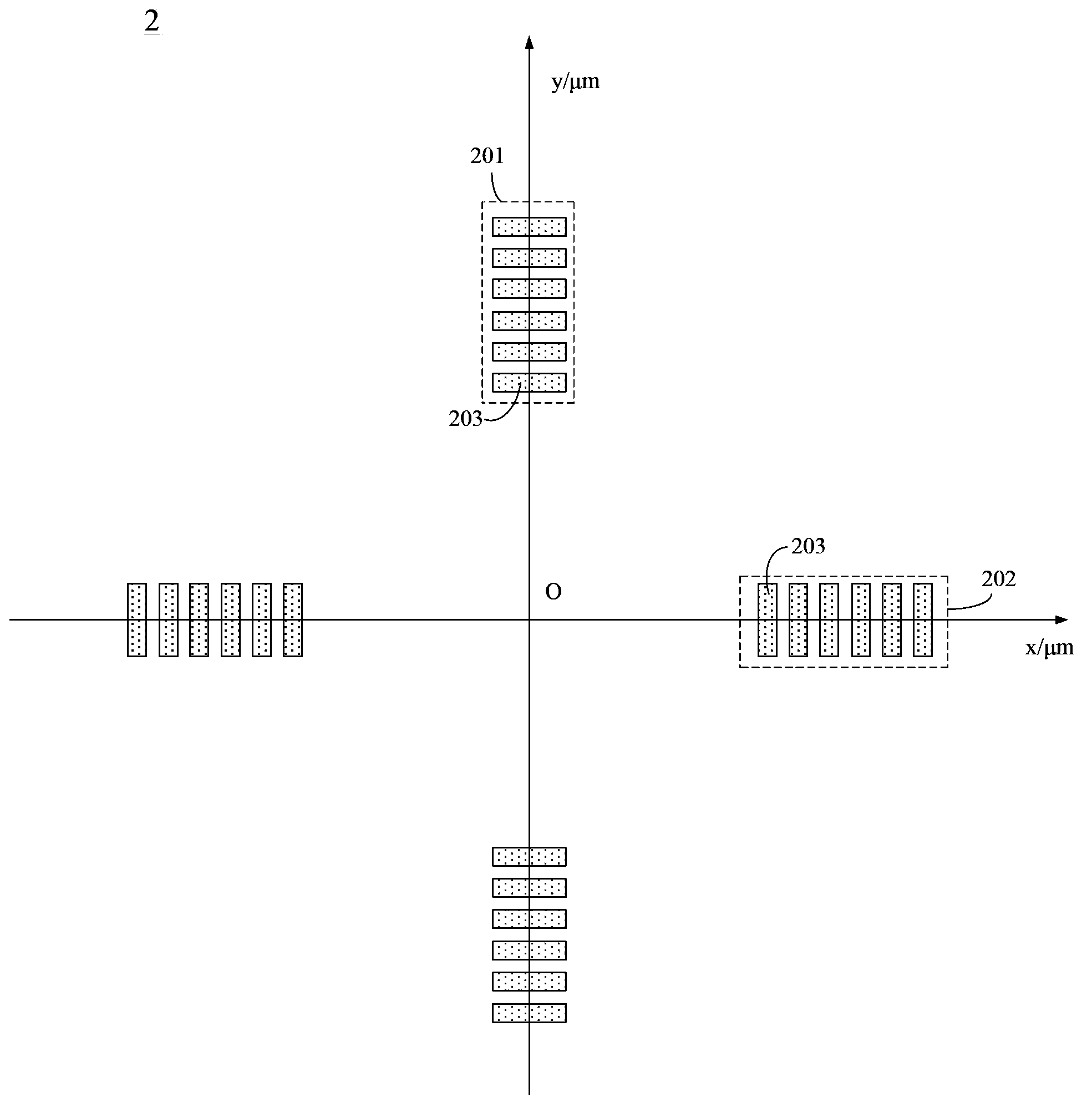

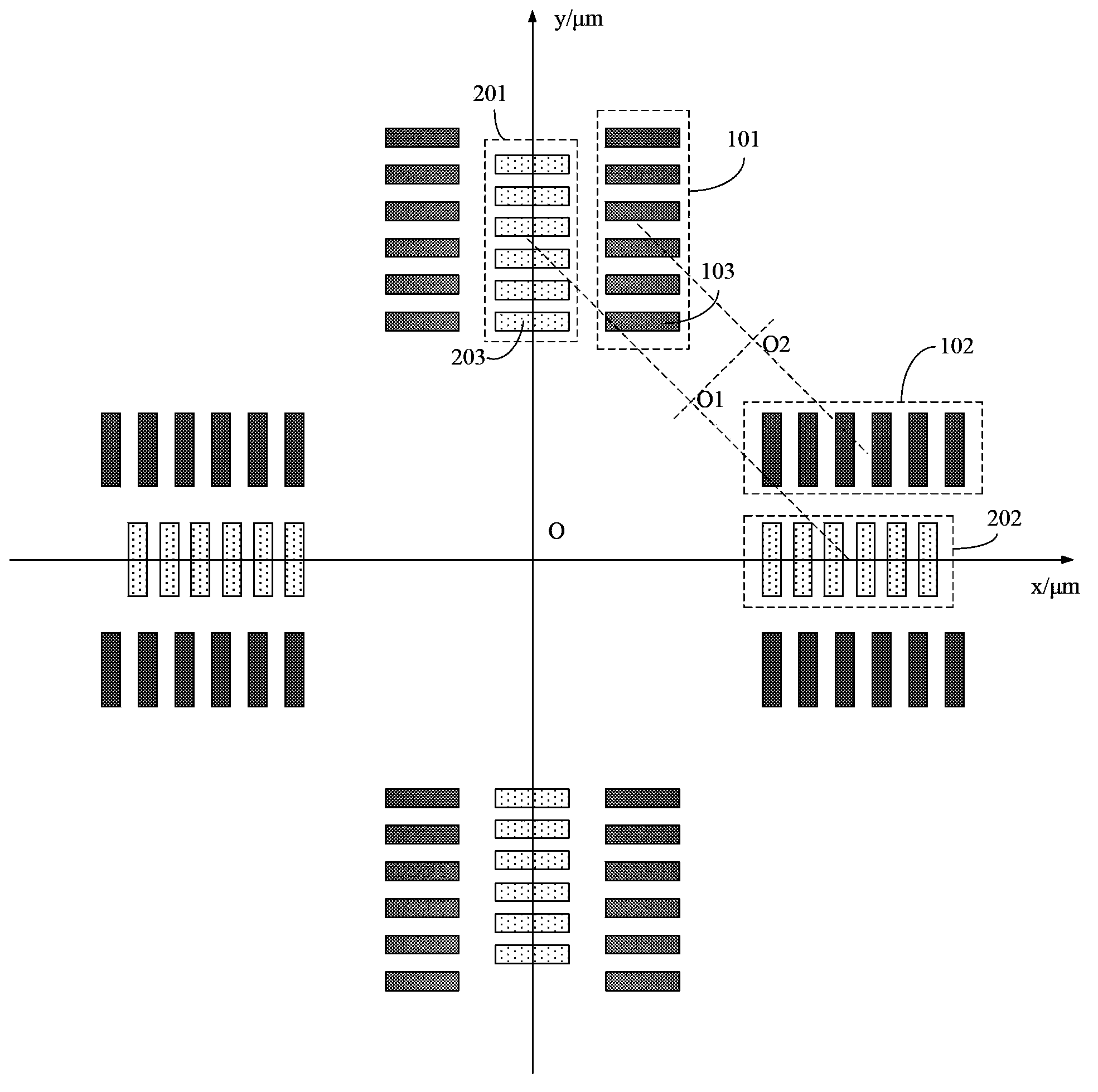

[0031] It has been mentioned in the background that at present, due to the shortage of equipment involved in the bonding process, silicon wafers are prone to large deviations during bonding. After long-term experiments, the inventors found that by making full use of existing resources and forming alignment marks with a specific structure on the silicon wafers to be bonded, the deviation of the silicon wafers can be reduced as much as possible.

[0032] The bonding alignment mark and the method for calculating the offset provided by the present invention will be further described in detail below with reference to the drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in a very simplified form, and are only used for the purpose of conveniently and clearly assisting in describing the embodiments of the present invention.

[0033] First please ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More