Multi-substrate three-dimensional chip packaging method

A three-dimensional packaging and multi-substrate technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems that cannot satisfy users, violate the original intention of design, and cannot meet wiring requirements, etc., and achieve the elimination of peripheral circuits and components. device, reduce design difficulty and cost, and improve the effect of signal integrity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

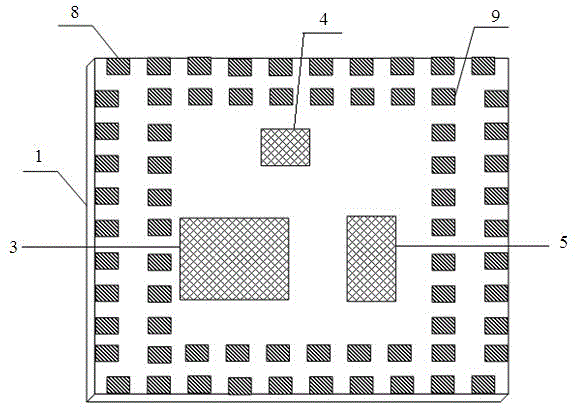

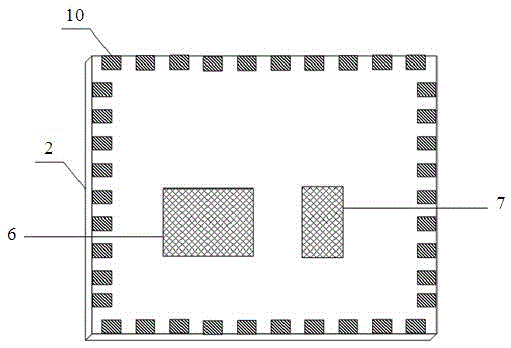

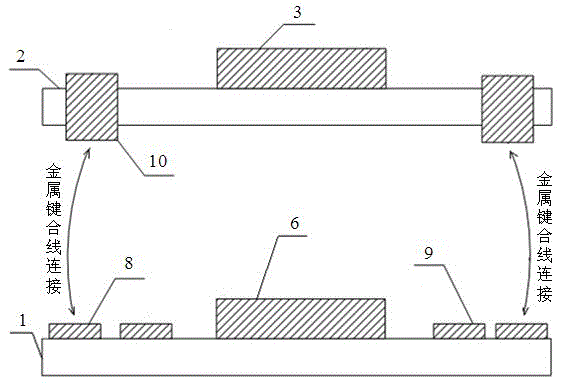

[0034] This embodiment designs a three-dimensional package chip with two substrates (see Figure 1-3 ), the chip substrate includes a main substrate 1, a sub-substrate 2, a first bare chip 3, a second bare chip 4, a third bare chip 5, a fourth bare chip 6 and a fifth bare chip 7; the main substrate 1 is close to There are two circles of PAD points around the edge, namely the outer circle PAD point 8 and the inner circle PAD point 9; the first bare chip 3, the second bare chip 4, and the third bare chip 5 are respectively installed on the main substrate 1, It is connected with the inner ring PAD point 9 through the printed wire; the fourth bare chip 6 and the fifth bare chip 7 are respectively installed on the sub-substrate 2; the edge of the sub-substrate 2 has a circle of PAD points 10, the fourth The signals to be drawn from the bare chip 6 and the fifth bare chip 7 are connected to the PAD point 10 through the printed wire. The signal to be drawn is connected to the outer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More