An on-chip reference clock generation circuit and method

A technology for generating circuits and reference clocks, applied to electrical components, automatic power control, etc., can solve the problems of increasing and reducing costs, large chip area, unfavorable integration of discrete devices, etc., and achieve high stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to have a clearer understanding of the technical features, purposes and effects of the present invention, the specific implementation manners of the present invention will now be described in detail with reference to the accompanying drawings.

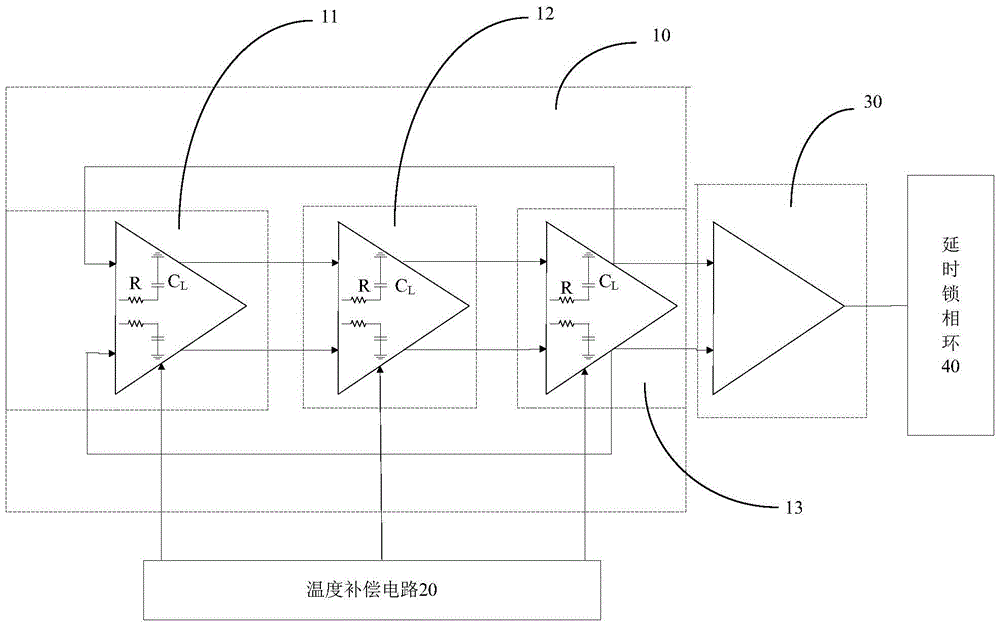

[0035] Such as figure 1As shown, it is a schematic structural diagram of an embodiment of an on-chip reference clock generation circuit of the present invention, the on-chip reference clock generation circuit includes a fully differential ring oscillator circuit 10 formed by cascading a plurality of identical delay units, respectively connected to each A temperature compensation circuit 20 connected to a delay unit, a comparator 30 connected to the two output terminals of the last stage of delay unit, and a delay phase-locked loop 40 connected to the output terminals of the comparator 30 . Among them: because the fully differential ring oscillation circuit 10 is formed by cascading a plurality of identical delay units, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com