Method for flattening through-silicon-via back-surface metal

A planarization method and a technology of penetrating silicon vias, which are applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., and can solve problems such as weak mechanical strength of the dielectric layer, affecting the electrical performance of the through hole, and damage to the dielectric layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to describe the technical content, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

[0018] Before detailing the method for planarizing the metal on the back of the TSV of the present invention, the disclosure of the metal on the back of the TSV will be described first. After the metal on the back of the TSV is exposed, the metal on the back of the TSV is flattened by using the present invention, so that the metal on the back of the TSV is flush. The metal exposure method on the back side of the TSV is not limited to the following method, and the following method is only described as a representative embodiment.

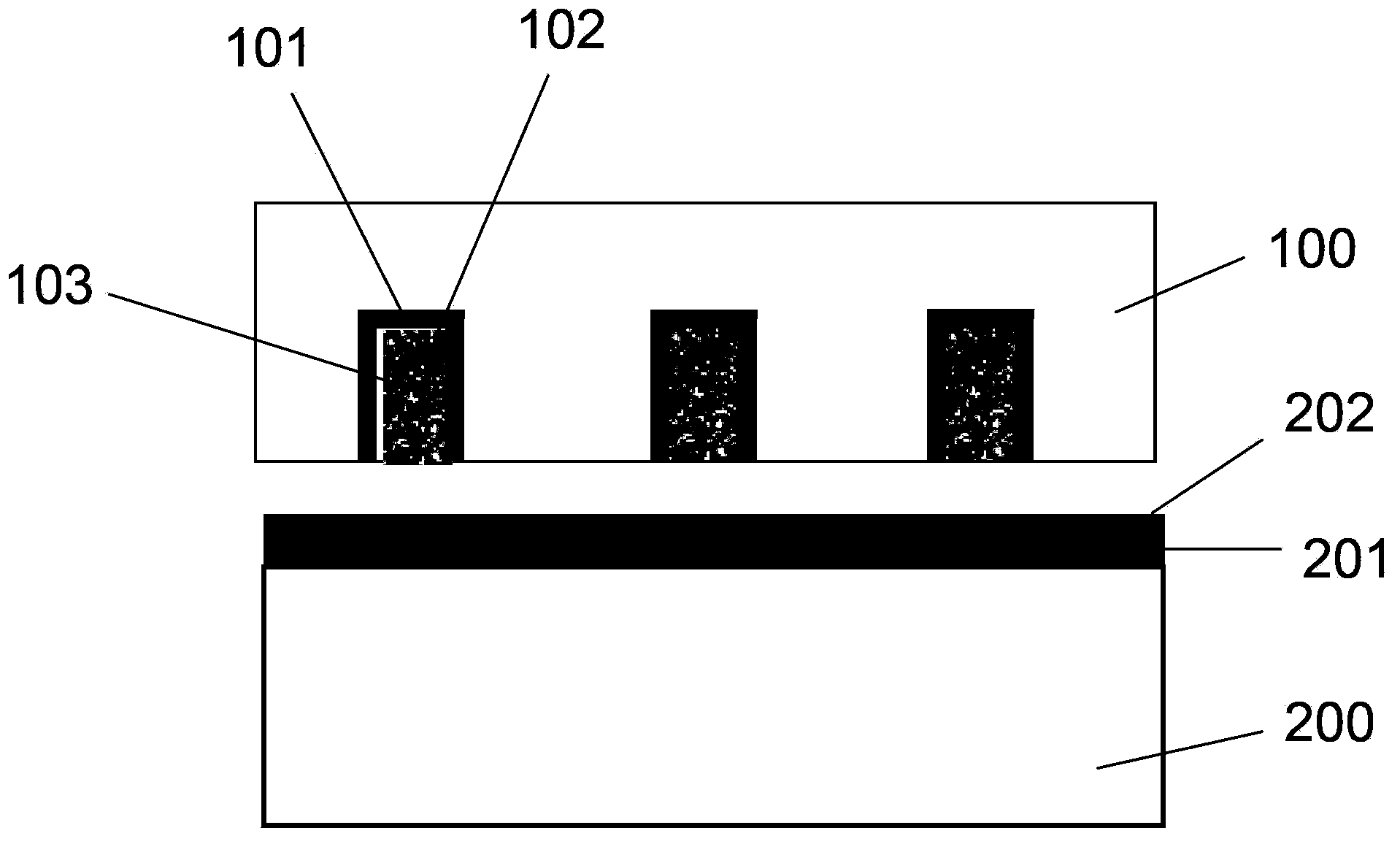

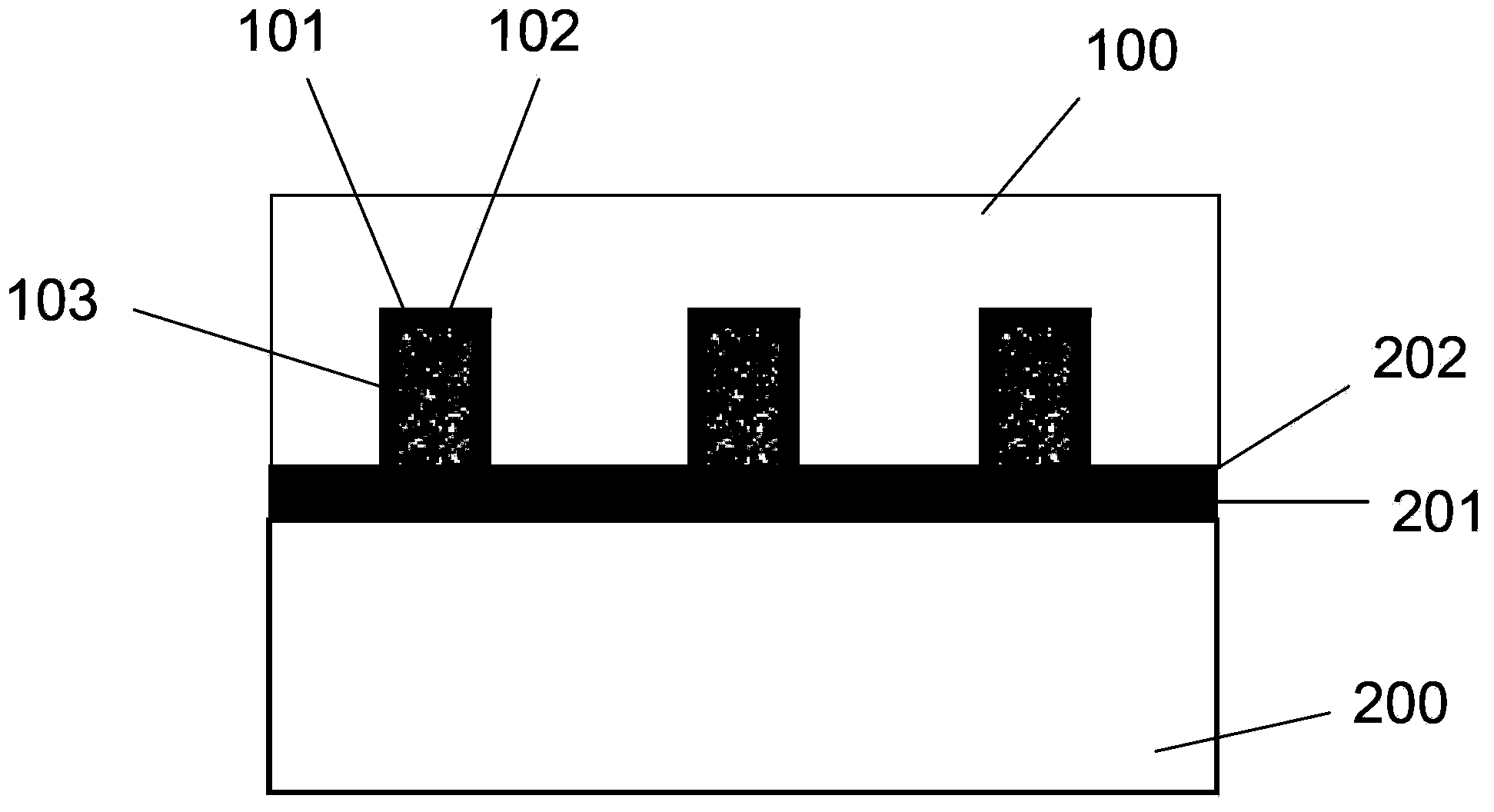

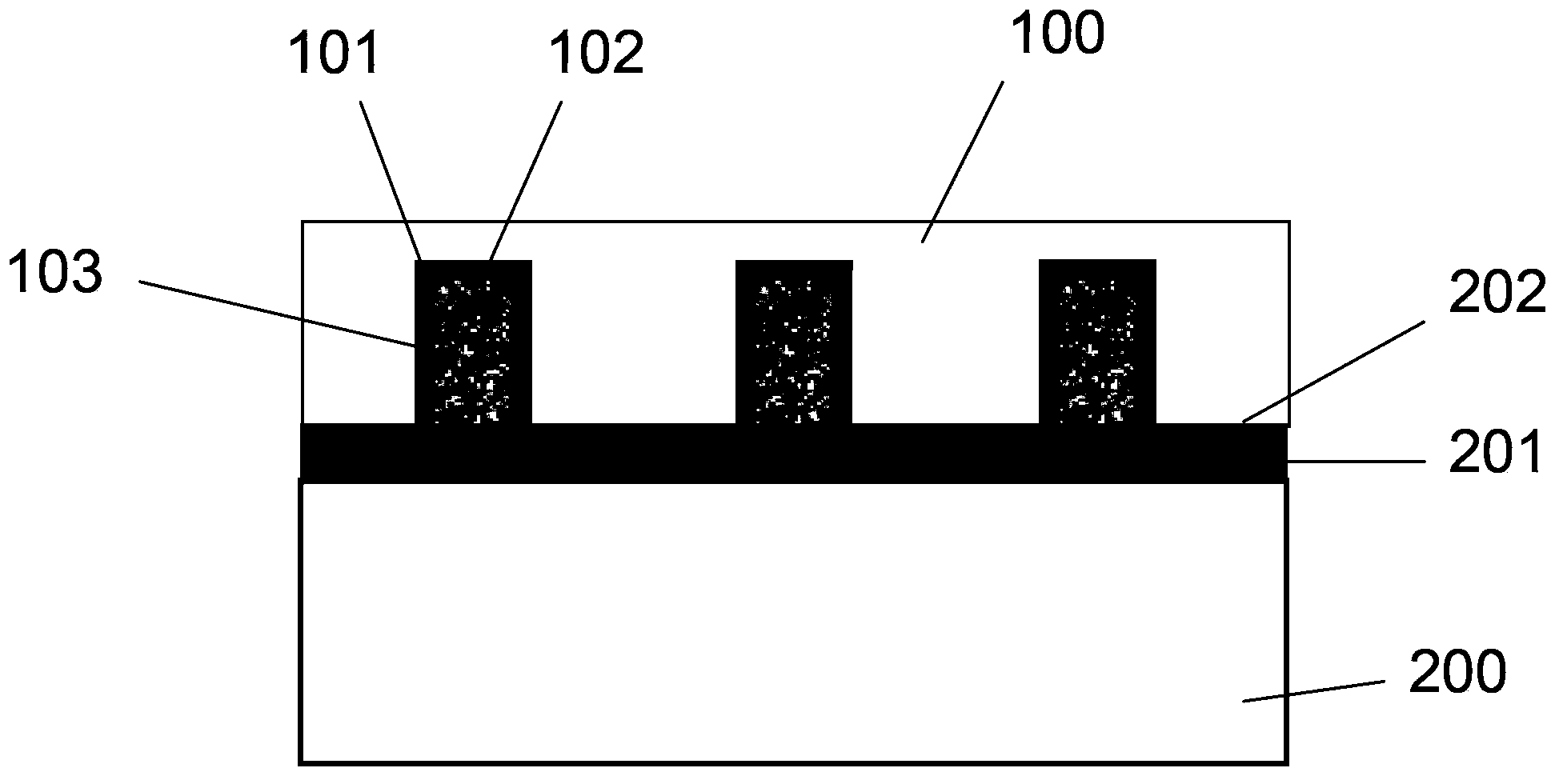

[0019] refer to Figures 1 to 8B The method for exposing the metal on the backside of the TSV includes the following steps:

[0020] First, if figure 1 As shown, a silicon substrate 100 and a carrier sheet 200 are provided. The s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com