A method for implementing gpgpu register cache

An implementation method and register technology, which are applied in the directions of resource allocation, multi-programming device, energy-saving computing, etc., can solve the problems of energy consumption and area waste of GPGPU chips, so as to solve the problem of insufficient number of registers, improve system efficiency, reduce energy consumption and reduce energy consumption. The effect of chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described below in conjunction with drawings and embodiments.

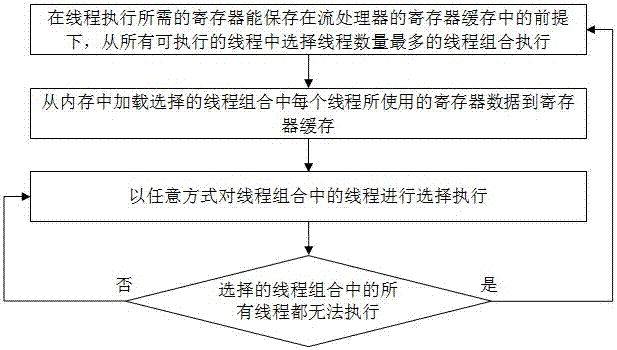

[0021] The method of the invention includes: adding a register cache in each stream processor to replace a register file, adopting an organization mode based on the register cache, and adopting a scheduling mode based on the register cache for stream processor threads.

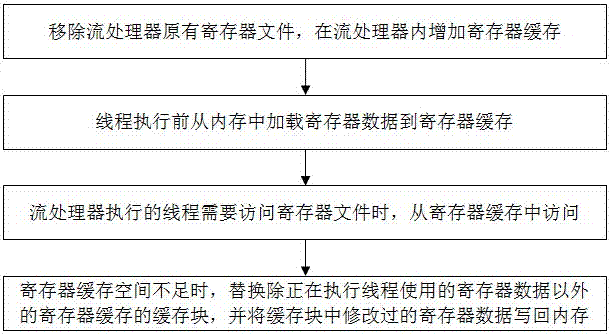

[0022] Such as figure 1 As shown, the above-mentioned organization method based on the register cache is as follows:

[0023] A.1) Remove the original register file of the stream processor, save all the register data in the original register file in the memory, add a register cache for storing the registers required by the executing thread in the stream processor, and replace the original There are register files.

[0024] A.2) Load register data from memory to register cache before thread execution.

[0025] When the thread executed by the stream processor needs to access the register file, it acces...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More