Method for manufacturing coreless substrates of symmetrical structure

A coreless substrate, symmetrical structure technology, applied in the directions of printed circuit manufacturing, electrical components, printed circuits, etc., can solve the problems of difficult to control the rigidity of coreless substrates, achieve good rigidity and flatness, and is not easy to warp , the effect of low material cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

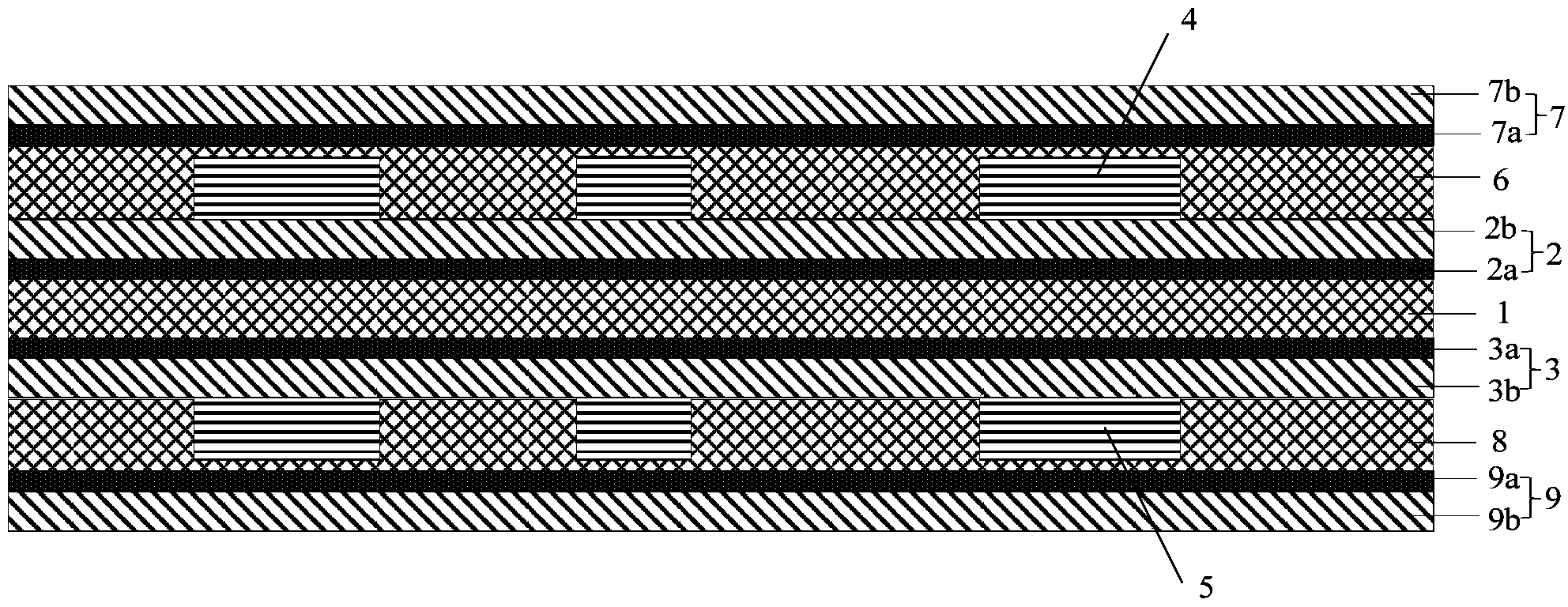

[0031] The present invention will be further described below in conjunction with specific drawings and embodiments.

[0032] The method for preparing a coreless substrate with a symmetrical structure proposed by the present invention specifically includes the following steps:

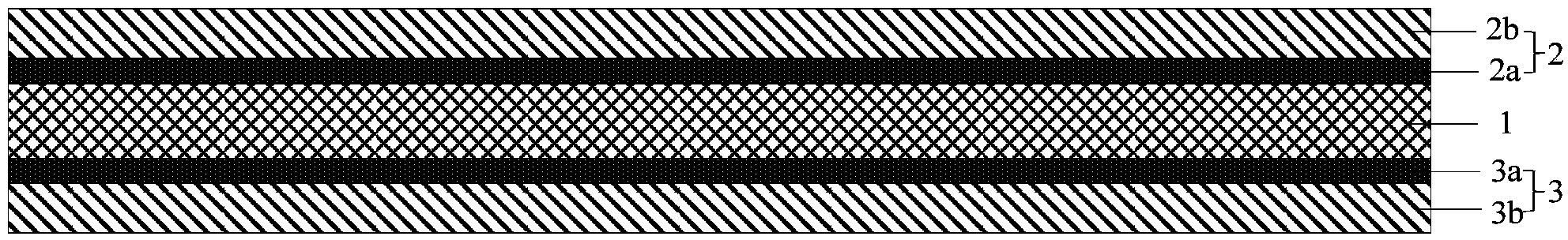

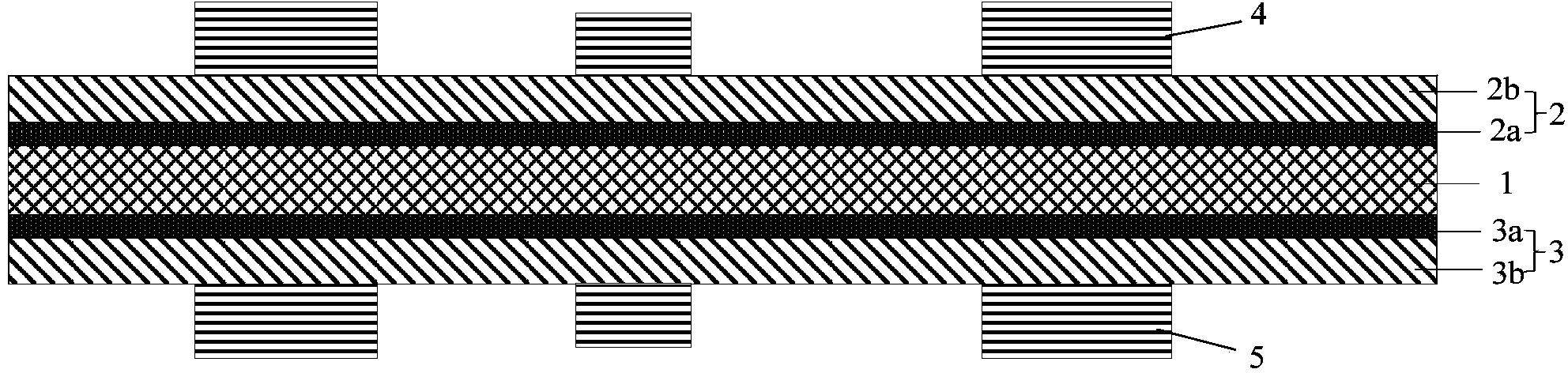

[0033] Such as figure 1 As shown, in step 1, the front inner layer copper foil 2 and the back inner layer copper foil 3 are laminated on the front and back sides of a central prepreg 1 to form a double-sided copper clad laminate; wherein the front inner layer copper foil 2 has a front inner layer base The copper foil 2a and the front inner layer carrier copper foil 2b; the back inner layer copper foil 3 has the back inner layer base copper foil 3a and the back inner layer carrier copper foil 3b; Copper foil 2a and back inner layer base copper foil 3a;

[0034] In this step, the front inner layer base copper foil 2a and the back inner layer base copper foil 3a are both made of 3um ultra-thin copper foi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More