Manufacturing method for thin coreless substrate

A technology of thin substrates and manufacturing methods, which is applied in the direction of multilayer circuit manufacturing, semiconductor/solid-state device manufacturing, and electrical connection formation of printed components, etc. It can solve the problems of increasing the difficulty of controlling the thickness of the line and the difficulty of arbitrary interconnection of circuits, etc., and achieves low cost. , reduce thickness and reduce cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0042] The manufacturing method of the coreless thin substrate of this embodiment includes the following steps:

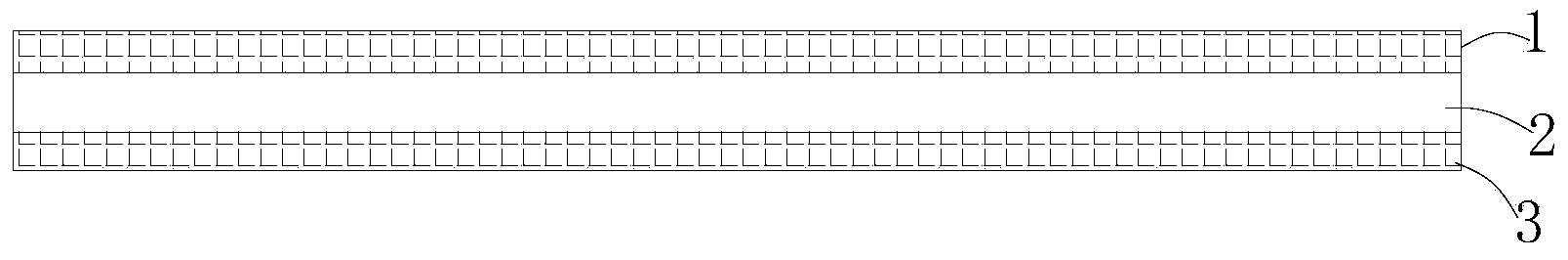

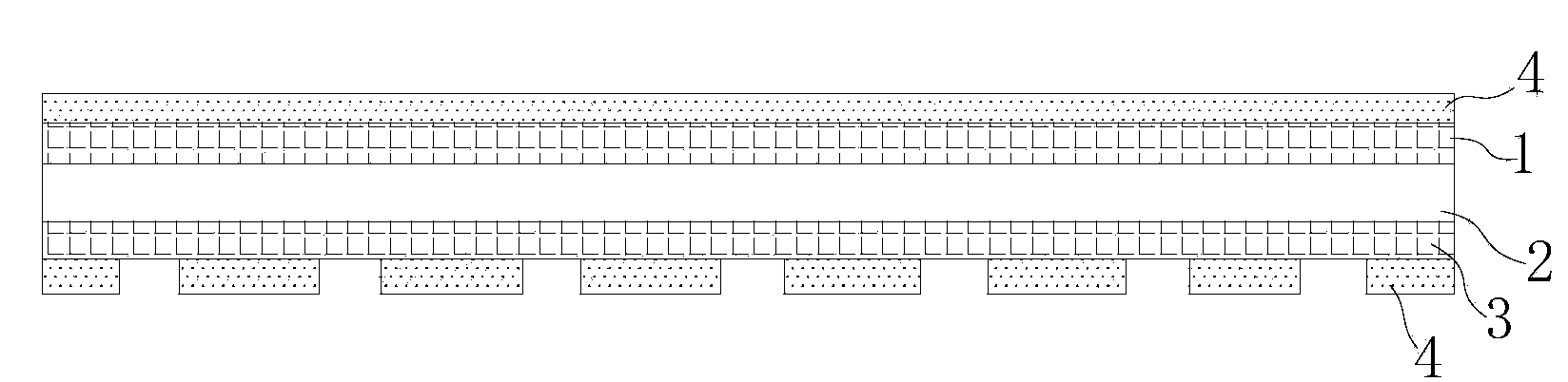

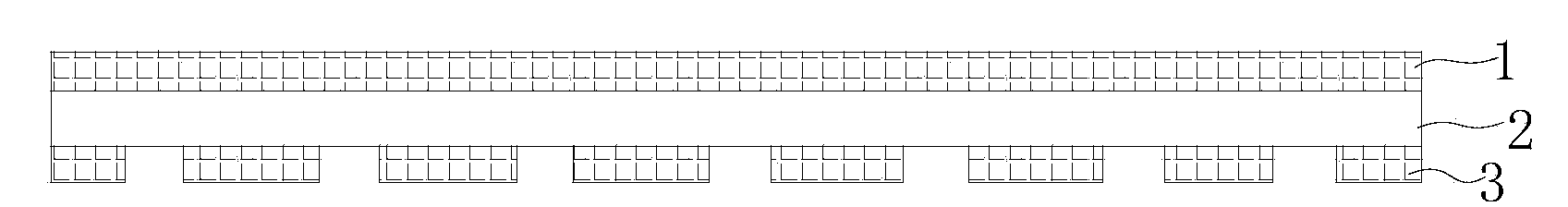

[0043] a. Laminate the first copper foil 1, the first prepreg 2, and the second copper foil 3 from top to bottom in order for the first pressing. The first pressing is low-temperature vacuum pressing, and the pressing temperature is the first prepreg The temperature at which the viscosity of 2 is the lowest, this embodiment is preferably 110°C, and it is pressed under a certain pressure with a vacuum laminator for 15-25 minutes, and it is preferably 20 minutes in this embodiment to obtain the first substrate, such as figure 1 As shown, the double-sided copper clad prepreg; the first substrate is subjected to dry film pretreatment, such as cleaning or acid treatment, and then the first dry film 4 is pressed on the surface of the first copper foil 1 and the second copper foil 3 respectively, and The first dry film 4 pressed on the surface of the second copper foil 3 is s...

Embodiment 2

[0050] This embodiment differs from embodiment 1 in that: after step d, step e2 replaces step e1, and the third prepreg 14 is laminated on both sides of the substrate model prepared in step d, and the third prepreg 14 is laminated on the third prepreg 14. Laminate a specific number of multi-layer circuits 15 to prepare a multi-layer odd-numbered board, such as Figure 15 As shown, the multilayer circuit is also respectively connected to the first circuit and the third circuit through blind holes. The build-up method used in this embodiment is just a conventional method for manufacturing a multilayer board, and will not be repeated here.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More