Semiconductor structure for suppressing harmonic effect and method for forming a structure for suppressing harmonic effect

A harmonic effect, semiconductor technology, applied in the field of suppressing harmonic effects in semiconductor structures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

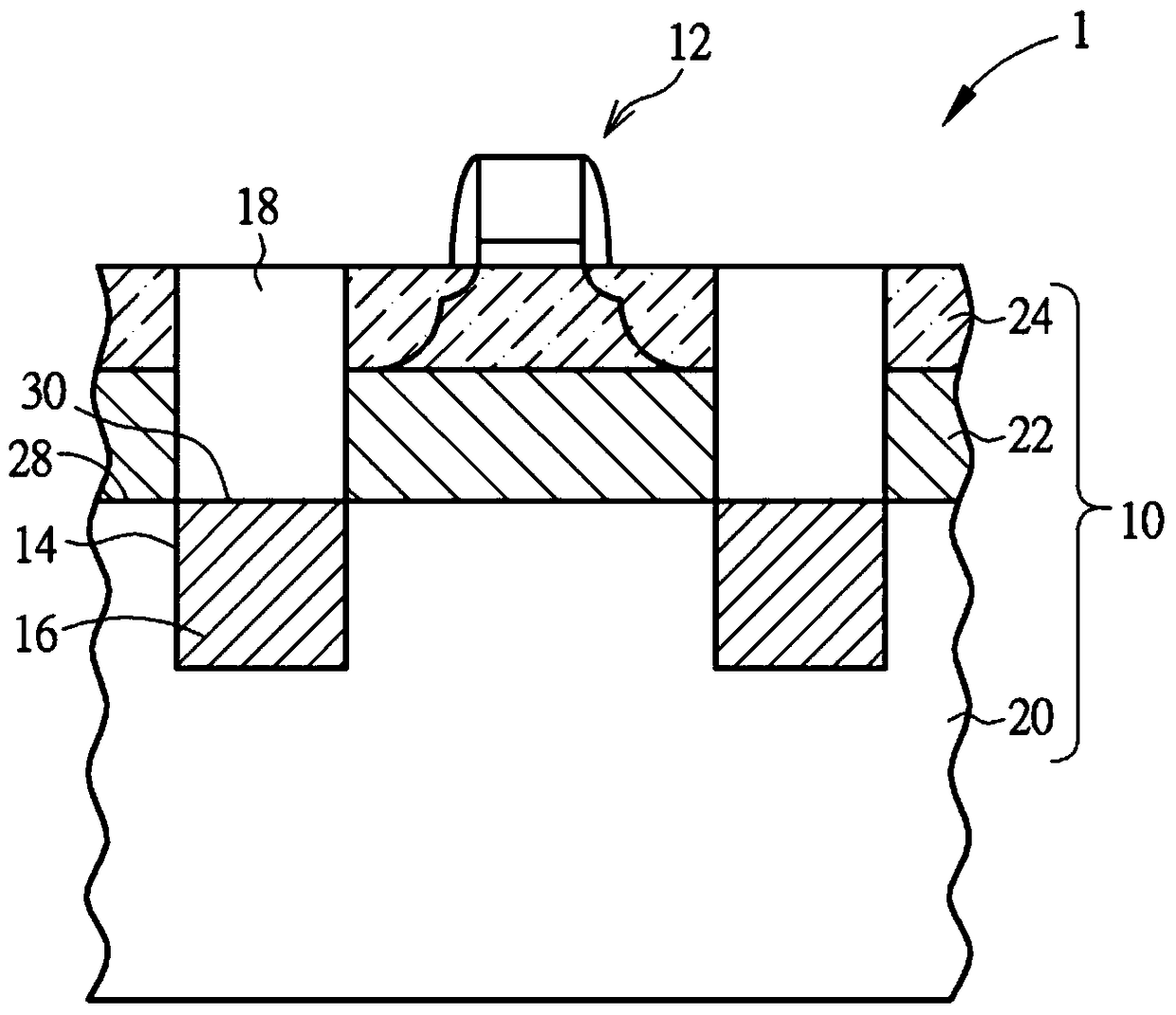

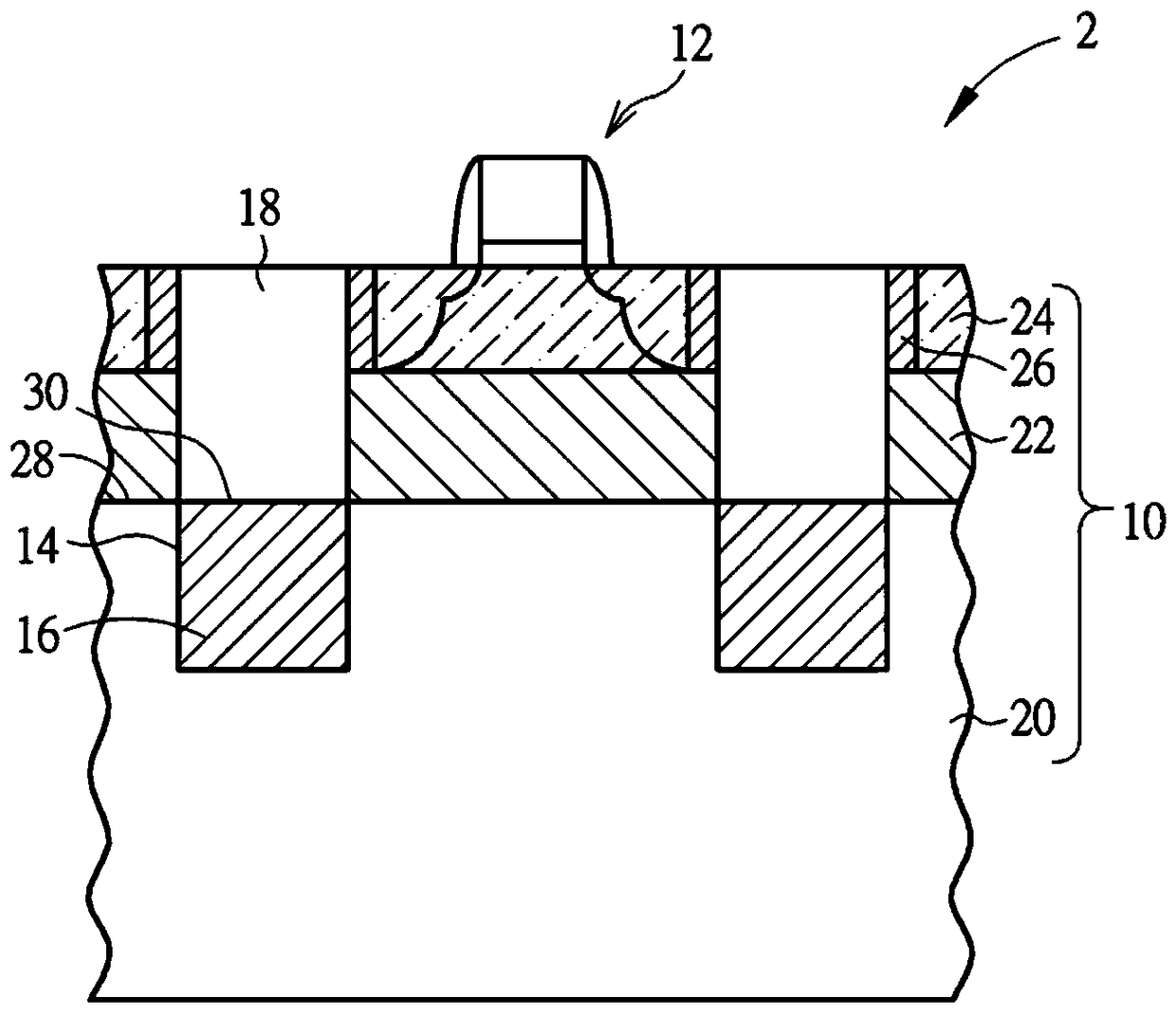

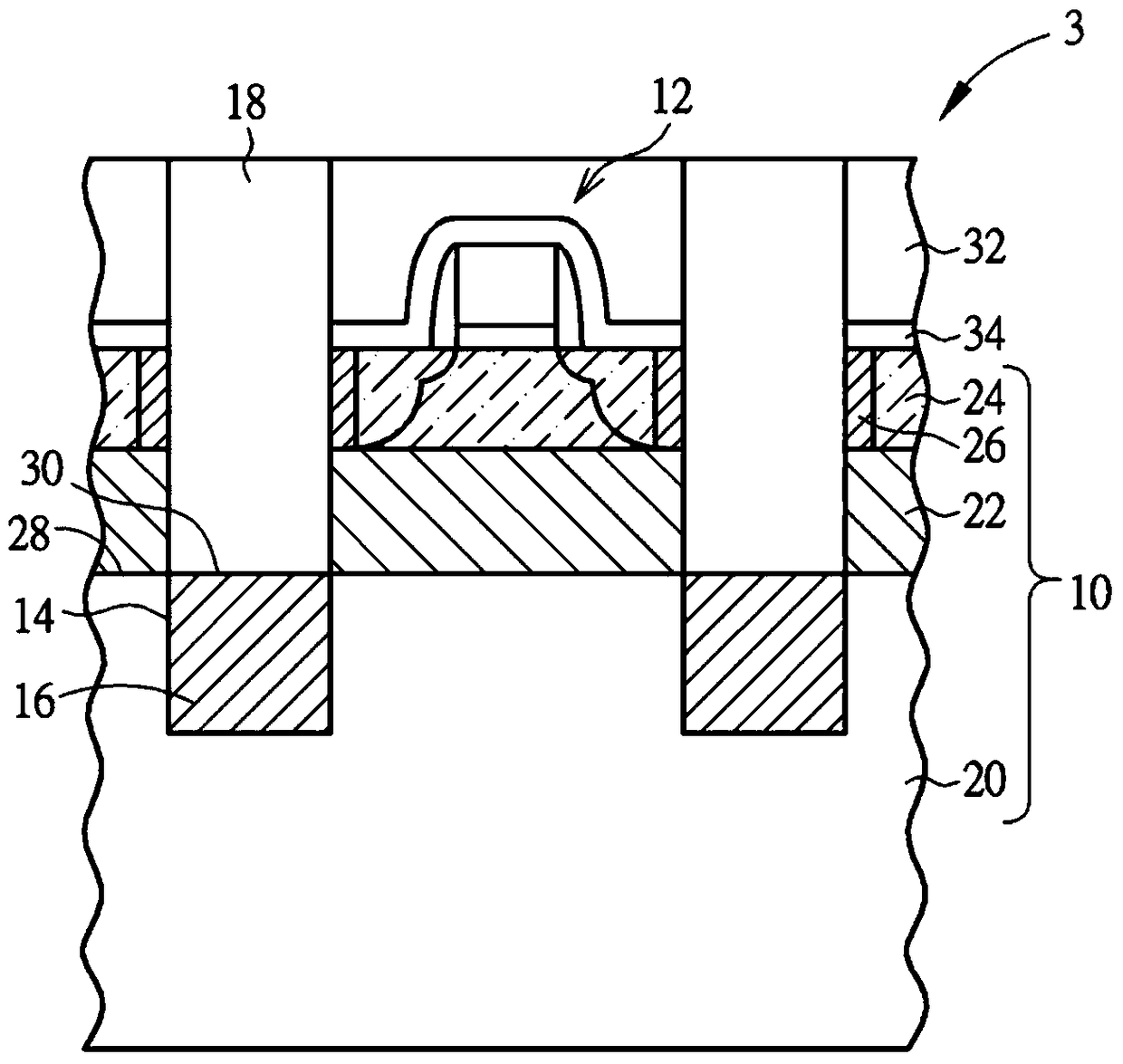

[0023] Figure 1 to Figure 5 A schematic cross-sectional view showing a semiconductor structure capable of suppressing harmonic effects according to several embodiments of several aspects of the present invention. see figure 1 A semiconductor structure 1 capable of suppressing harmonic effects according to an embodiment of the present invention includes a semiconductor substrate 10 , a device 12 , a deep trench 14 , a silicon layer 16 , and a dielectric layer 18 . The semiconductor substrate 10 includes a semiconductor substrate base 20, a buried dielectric layer (buried dielectric) 22 on the semiconductor substrate base 20, a surface semiconductor layer 24 on the buried dielectric layer 22, and a semiconductor layer located in the surface semiconductor layer 24. The shallow trench isolation layer 26. The semiconductor substrate base 20 may include, for example, a high-resistance silicon material such as an amorphous silicon layer or a silicon base with a silicon germanium (...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More