PUFs (physical unclonable functions) circuit based on transmission delay multiplexing

A delay circuit and delay chain technology, applied in the direction of electrical program control, program control in sequence/logic controller, internal/peripheral computer component protection, etc., can solve low circuit utilization, increase the number of PUFs circuits, and increase circuit cost And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

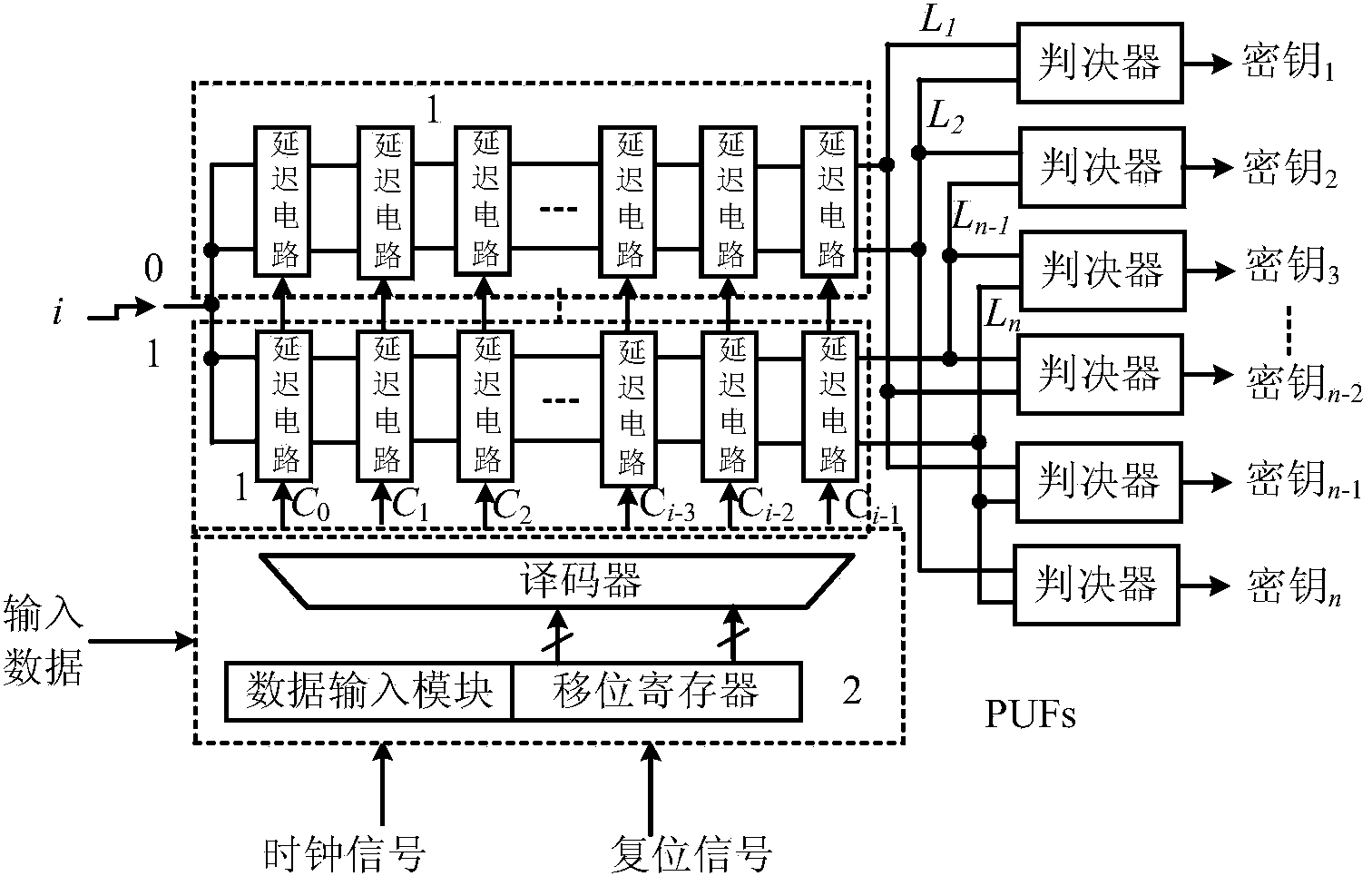

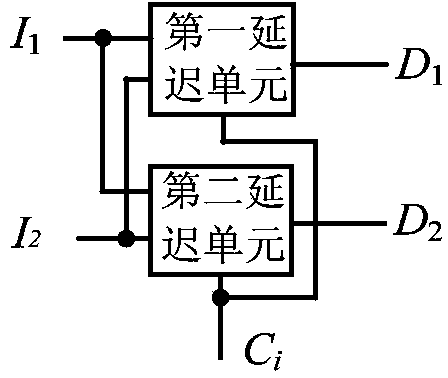

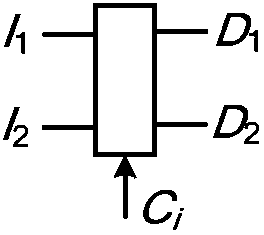

[0035] Embodiment one: if figure 1 As shown, a PUFs circuit based on delay chain multiplexing includes n transmission delay circuits 1 and a controller 2 that generates n control signals for controlling the transmission delay circuits. Two completely symmetrical The signal transmission delay path of n transmission delay circuits has 2n signal transmission delay paths, and the signal output end of each signal transmission delay path outputs a delay signal, and the PUFs circuit also includes A decision device, every two different signal output terminals in the signal output terminals of the 2n signal transmission delay paths are combined into a group of delayed signal output terminals, and the combination is obtained group delay signal output, group delay signal output with The signal input ends of each decision device are connected one by one, and each group of delayed signal output ports outputs a group of delayed signals to a corresponding decision device to generate a ...

Embodiment 2

[0046] Embodiment two: if figure 1 As shown, a PUFs circuit based on delay chain multiplexing includes n transmission delay circuits and a controller that generates n control signals for controlling the transmission delay circuits. Two completely symmetrical signal transmissions are set in the transmission delay circuits Delay path, n transmission delay circuits have 2n signal transmission delay paths, and the signal output end of each signal transmission delay path outputs a delay signal, and the PUFs circuit also includes A decision device, every two different signal output terminals in the signal output terminals of the 2n signal transmission delay paths are combined into a group of delayed signal output terminals, and the combination is obtained group delay signal output, group delay signal output with The signal input ends of each decision device are connected one by one, and each group of delayed signal output ports outputs a group of delayed signals to a correspon...

Embodiment 3

[0054] Embodiment three: as figure 1 As shown, a PUFs circuit based on delay chain multiplexing includes n transmission delay circuits and a controller that generates n control signals for controlling the transmission delay circuits. Two completely symmetrical signal transmissions are set in the transmission delay circuits Delay path, n transmission delay circuits have 2n signal transmission delay paths, and the signal output end of each signal transmission delay path outputs a delay signal, and the PUFs circuit also includes A decision device, every two different signal output terminals in the signal output terminals of the 2n signal transmission delay paths are combined into a group of delayed signal output terminals, and the combination is obtained group delay signal output, group delay signal output with The signal input ends of each decision device are connected one by one, and each group of delayed signal output ports outputs a group of delayed signals to a corresp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More