Design method of cache coherence protocol for multi-core and multi-processor platform

A multi-processor and design method technology, applied in the fields of electrical digital data processing, instruments, calculations, etc., can solve the problems of reducing protocol performance and increasing system communication burden, so as to improve synchronization efficiency, reduce message synchronization delay, and simplify processing Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be further described in detail below in conjunction with the accompanying drawings.

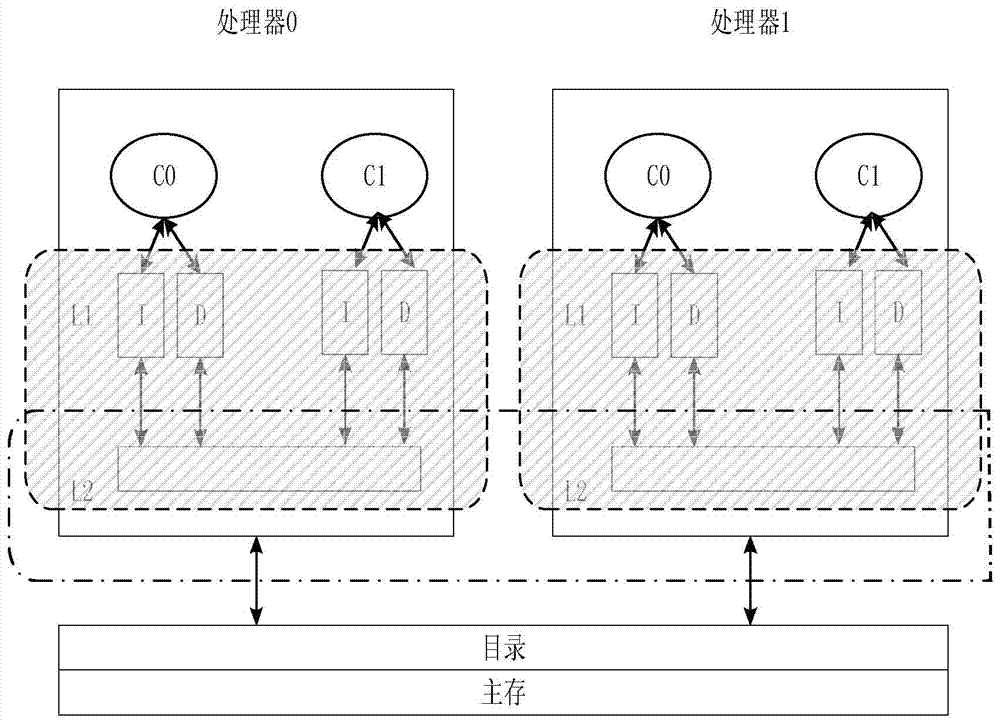

[0019] Depending on the implementation, the processor can be implemented using a bus-snooping-based or directory-based Cache coherence protocol. The description of the embodiments of the present invention takes bus monitoring as an example to describe, and the directory is used to record shared information between processors.

[0020] In this embodiment, with figure 1 The shown multi-core multi-processor structure is used as an example to illustrate the synchronization process of Cache lines in the S and SS states and the mutual conversion between the SS and S shared states. For concise and accurate description, use (processor number, processing core number) to represent a processor core. For example, (0,1) indicates the processor core numbered 1 of processor 0, (1,0) indicates the processor core numbered 0 of processor 1, and so on. dL1 represents the pri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More