Patents

Literature

162results about How to "Does not affect the design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

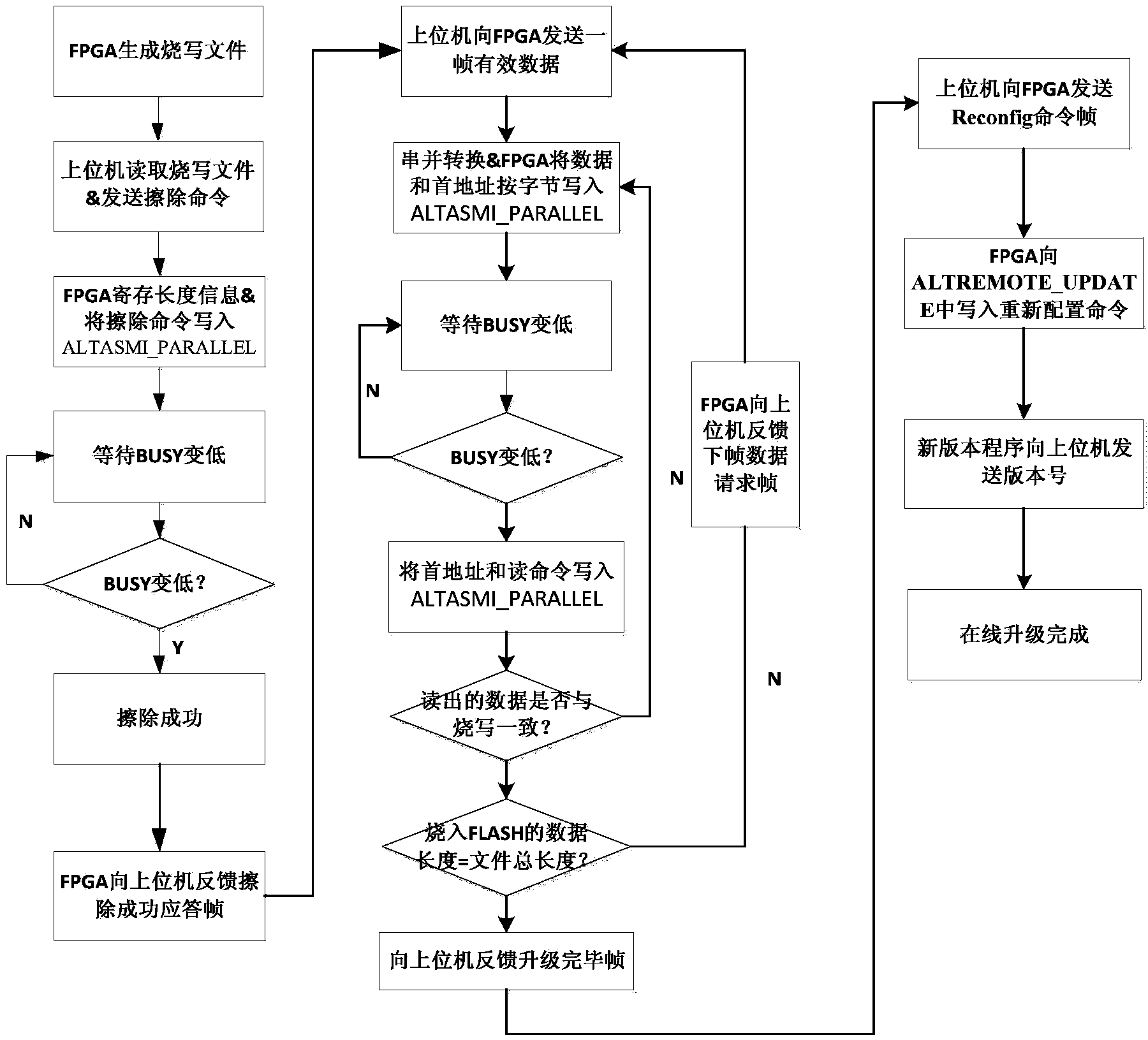

FLASH memorizer long-distance on-line upgrade method based on field programmable gate array (FPGA)

InactiveCN103136028ADoes not affect the designImprove robustnessProgram loading/initiatingUpgradeDigital signal processing

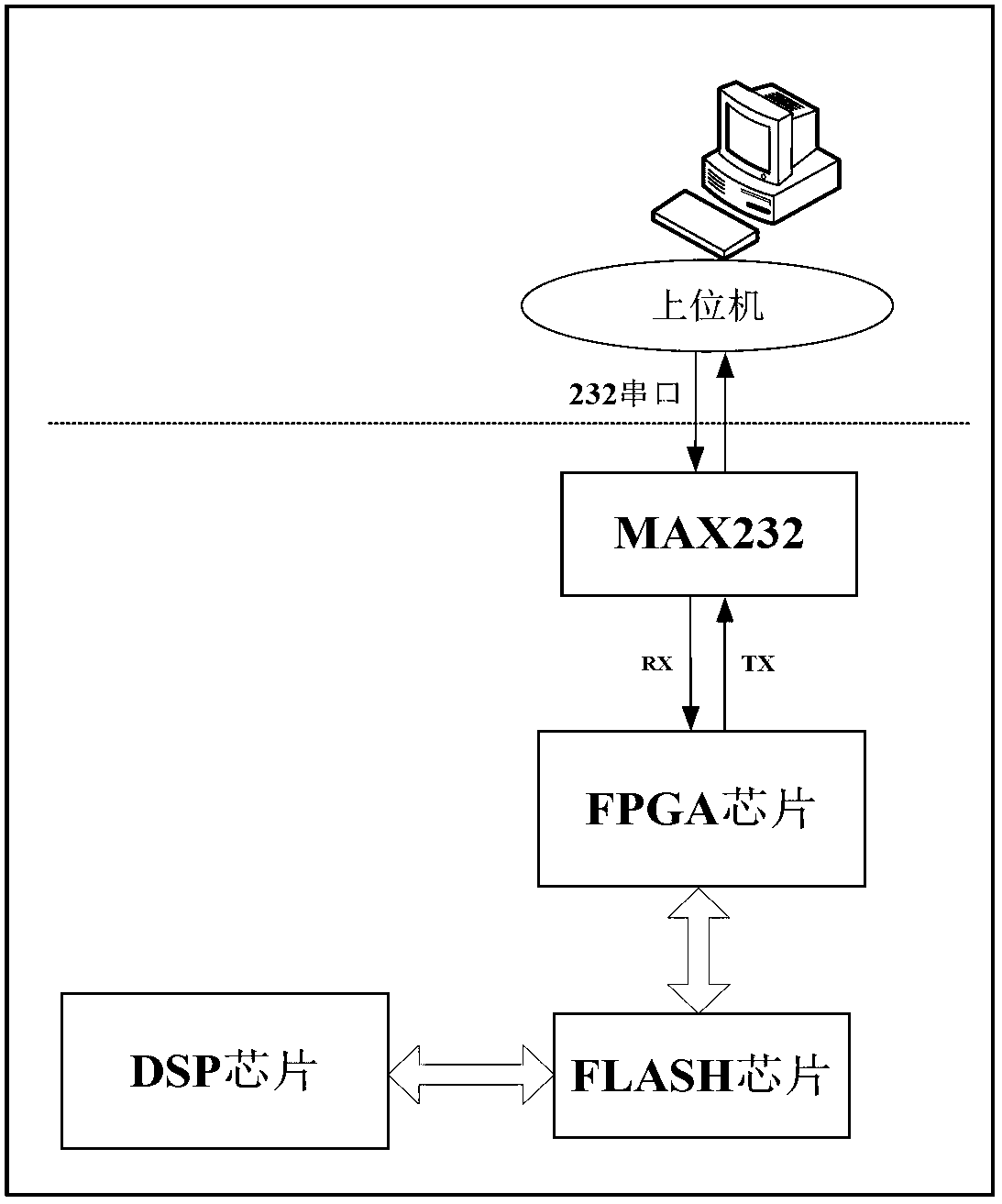

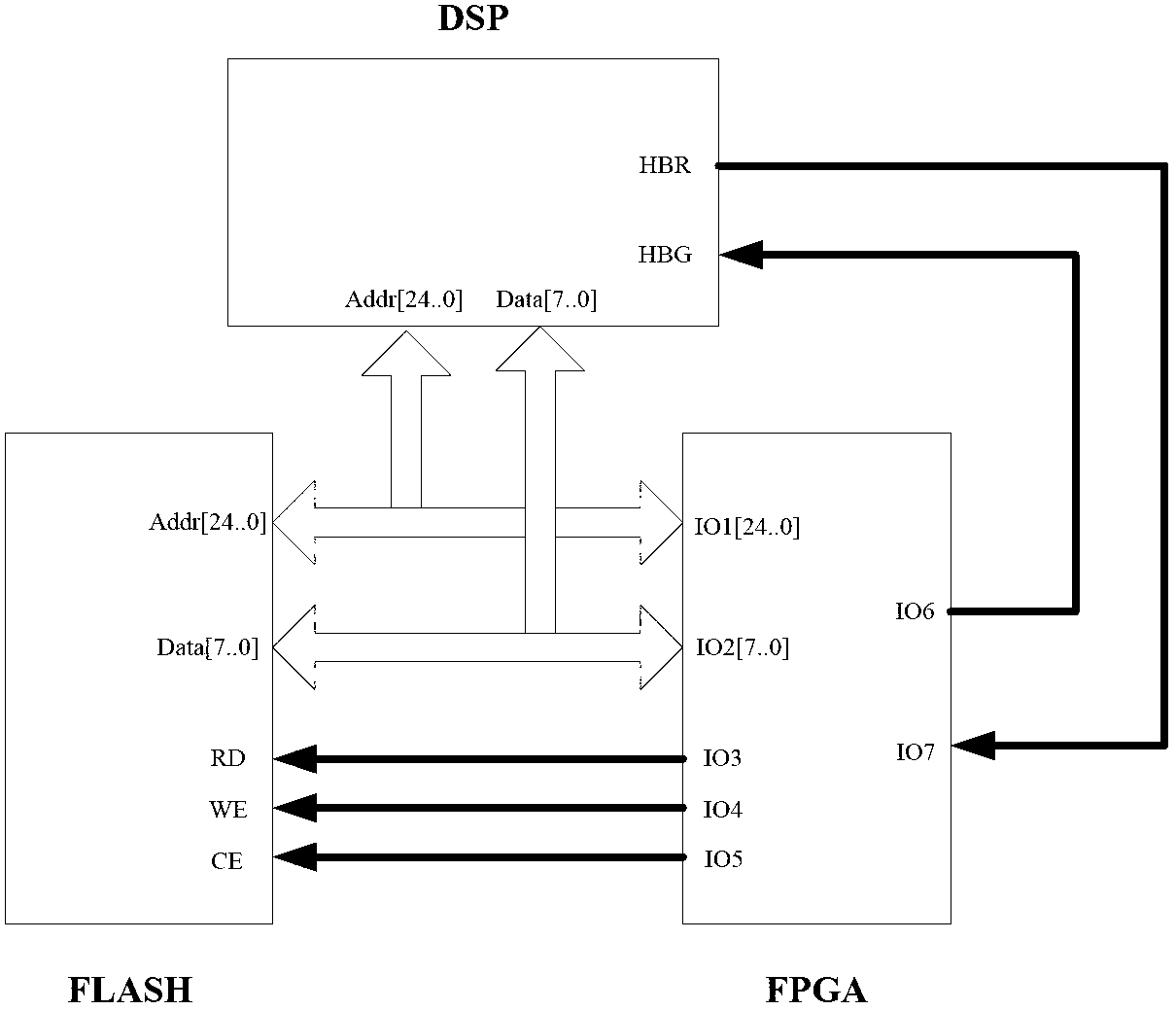

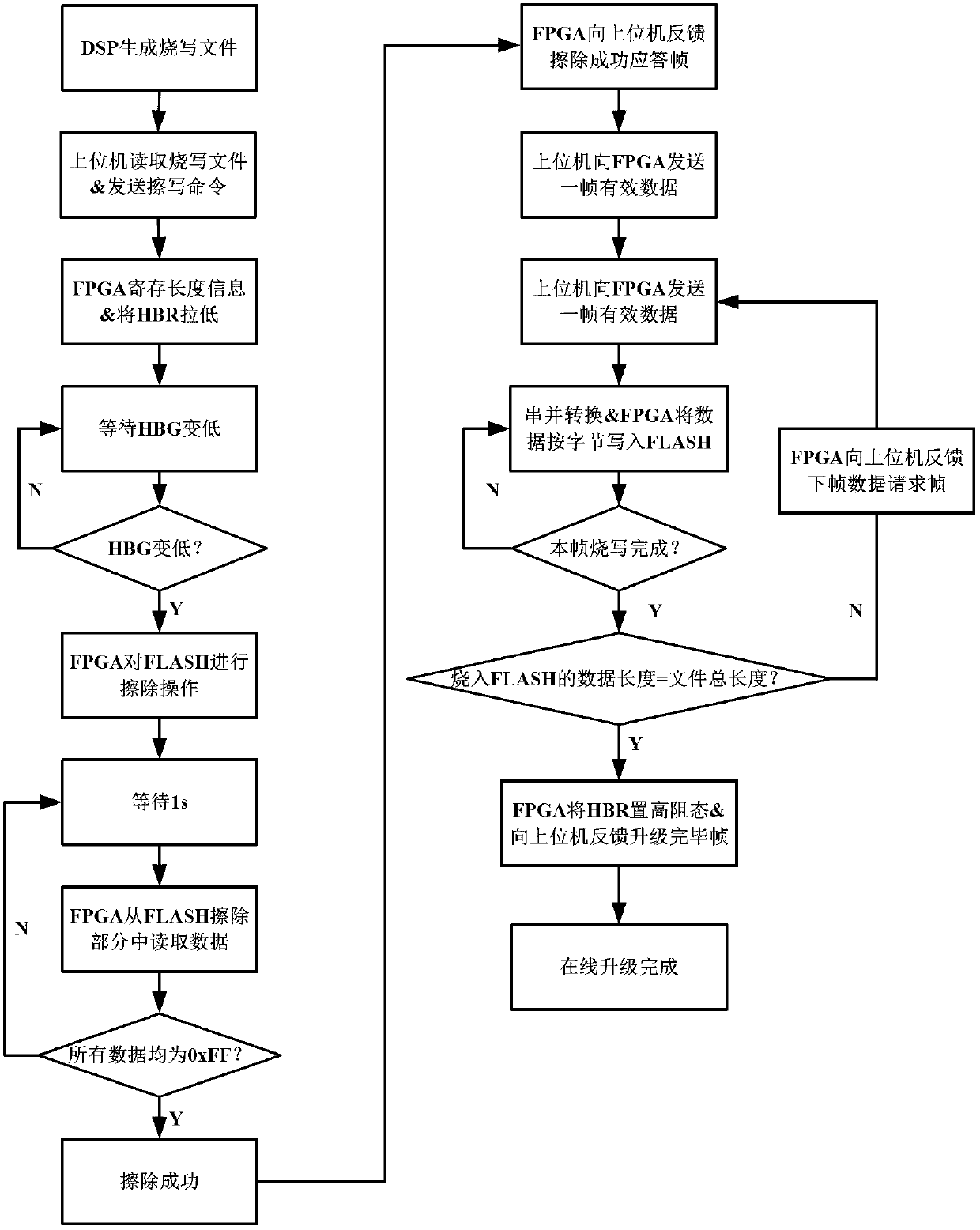

The invention provides a FLASH memorizer long-distance on-line upgrade method based on a field programmable gate array (FPGA). The FPGA serves as a main control chip and is used for receiving a command frame sent by an upper computer, feeding a response frame back to the upper computer and carrying out erasure and programming operation on a FLASH memorizer. The FPGA is used for receiving the command frame sent by the upper computer through a protocol of a serial port and judging that the command frame is a FLASH erasing command or a FLASH data frame through a zone bit of the command frame, wherein the FLASH erasing command comprises digital signal processing (DSP) programming file total length information, and the FLASH data frame comprises concrete contents of the DSP programming file. According to the FLASH memorizer long-distance on-line upgrade method based on the FPGA, the long-distance on-line upgrade of the FLASH memorizer can be achieved without dismounting the whole system, a long-distance on-line upgrade module is not affected, and vigorousness of the system is increased.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

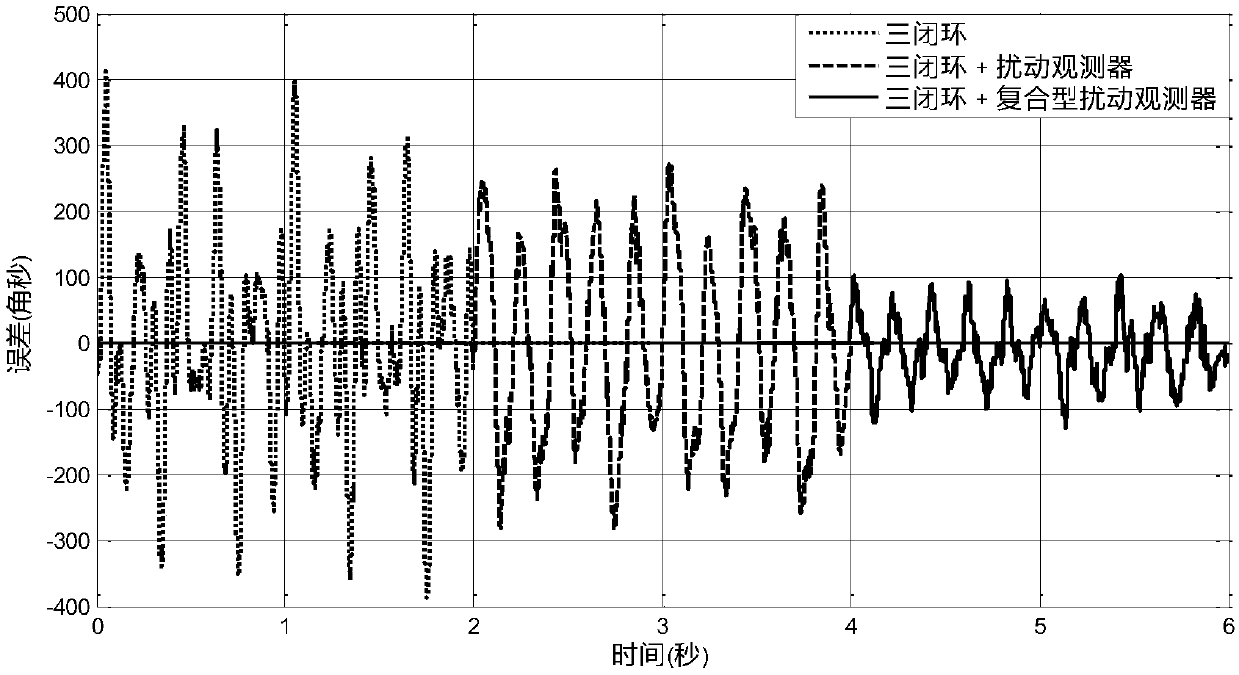

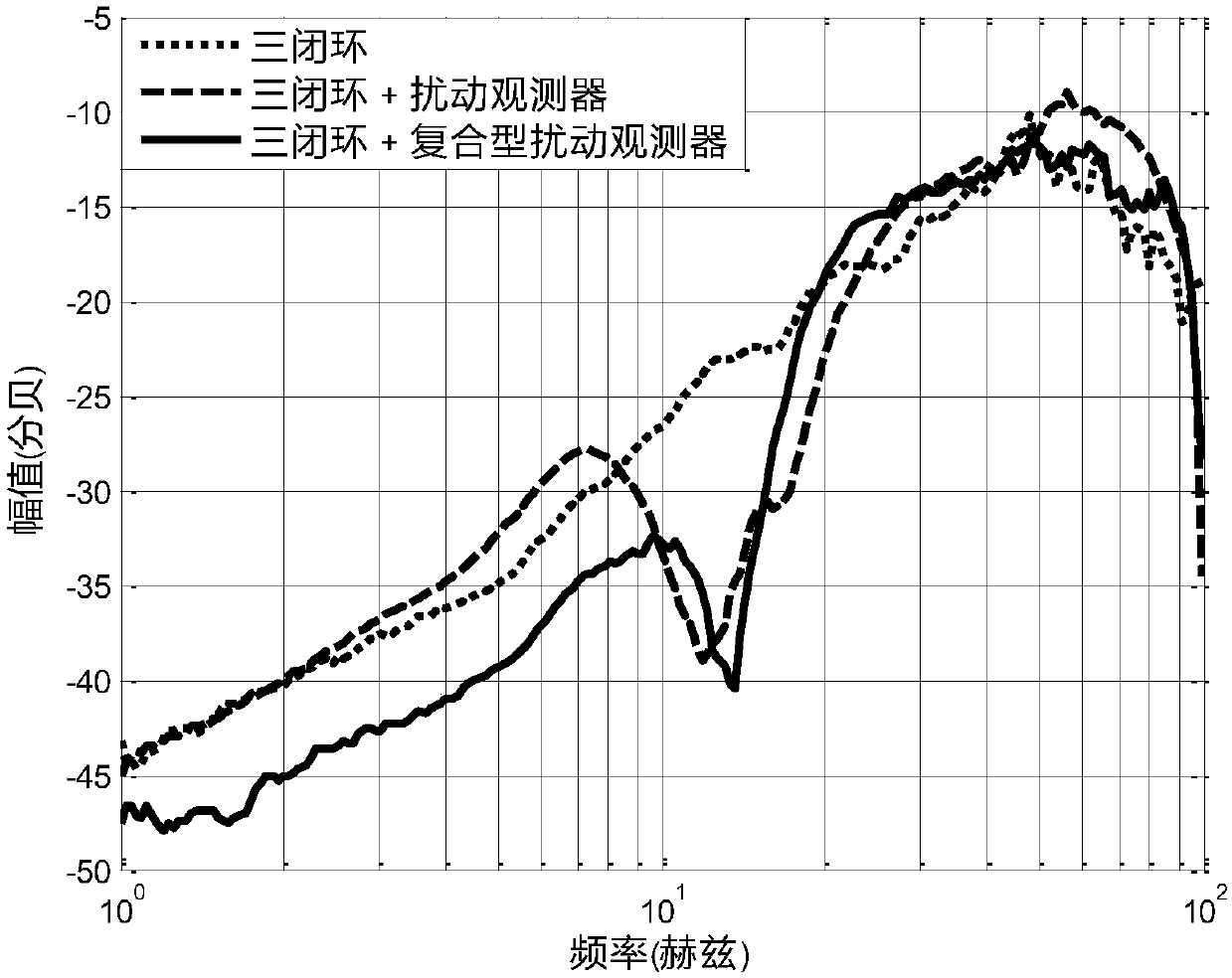

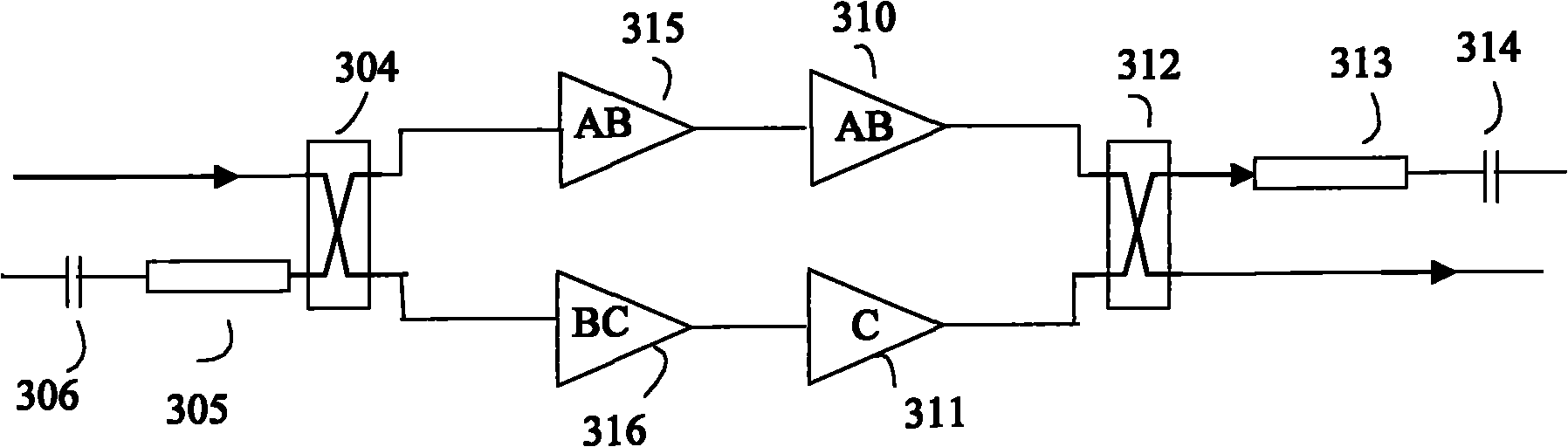

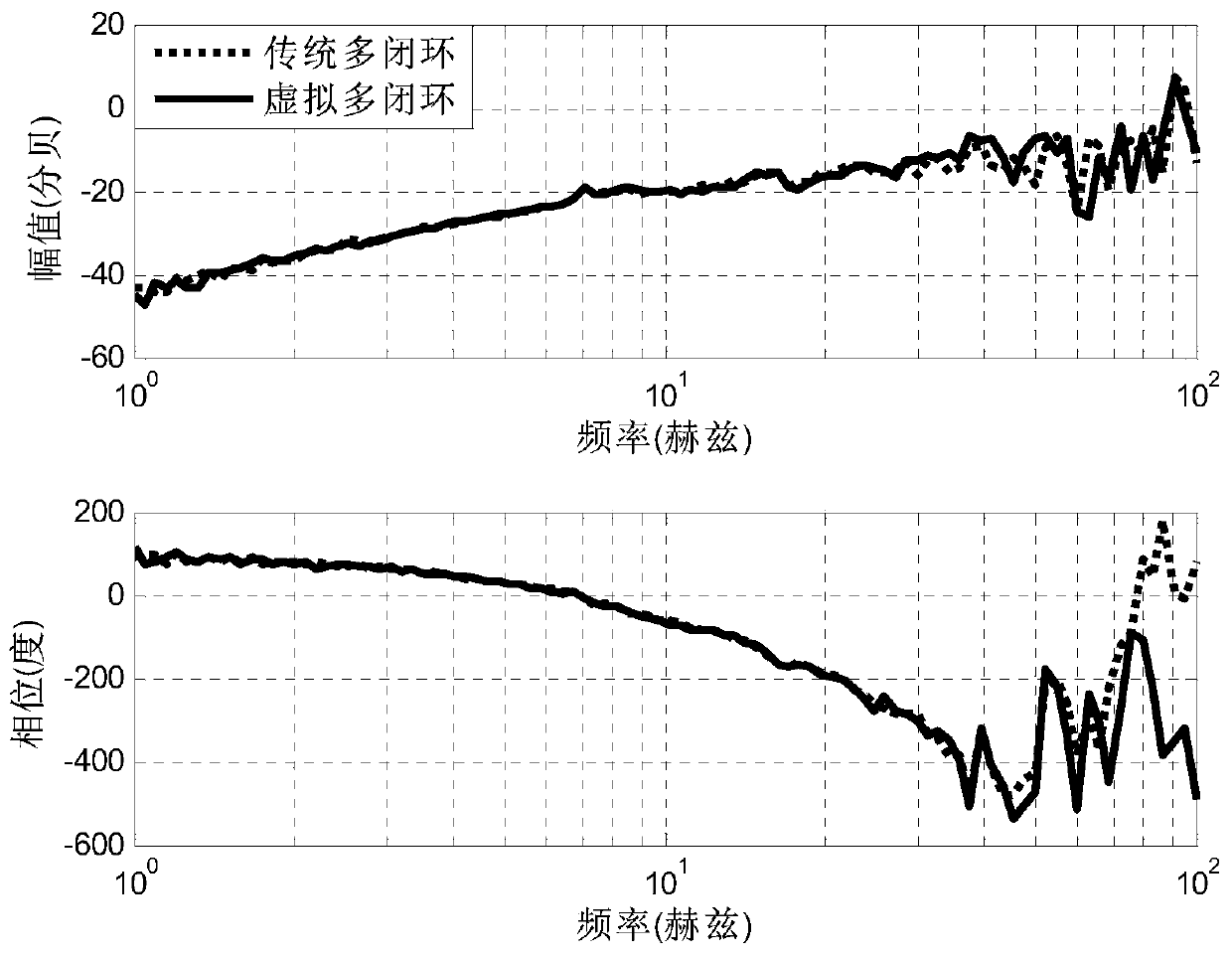

Disturbance suppression method based on compound disturbance observer

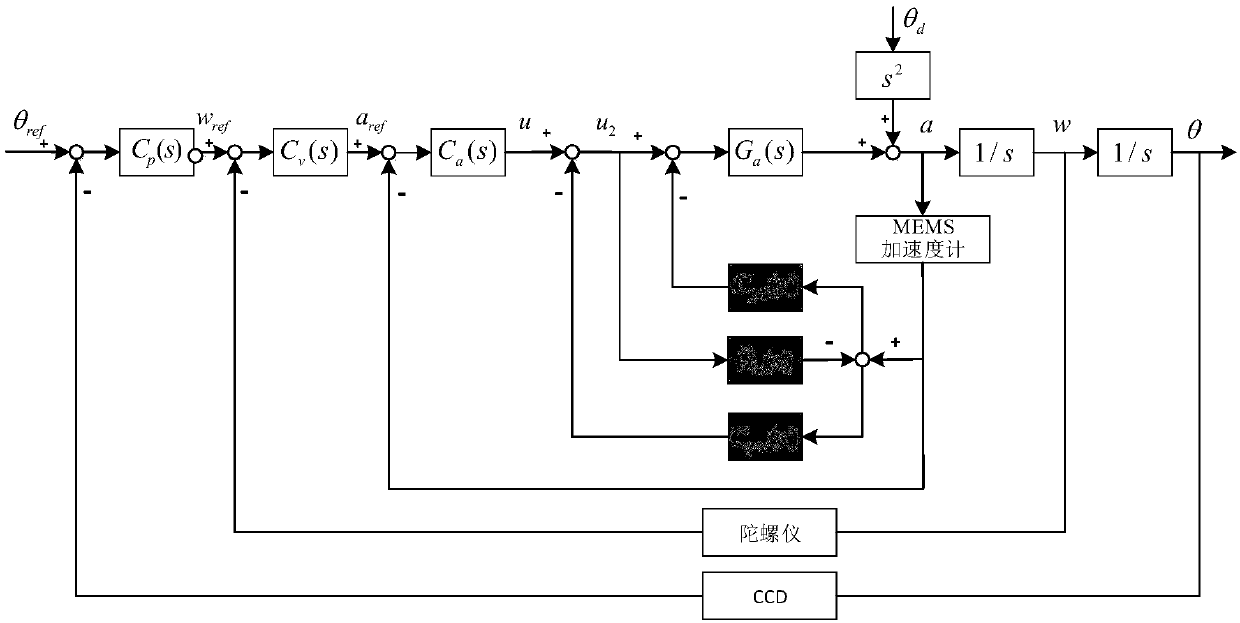

The invention discloses a disturbance suppression method based on a compound disturbance observer, and aims at the problem that system requirements can not be stably controlled at high accuracy sincethe low-frequency and middle-frequency disturbance suppression capability of a control system stable platform is poor. By use of the method, on the basis of multi-closed-loop control, a traditional disturbance observer design is improved, the compound disturbance observer structure is put forward, and a design method for an inner and outer ring feedforward compensation controller in the compound disturbance observer is given. By use of the method, an outer ring in the compound disturbance observer is utilized for estimation, inverse feedforward of a middle-frequency band and external disturbance, and an inner ring is used for estimation, inverse feedforward of a low-frequency band and external disturbance. The inner ring and the outer ring of the compound disturbance observer simultaneously act, finally, the purposes of simultaneously improving the disturbance suppression capability of the low frequency band and the middle-frequency band of the system and improving and controlling system stability accuracy are achieved.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

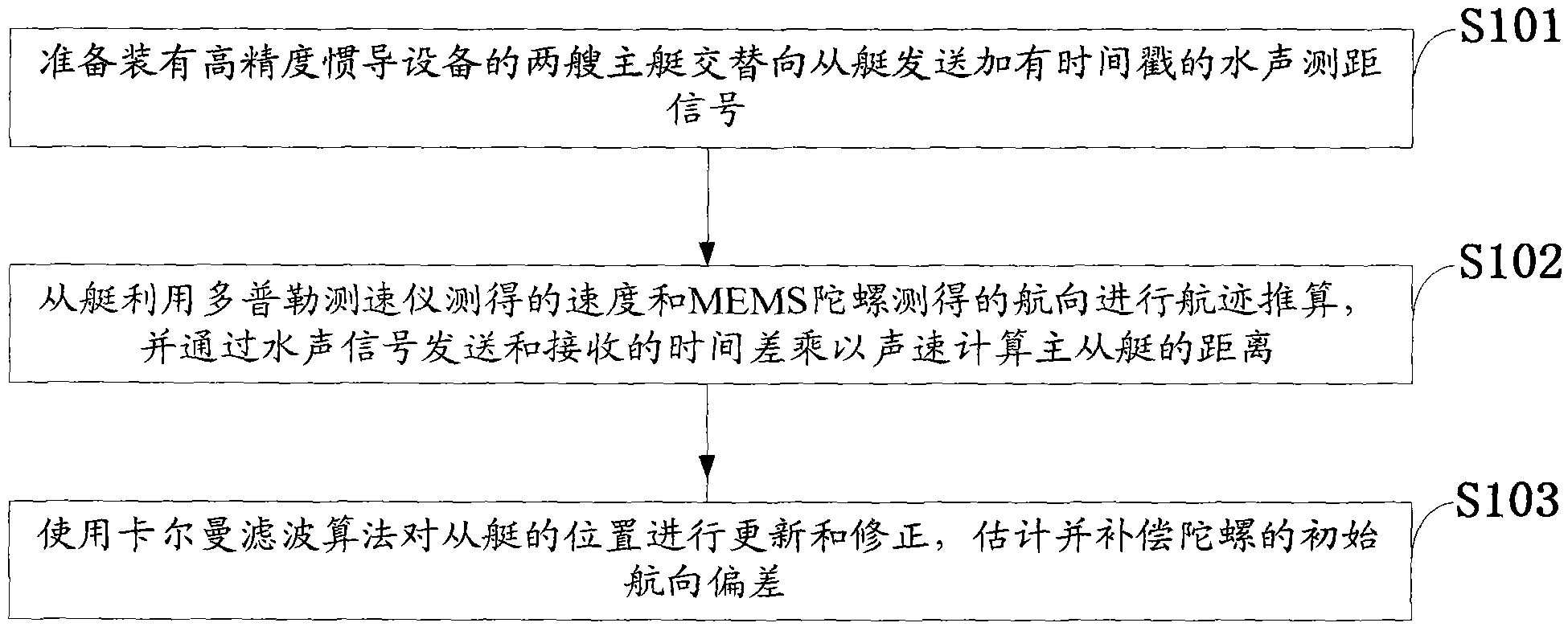

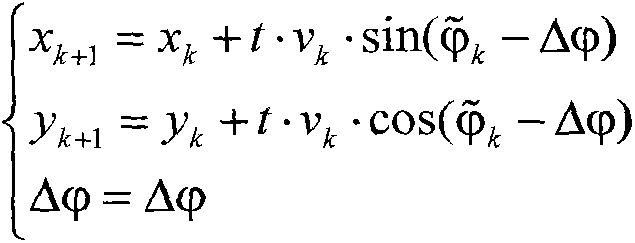

Method for estimating initial heading deviation filtering

InactiveCN103712625ADoes not affect the designImprove scalabilityNavigational calculation instrumentsGyroscopeTime difference

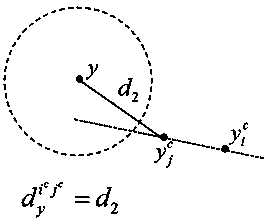

The invention discloses a method for estimating the initial heading deviation filtering. The method for estimating the initial heading deviation filtering comprises the following steps: preparing two main boats equipped with high-precision inertial navigation equipment to send subaqueous sound ranging signals with time stamps to a slave boat alternatively; carrying out dead reckoning by the slave boat by utilizing the speed measured by a Doppler velocimeter and the heading measured by an MEMS (Micro-electromechanical Systems) gyroscope, and calculating the distance between each main boat and the slave boat by multiplying the time difference of sending and receiving submarine sound signals and the sound velocity; updating and amending the position of the slave boat by using Kalman filter algorithm, estimating and compensating the initial heading deviation of the gyroscope. According to the method, through the radio broadcasting positional information of the main boat, the slave boat passively receives radio signals transmitted by the main boat, so that the expansibility is improved, and the condition of multiple slave boats can be simulated by using two main boats and one slave boat; the slave boat is provided with low-precision inertial navigation equipment for pushing, and the high-precision inertial navigation equipment of the main boat is utilized by measuring the distance between the slave boat and each main boat, thus the positioning precision is improved, and the equipment cost is greatly reduced.

Owner:HARBIN ENG UNIV

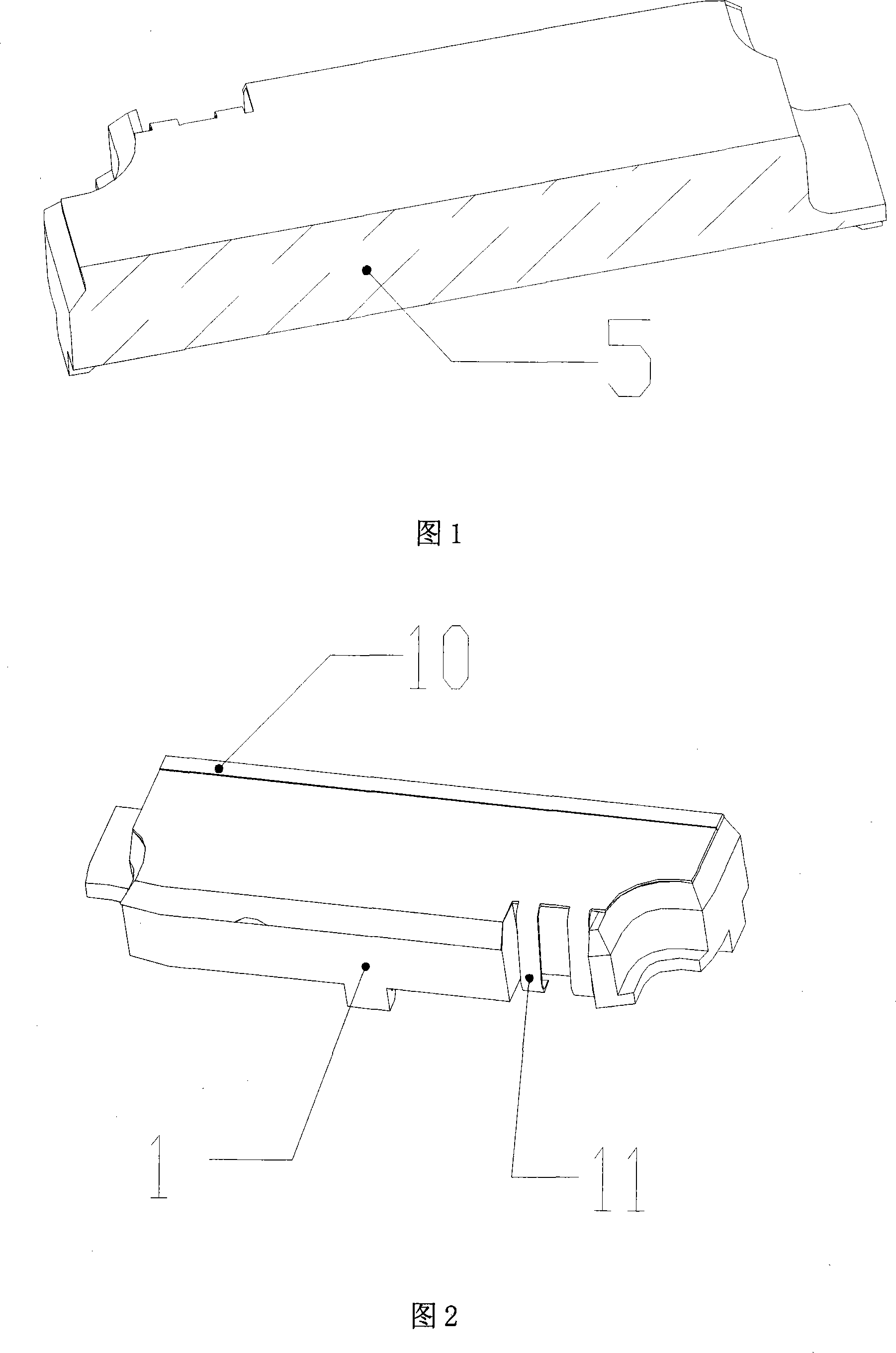

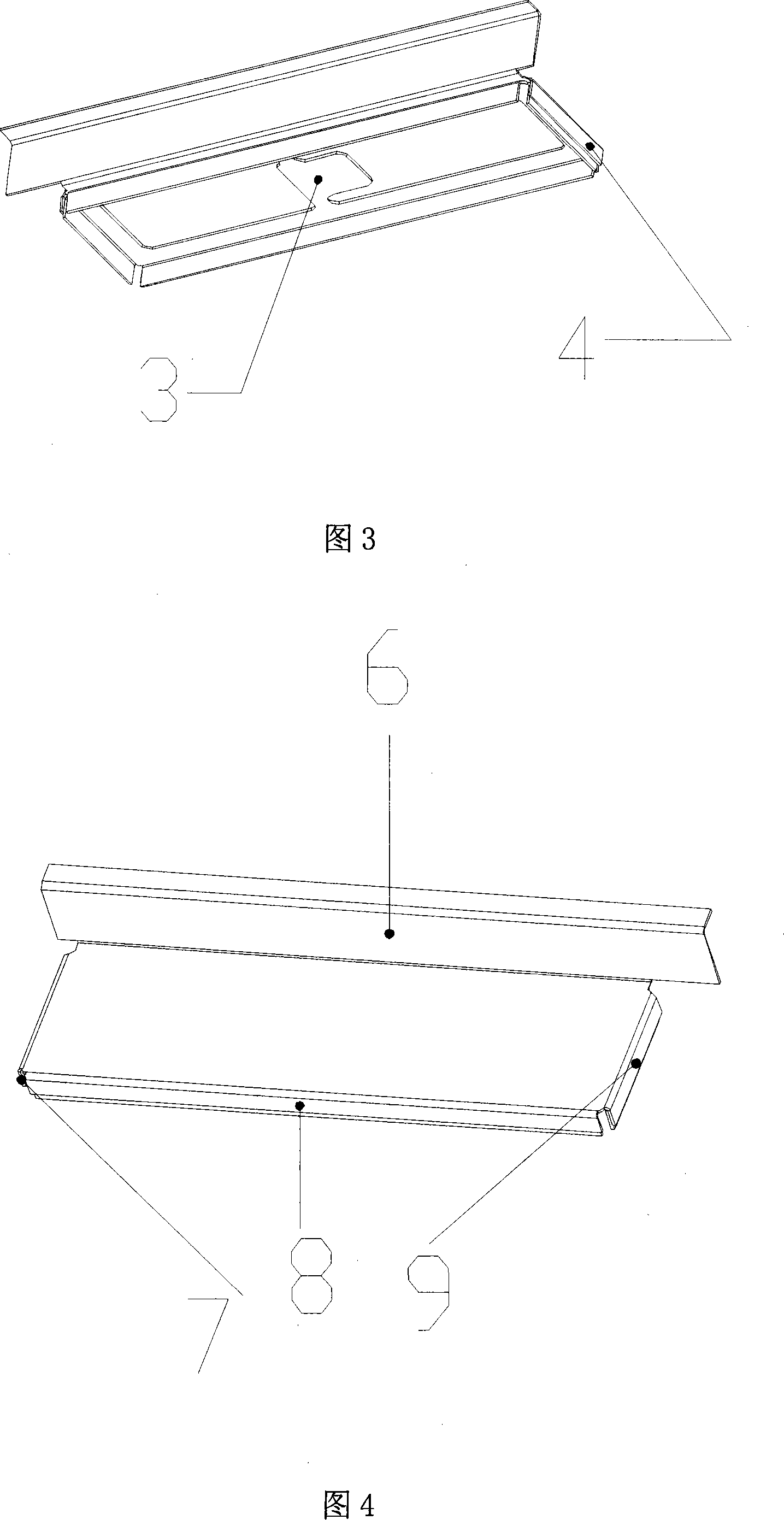

Tool for rotary cutting machining

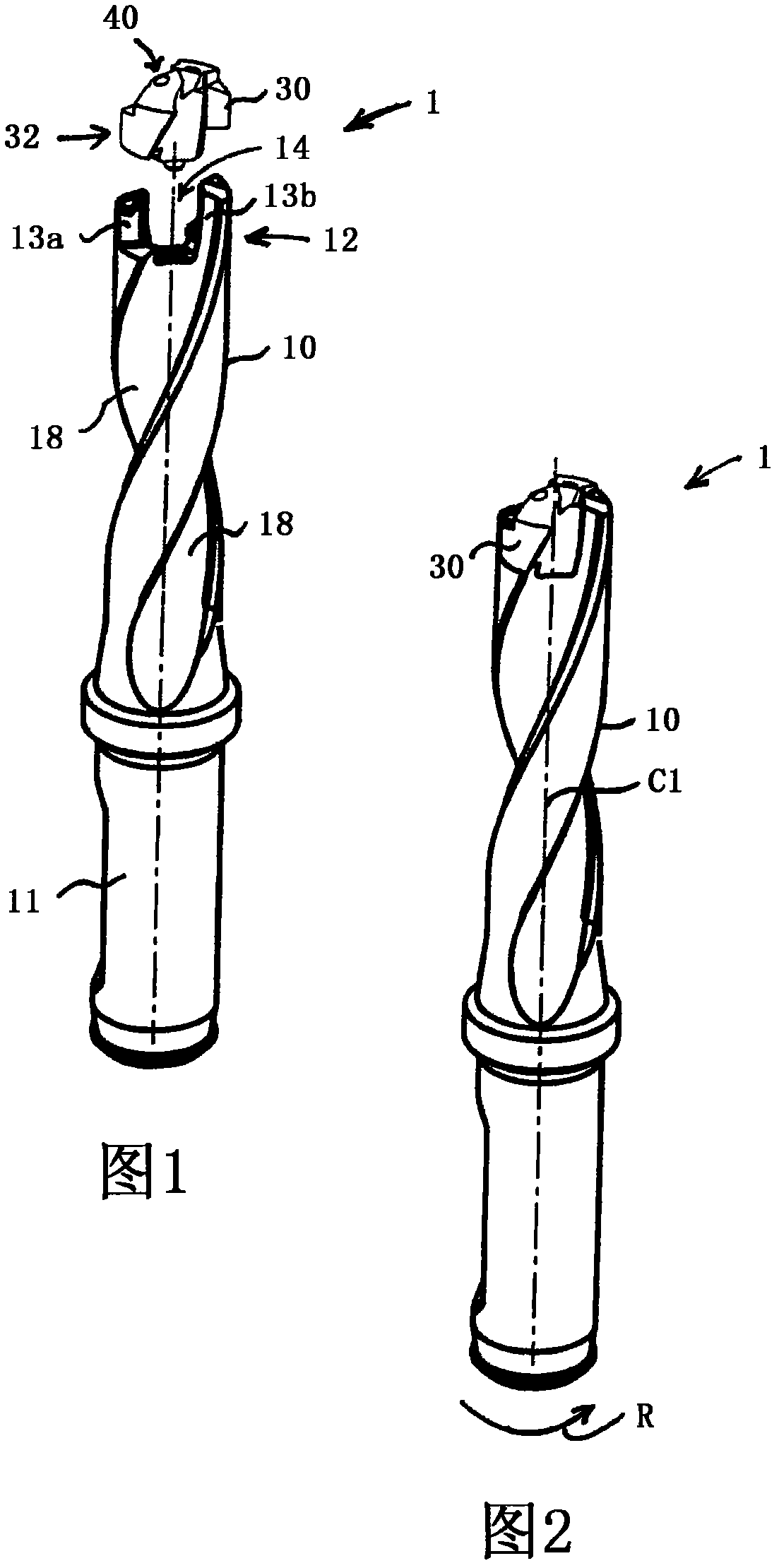

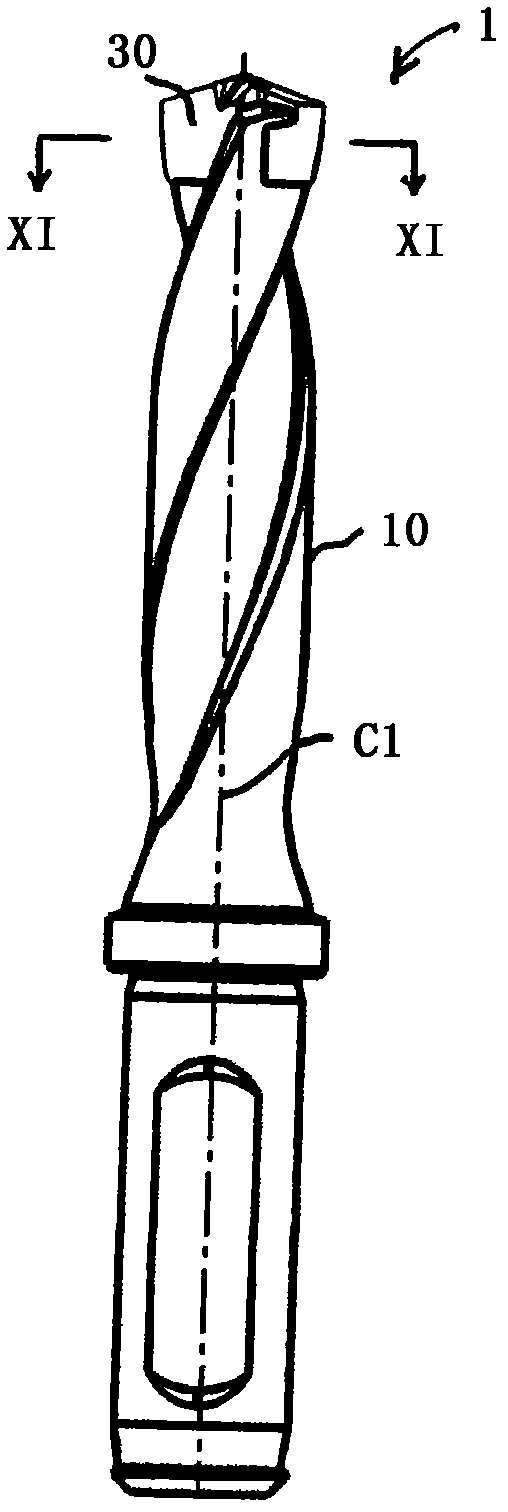

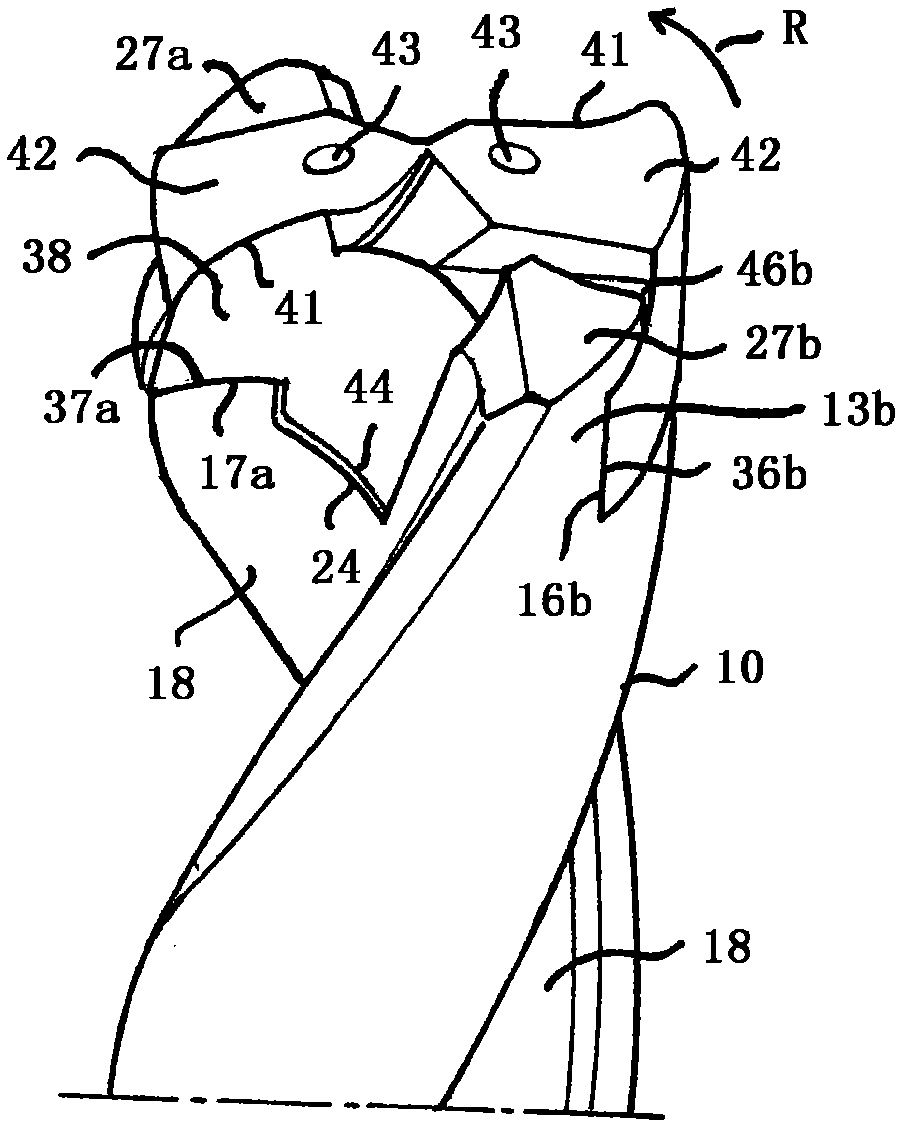

InactiveCN102006958AAxial locking is achievedSimple and optimal shapeMilling cuttersCutting insertsCouplingAbutment

The invention relates to a tool for rotary cutting machining, comprising a tool body (10) and a replaceable cutting head (30) de- tachably attachable to the tool body. At its front end, the tool body is provided with two coupling legs (13a, 13b) projecting in axial direction. The respective coupling leg is provided with a stop surface (16a, 16b) for transferring torque from the tool body to the cutting head, which stop surface is designed for abutment against a corresponding stop surface (36a, 36b) of the cutting head. The respective coupling leg is provided with a shoulder (26a, 26b) protruding from the stop surface of the coupling leg. The cutting head is provided with two shoulders (46a, 46b) facing the front end of the cutting head and arranged on opposite sides of the centre axis of the cutting head, which shoulders border on a respective one of said stop surfaces of the cutting head and are arranged to extend in under a respective one of said shoulders of the coupling legs of the tool body when the cutting head is attached to the tool body, so as to thereby prevent the cutting head from being displaced in axial direction away from the tool body. The invention also relates to a tool body and a cutting head included in such a tool.

Owner:SECO TOOLS AB

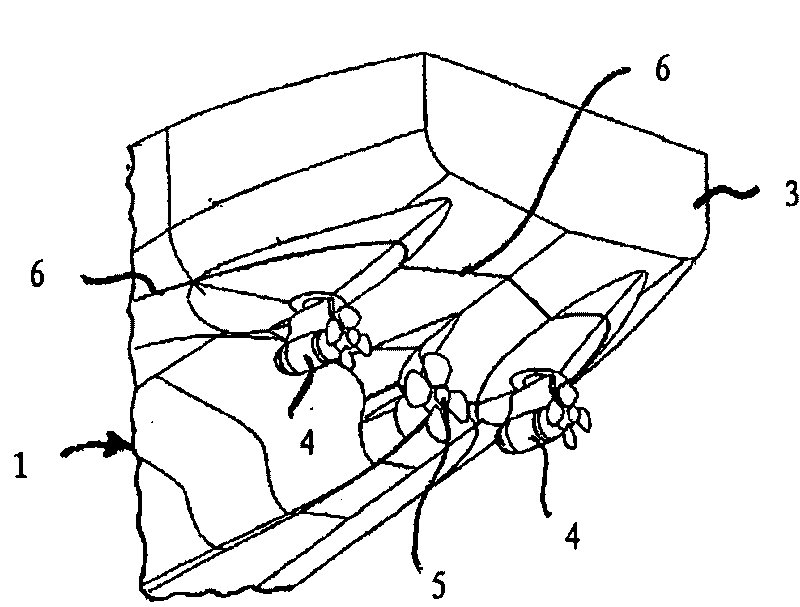

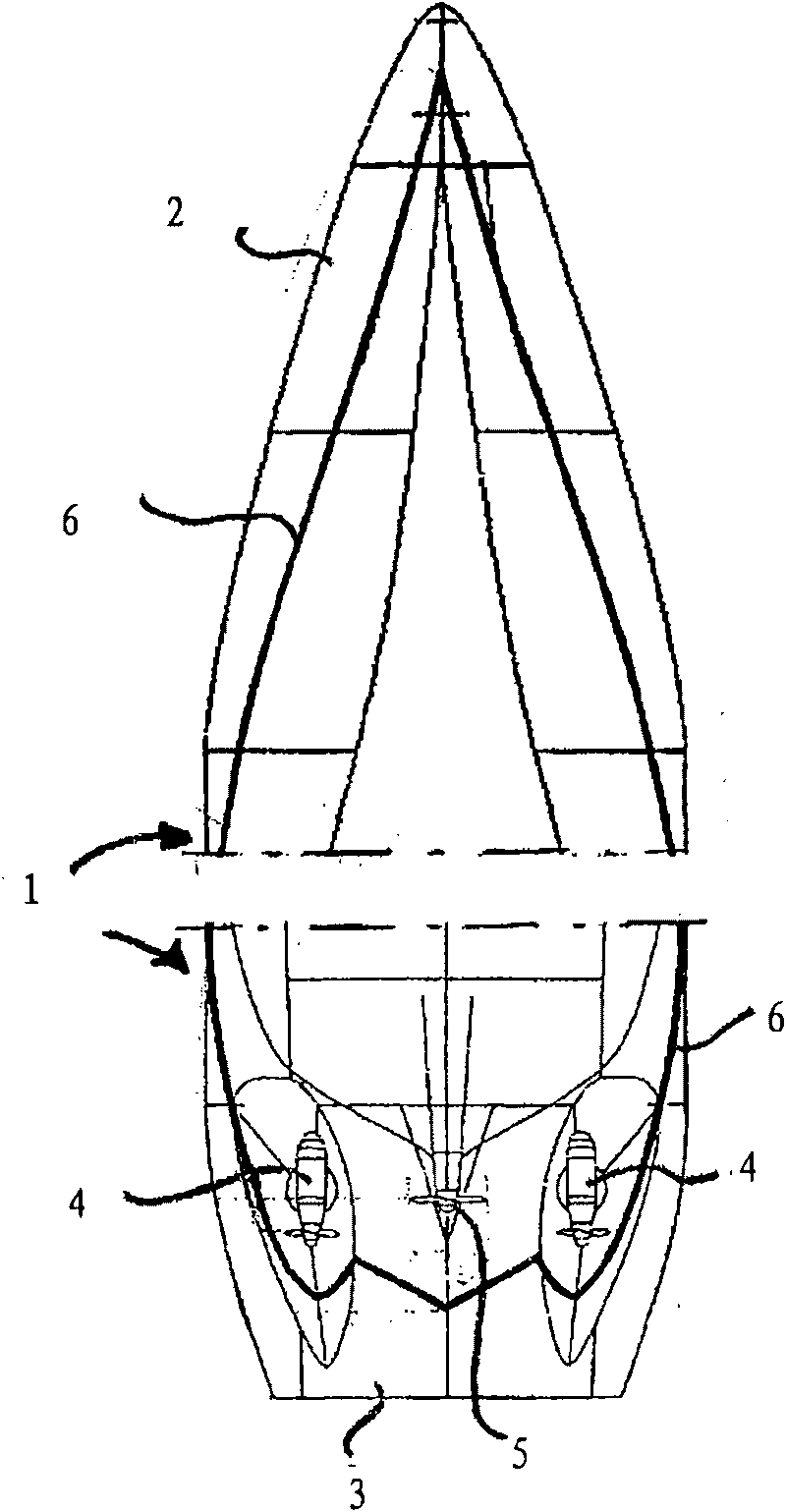

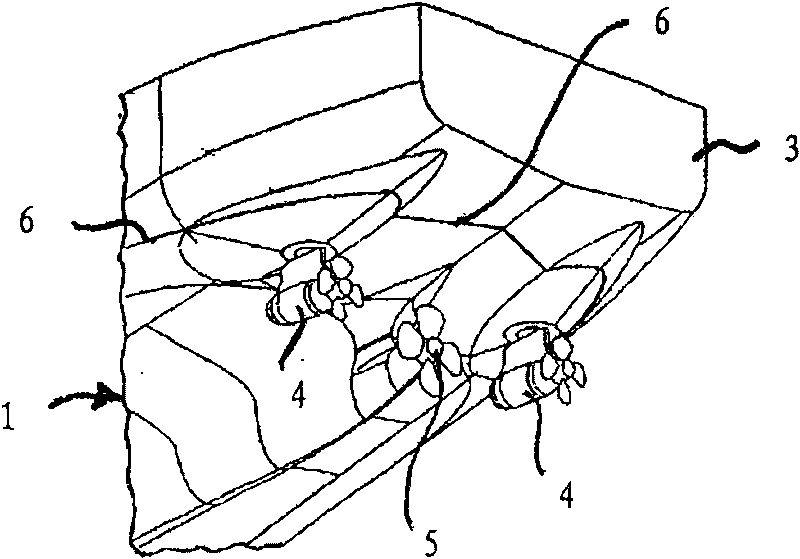

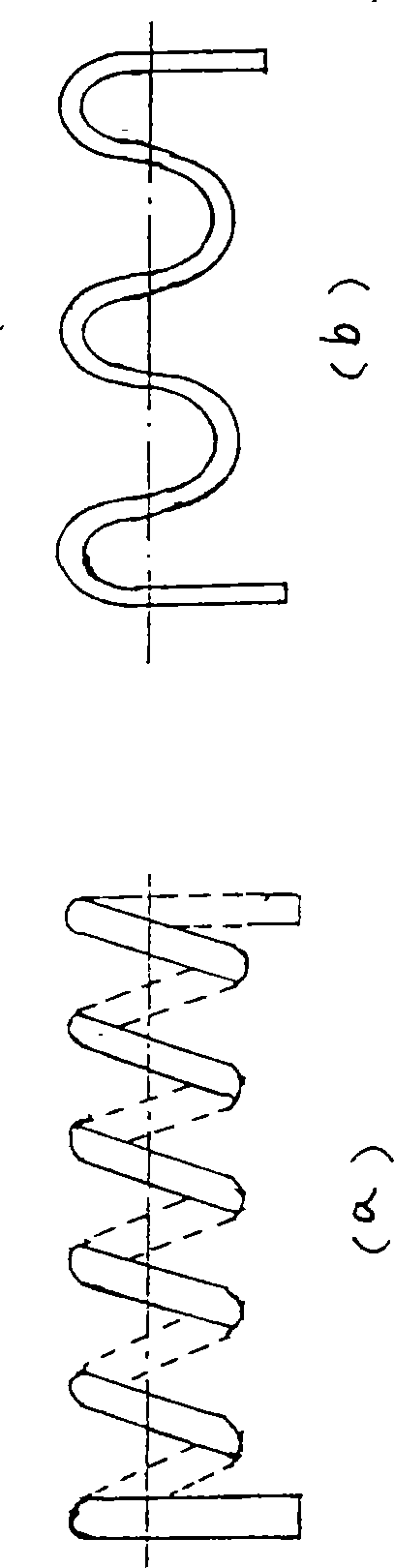

Method for improving the ice-breaking properties of a water craft and a water craft constructed according to the method

ActiveCN101730644AEasy to operateDoes not affect the designIce breakersPropulsive elementsPropellerWatercraft

A method of providing a watercraft, especially an icebreaker or a cargo ship, tanker or similar transport vessel, with improved ice penetration characteristics and a watercraft manufactured according to the method, which watercraft has a hull (1) with a first end (2) and a second end (3) and which is equipped at said second end with a propulsion arrangement, which provides the main propulsive thrust of the watercraft, while the watercraft moves with either end ahead, and the steering of the watercraft, whereby said second end (3) of the watercraft is shaped and designed so that it, as such, has efficient ice penetration characteristics. Said propulsion arrangement is chosen so as to include at least three propulsion devices, at least the majority of which are rudder propeller devices (4) and which are arranged at least at two different distances from said second end (3) of the watercraft so that when the watercraft moves in ice or ice build-ups said second end (3) ahead, the propeller with one or more propulsion devices located near said second end (3) of the watercraft is arranged to break ice and the propeller with one or more propulsion devices located farther away from said second end (3) of the watercraft is arranged to remove disintegrated ice or ice chunks away from the ice build-up.

Owner:AKER ARCTIC TECH

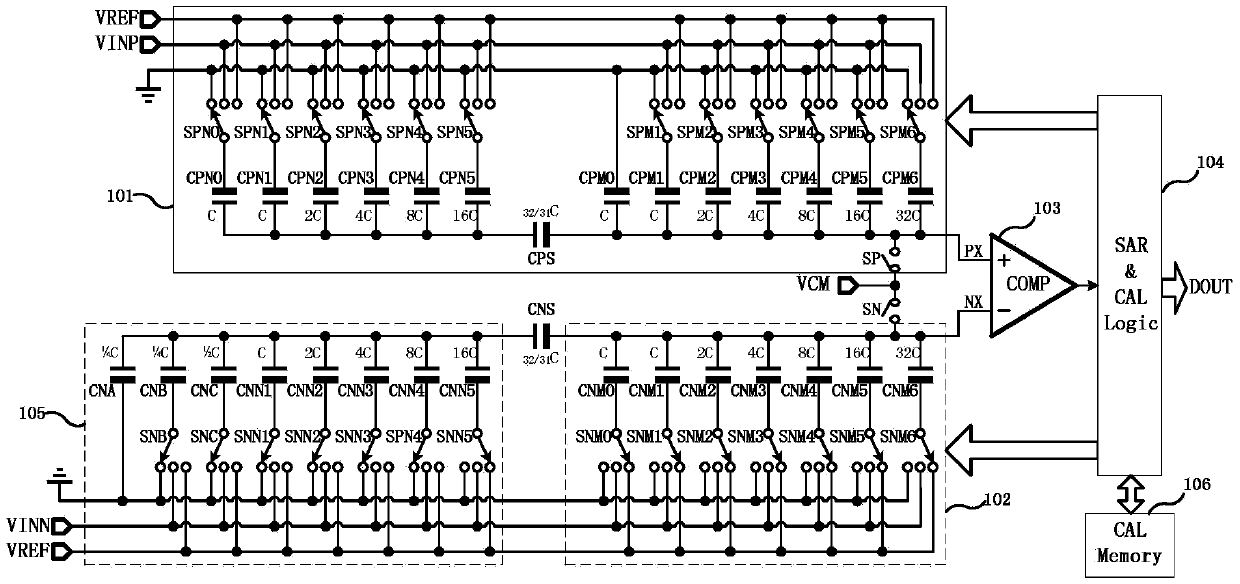

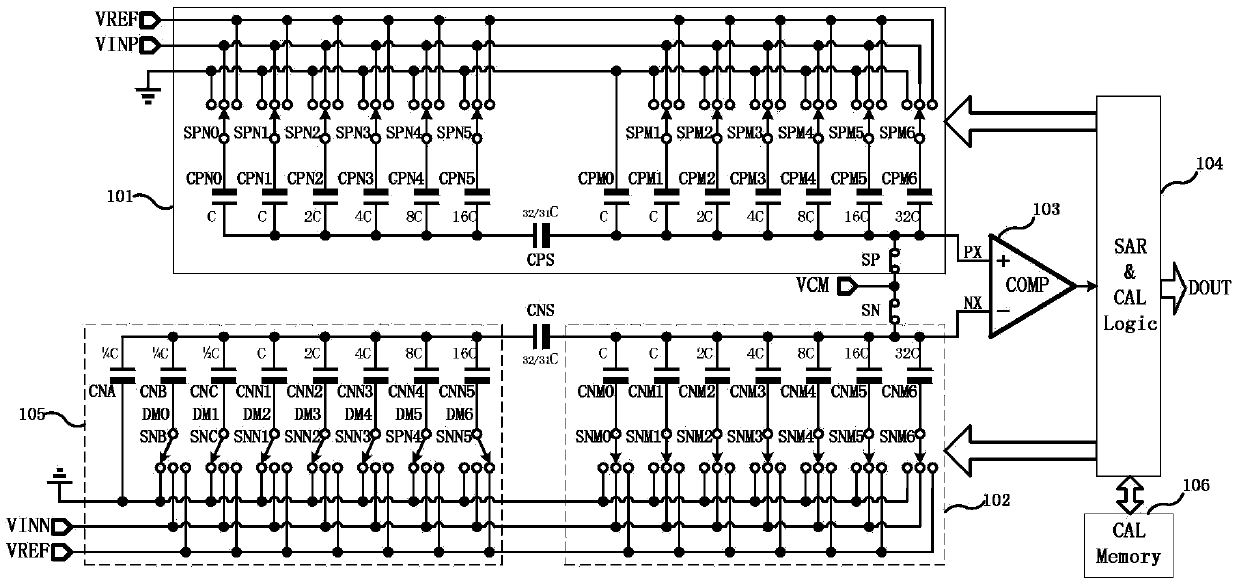

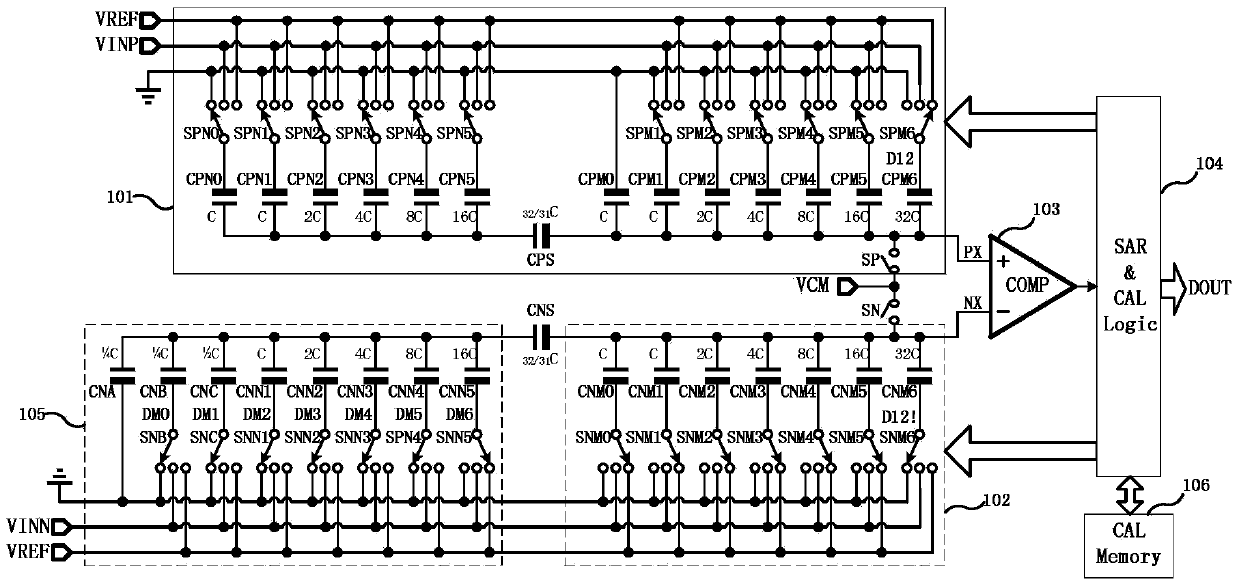

Digital self-calibration circuit and method of successive approximation analog to digital converter

ActiveCN105375923ALow latencyLower latencyAnalogue/digital conversion calibration/testingAnalog to digital conversionCapacitance

The invention discloses a digital self-calibration circuit of a successive approximation analog-to-digital converter. During analog-to-digital conversion, when carrying out kth bit analog-to-digital conversion, one control code is selected from two selectable control codes according to former bit data at first, and the selected control code is used for controlling a calibration capacitor array and calculating the kth bit data; and before outputting the kth bit data, when carrying out the kth bit analog-to-digital conversion, a logic circuit is controlled to calculate the two selectable control codes corresponding to the (k-1) th bit. The invention further discloses a digital self-calibration method of a successive approximation analog-to-digital converter. The digital self-calibration circuit and method disclosed by the invention can be used for improving the conversion efficiency and the conversion precision, reducing the number of adders and saving the circuit area.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

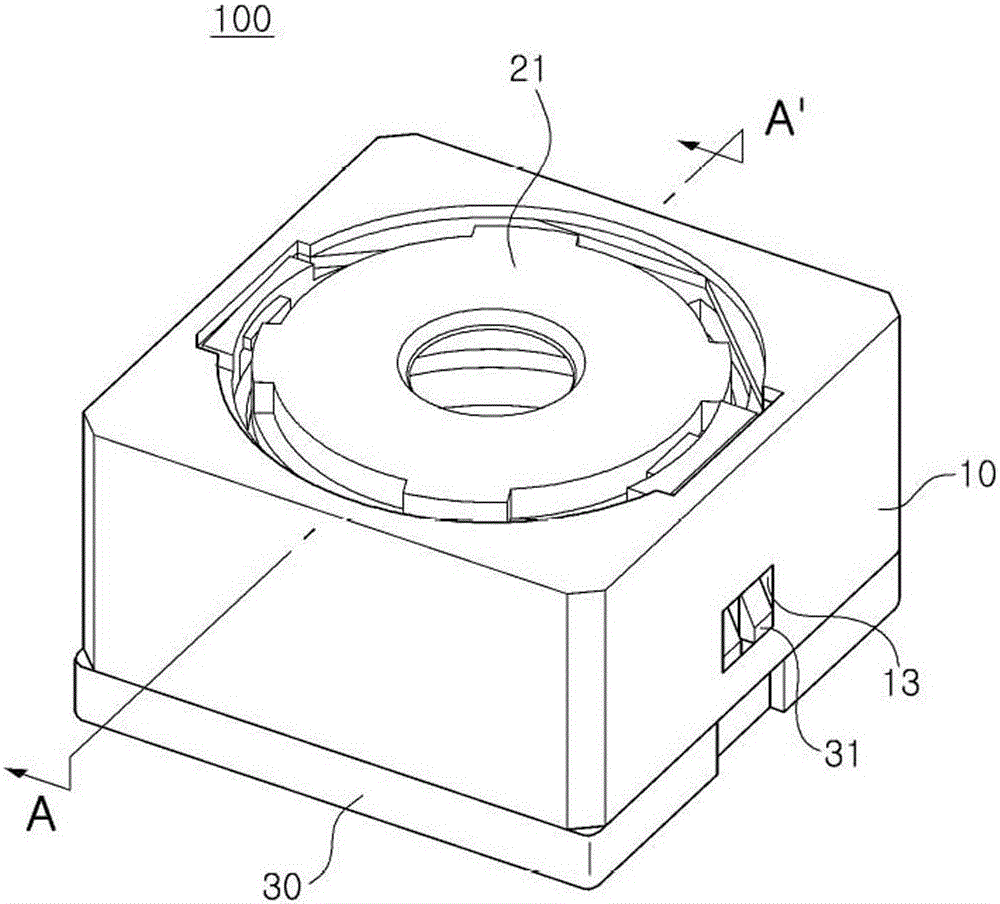

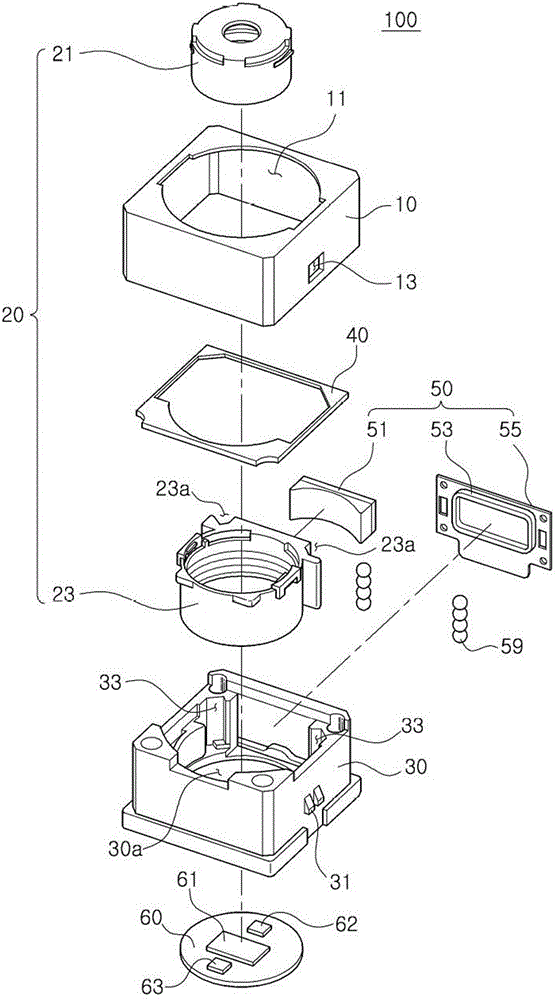

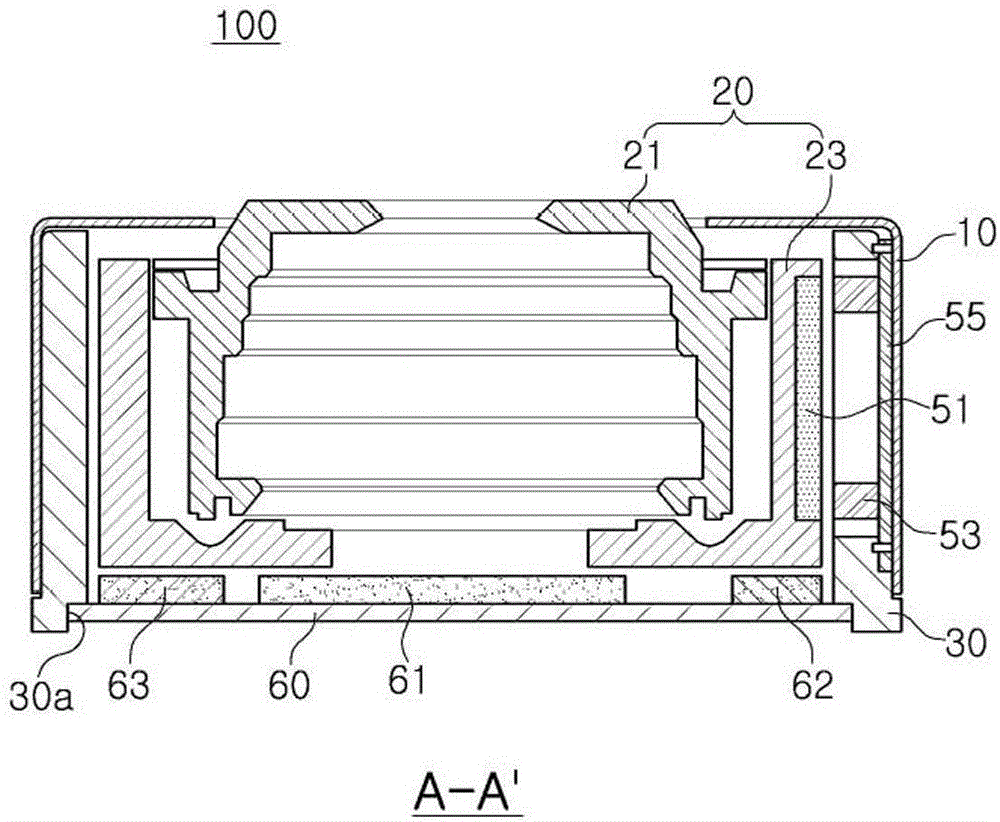

Camera module

InactiveCN106647107ADoes not affect the designSimple designMountingsFocusing aidsCamera lensOptical axis

The disclosure provides a camera module. The camera module includes a shell which accommodates a lens module capable of moving along an optical axis direction; a driving component which includes a magnet arranged in the lens module and a coil arranged in the shell; a substrate which is arranged on a surface of the shell vertical to the optical axis, includes a position sensor, acts with the magnet of the shell on the surface facing the optical axis direction of the lens module and senses the position of the lens module. According to the abovementioned structure, the position sensor does not influence the design of the driving component used for automatic focusing, unused space can be effectively utilized, and thus the design freedom of the camera module can be increased.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

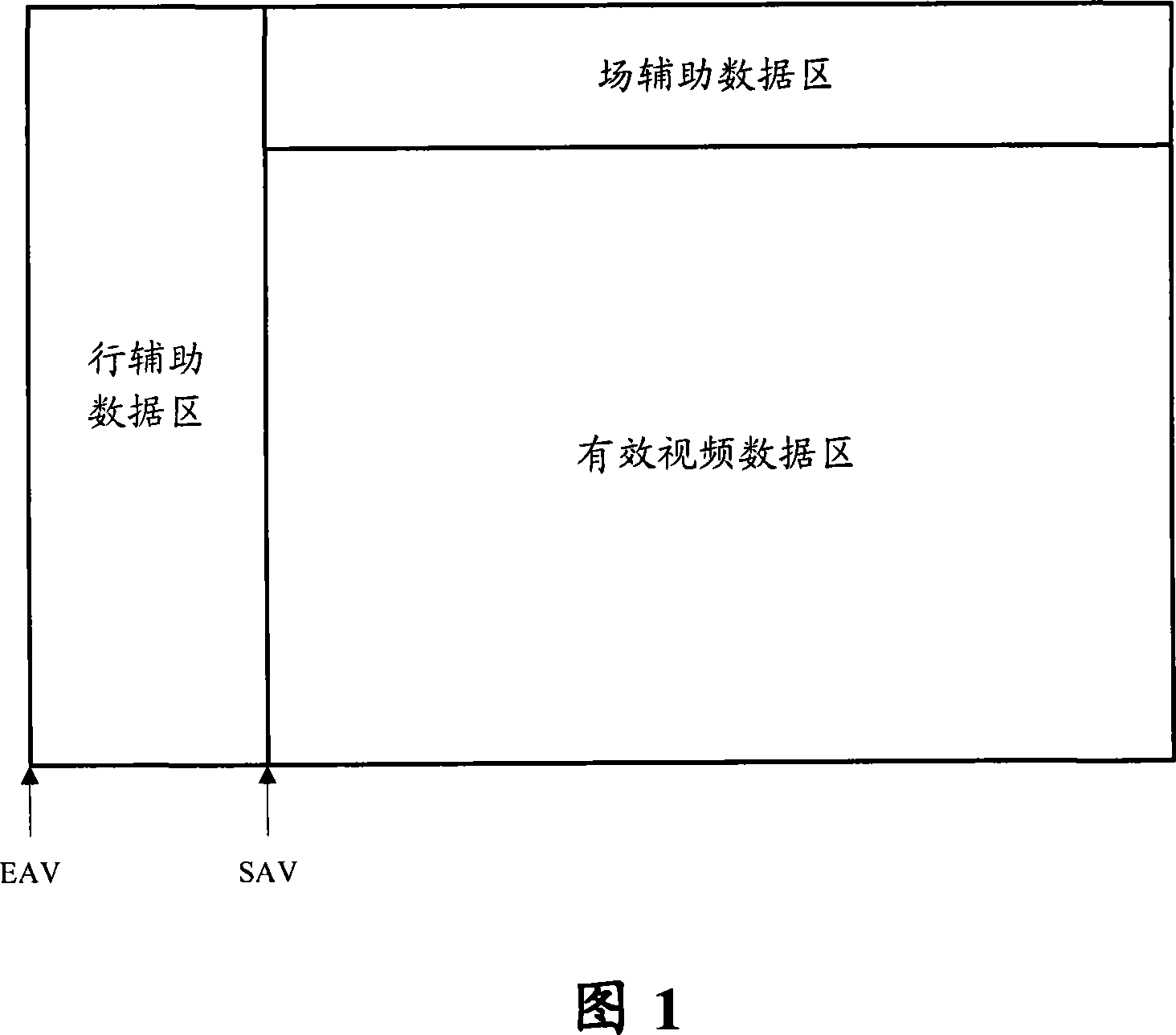

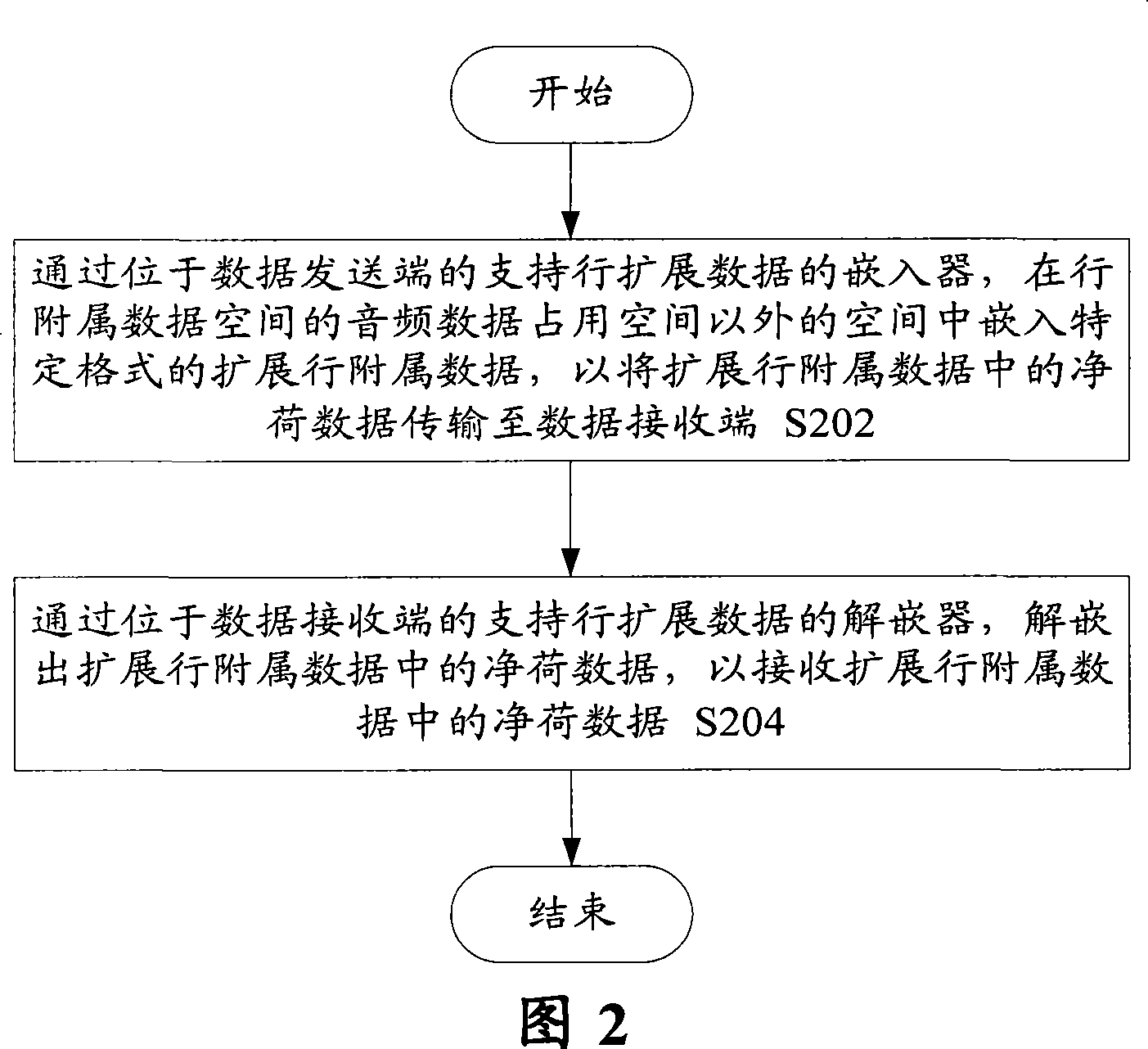

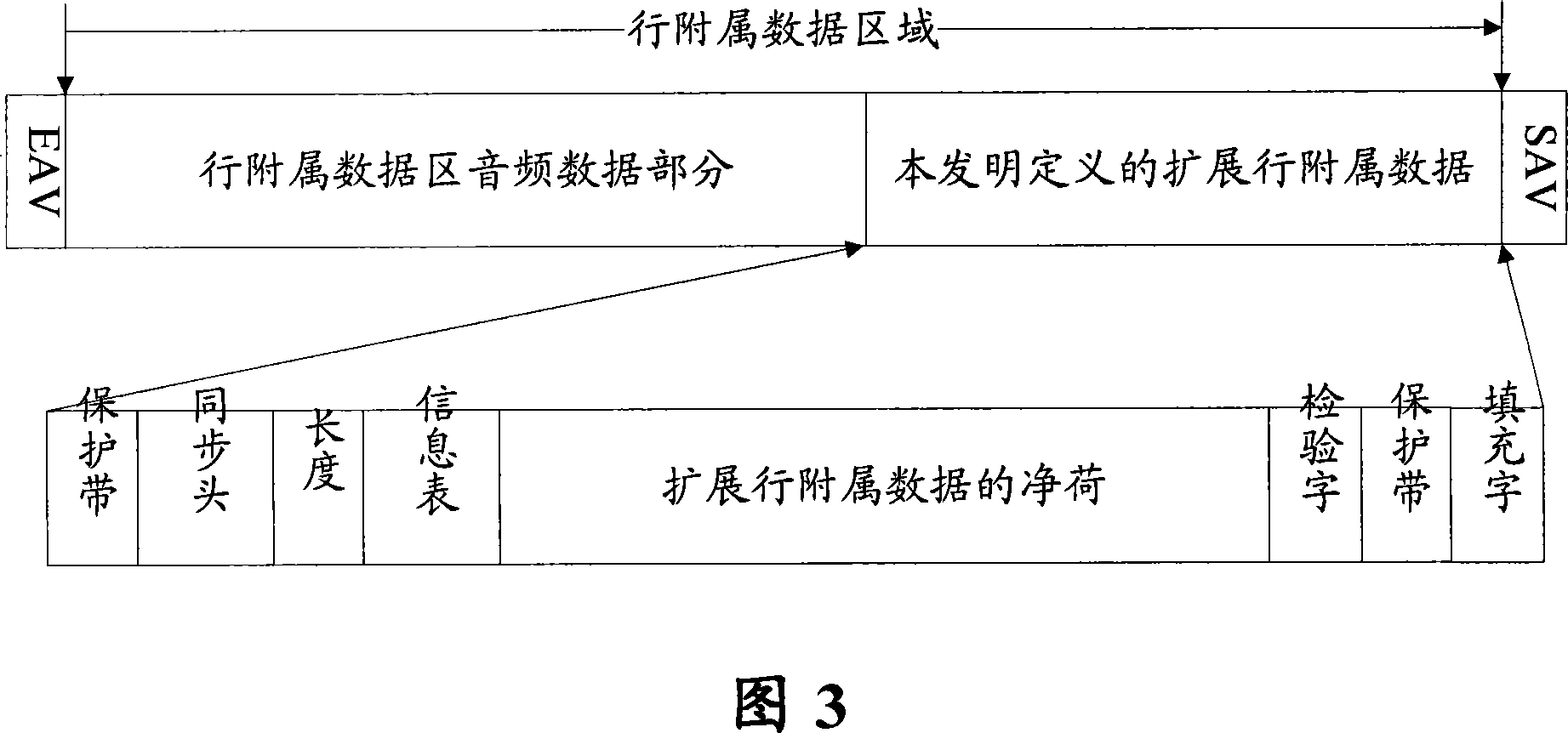

Data transmission method and system

ActiveCN101098213AIncrease profitDoes not affect the designError preventionTelevision conference systemsData spaceData transmission

The invention discloses a data transmission method and a relative system, wherein the method comprises that S202, via an embedded at a data sender, embedding an expansion row attach data with special format at the space outside the space occupied by voice data in a row attach data space, to transmit pure load data of expansion attach data to a data receiver, S204, a de-embed device at the data receiver de-embed the pure load data in the row attach data, to receive the pure load data in the expanded row attach data. The invention can fully utilize idle space to improve the utilization of system bandwidth.

Owner:ZTE CORP

Driving circuit of liquid crystal display panel and liquid crystal display panel using same

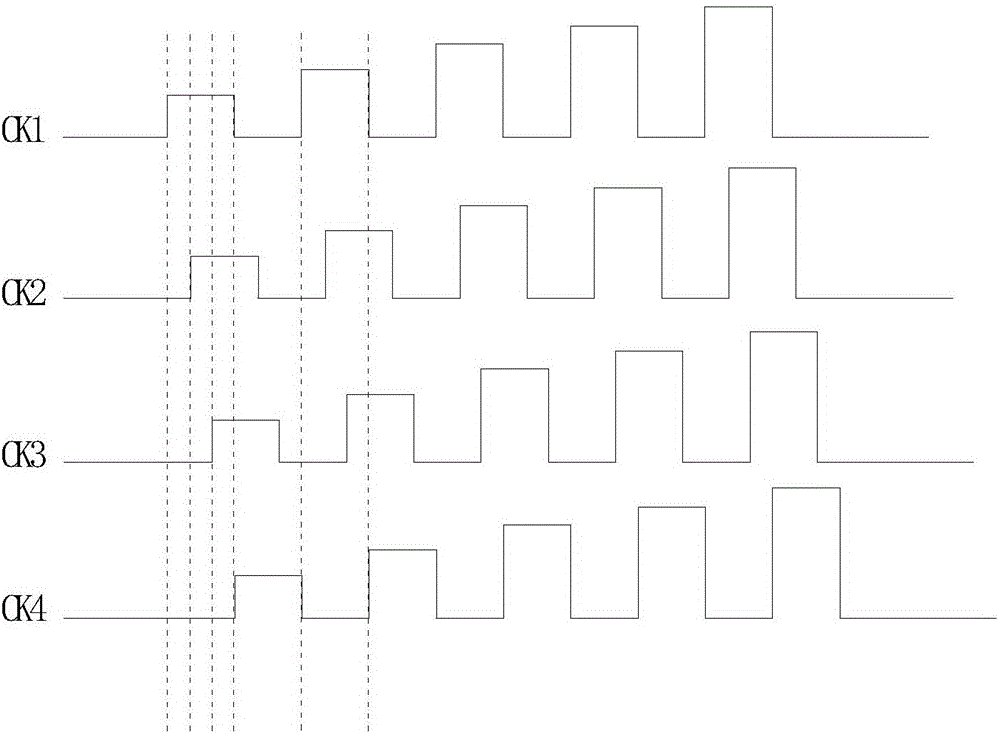

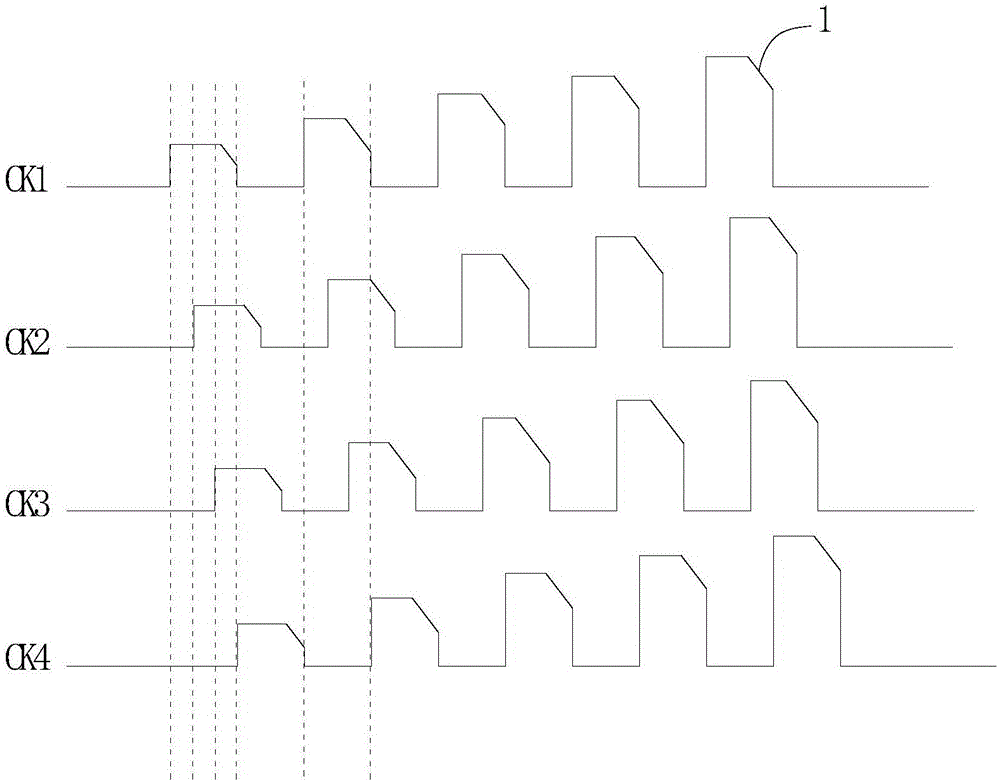

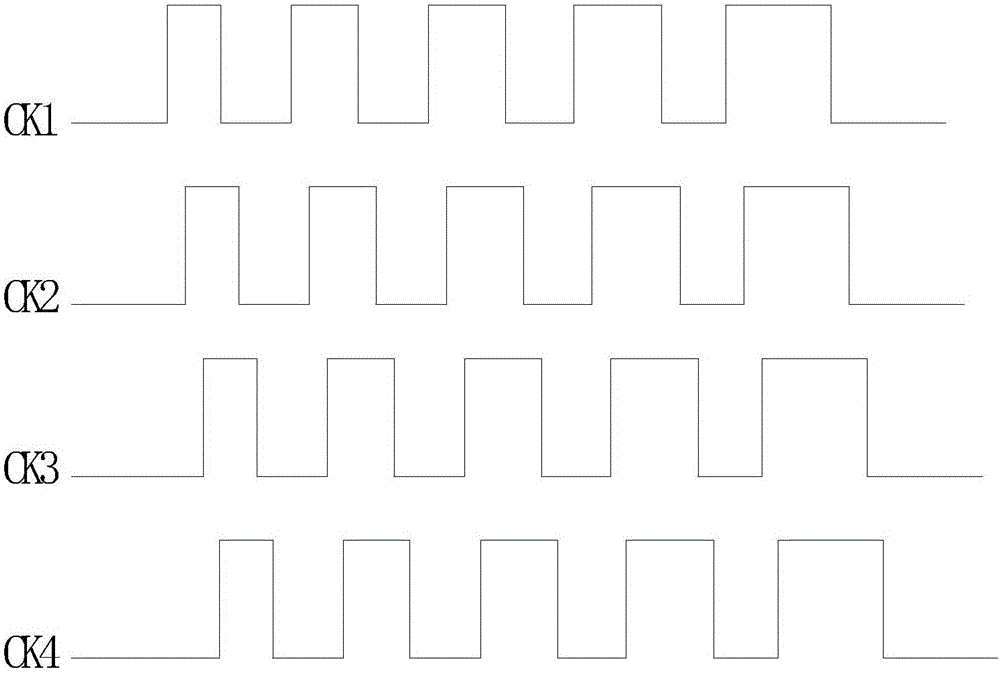

InactiveCN106128408AShow uniformGood qualityStatic indicating devicesIdentification meansLiquid-crystal displaySquare waveform

The invention provides a driving circuit of a liquid crystal display panel and a liquid crystal display panel using same. The driving circuit is used for outputting a plurality of clock control signals for driving scanning lines of the display area of the liquid crystal display panel in a one-to-one manner after passing through the GOA circuit of the liquid crystal display panel. The driving circuit and the liquid crystal display panel are characterized in that the driving circuit uses the clock control signals with preset waveforms, wherein the preset waveforms are periodical square waves; the high levels of the preset waveforms periodically increase; and furthermore the time lengths of the periods of the preset waveforms are same. The driving circuit and the liquid crystal display panel have advantages of reducing brightness differences in the vertical direction and the left-and-right direction of the liquid crystal display panel, improving driving capability of the GOA circuit, realizing higher display brightness uniformity of a large-dimension high-resolution liquid crystal display panel, and obtaining higher definition of a displayed picture.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

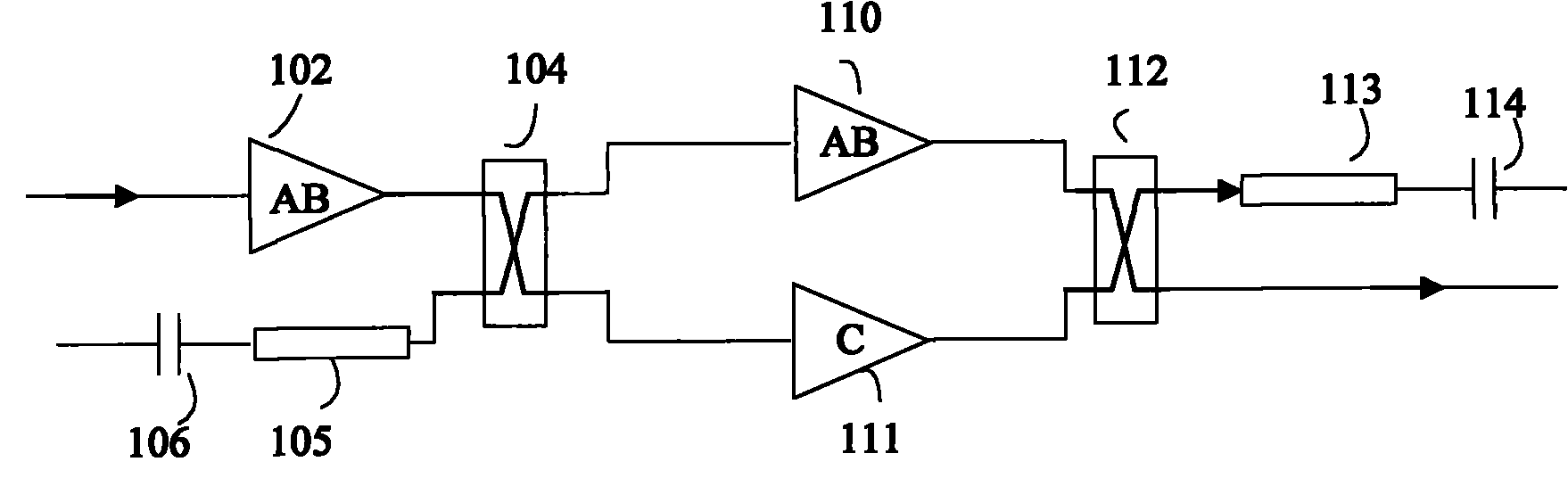

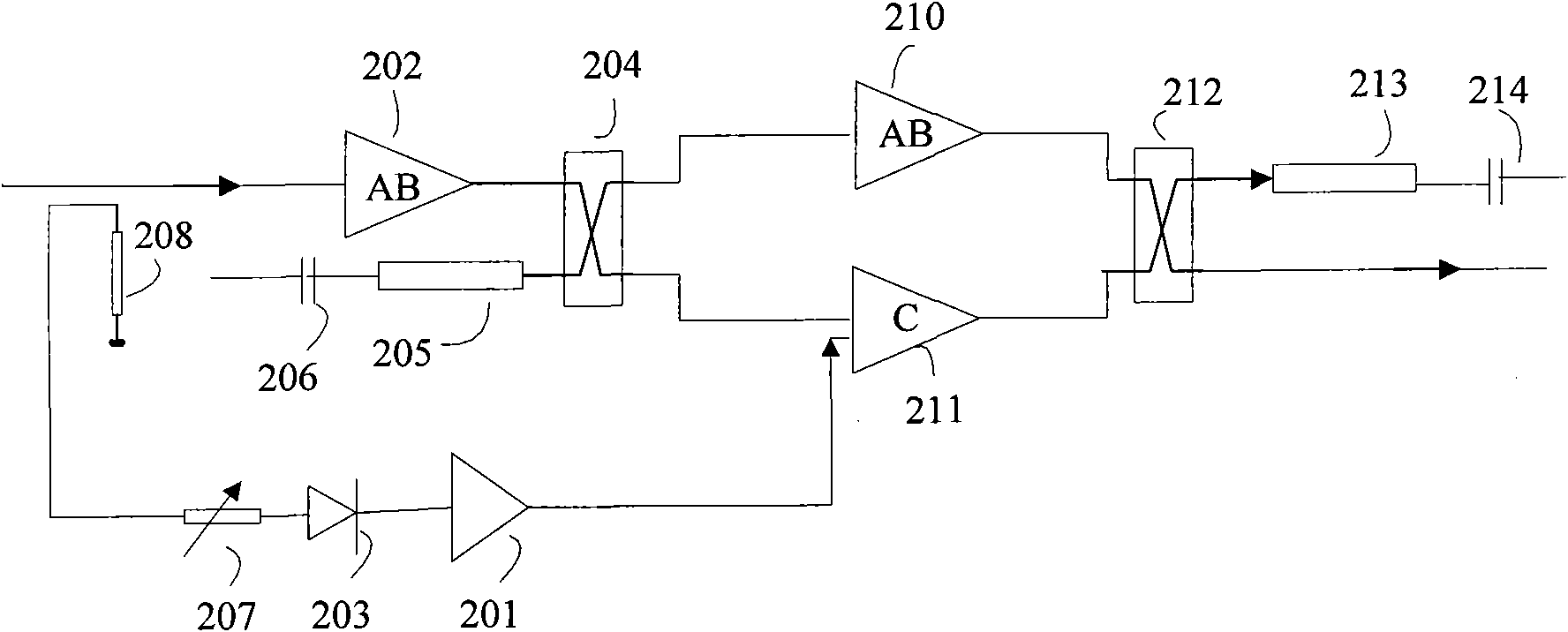

Efficient linear power amplifier circuit

InactiveCN101834571AOvercome deficienciesDoes not affect the designPower amplifiersAmplifier modifications to raise efficiencyCapacitanceAudio power amplifier

An efficient linear power amplifier circuit relates to the technical field of energy amplification and solves the technical problems of facilitating debugging and increasing efficiency. The circuit comprises a main amplifier, an auxiliary amplifier, a front radio-frequency bridge and a back radio-frequency bridge, wherein one input end of the front radio-frequency bridge is connected with an external signal source, the other input end is in serial connection with a pre-microstrip line and a pre-capacitor in turn, the two output ends are separately connected with the input end of the main amplifier and the input end of the auxiliary amplifier; the output ends of the main amplifier and auxiliary amplifier are separately connected with the two input ends of the back radio-frequency bridge; and one output end of the back radio-frequency bridge is used as the signal output end, and the other output end is in serial connection with a post-microstrip line and a post-capacitor. The circuit provided by the invention can provide wider bandwidth.

Owner:SHANGHAI TUYUE ELECTRONICS CO LTD

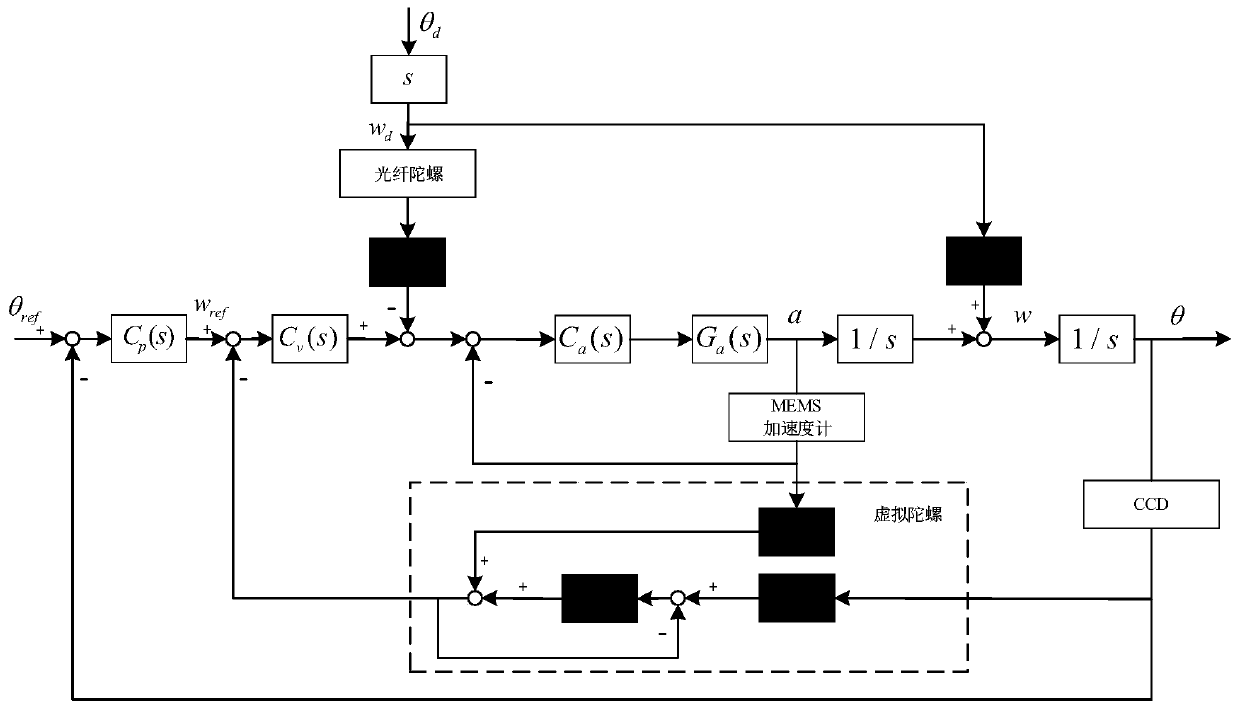

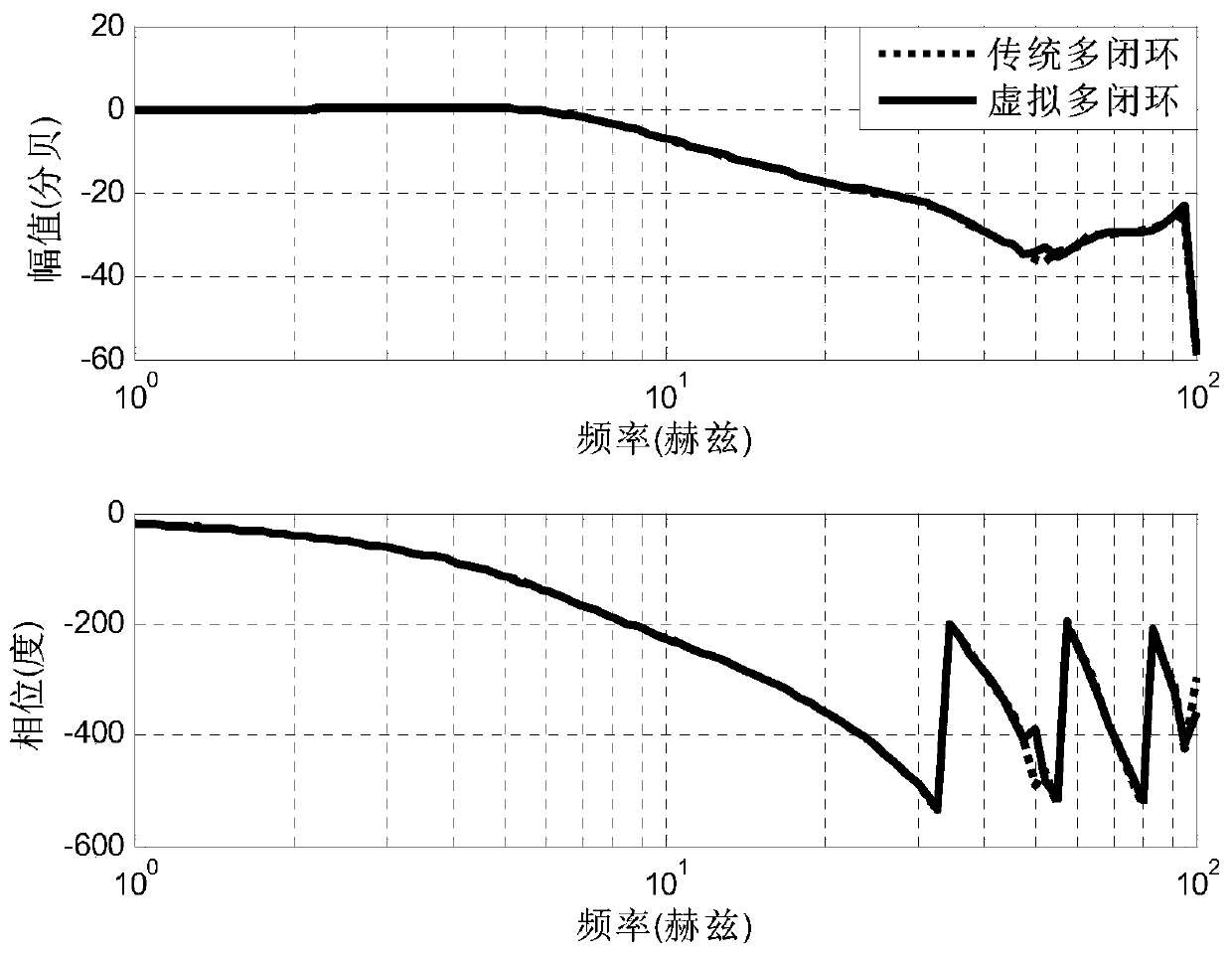

Virtual multi-closed loop-based disturbance measurement feedforward suppression method

ActiveCN110543123AHigh stability and precisionReduce load requirementsProgramme controlComputer controlFiberClosed-loop pole

The invention discloses a virtual multi-closed loop-based disturbance measurement feedforward suppression method. The virtual multi-closed loop-based disturbance measurement feedforward suppression method is used for improving the disturbance suppression capability of a control system stable platform so as to meet the demand of a higher-accuracy stable control system. A virtual gyro is obtained bya method of integrating an accelerator and a position sensor, and a fiber gyro of the stable platform is substituted by the virtual gyro. On the basis that virtual multi-closed loop control is achieved by the virtual gyro, the substituted fiber gyro is arranged on a carrier rack and is used for measuring an external disturbance speed, and an ideal feedforward compensation controller is used for feedforwarding the external disturbance to a control loop so as to actively suppress the influence of disturbance. On the premise that the system stability is not completely affected, the load and space requirement of the stable platform is effectively reduced, the disturbance suppression capability of the system is effectively improved, so that the stable platform obtains higher stability accuracy.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

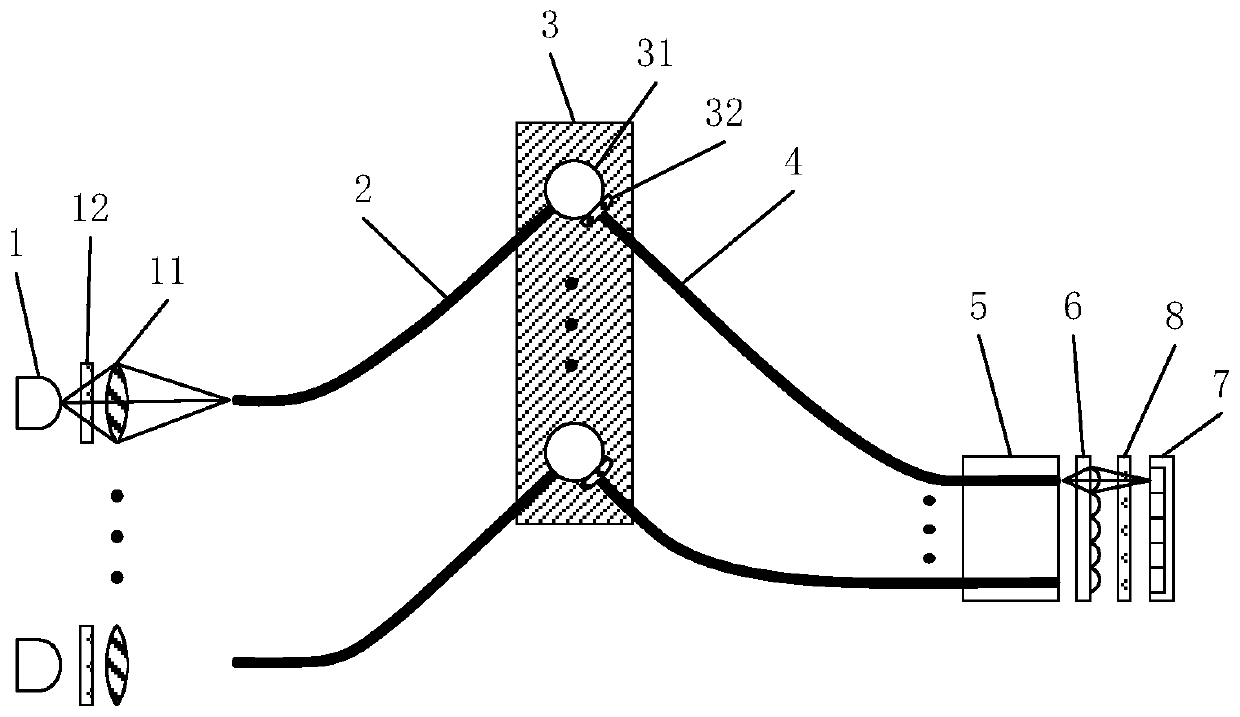

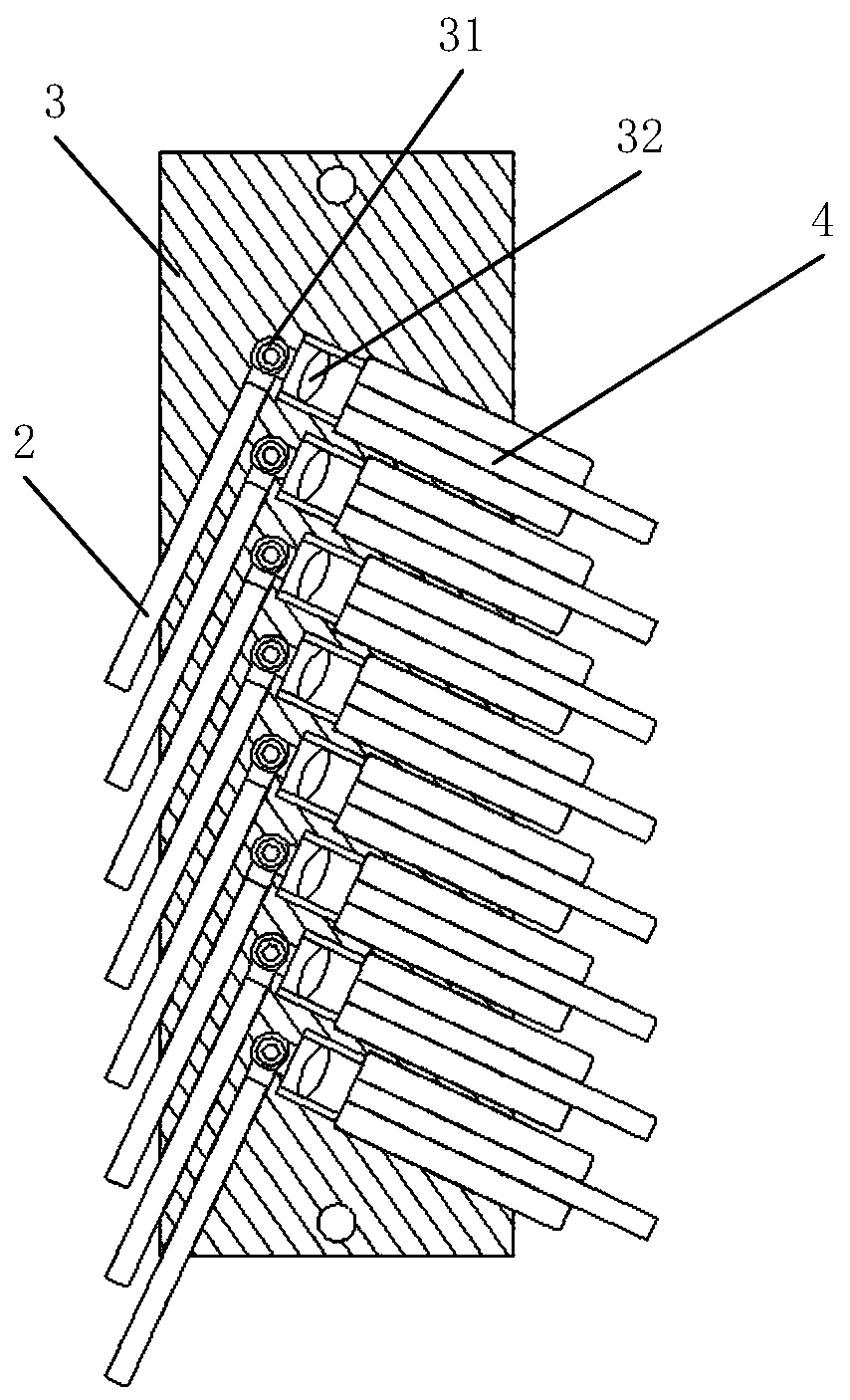

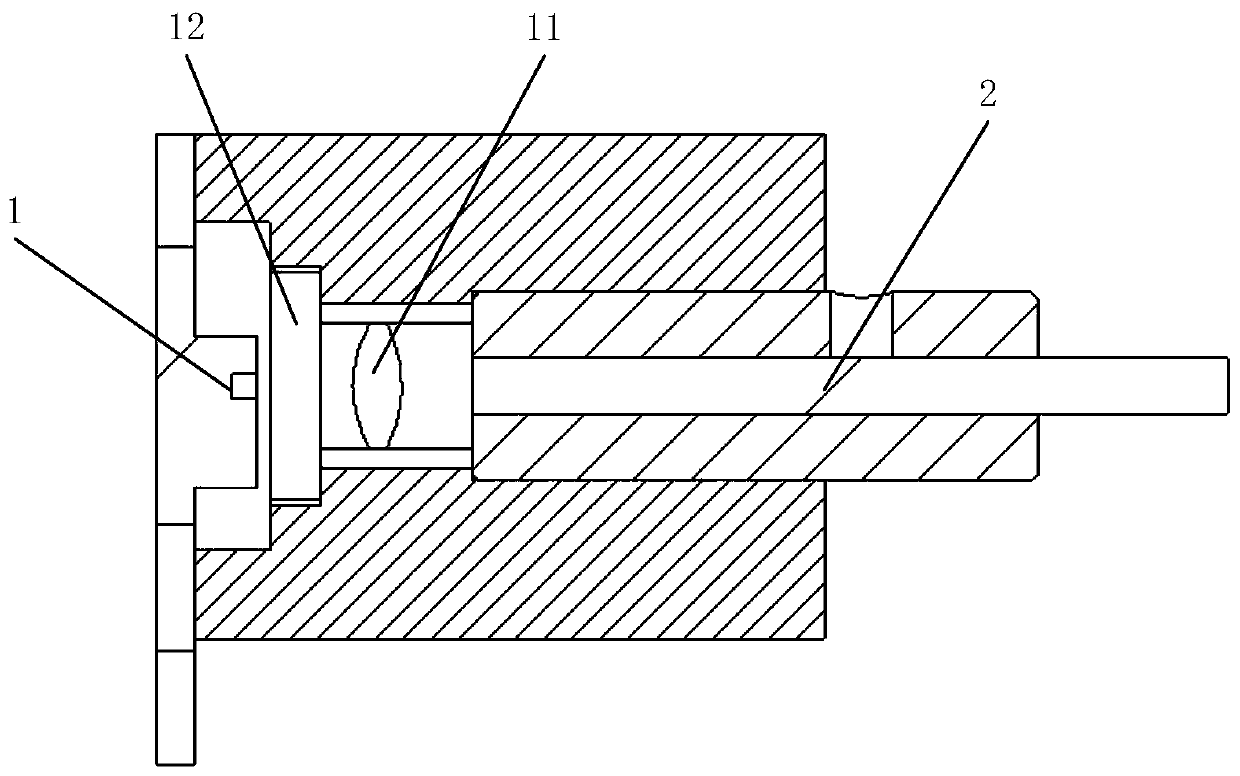

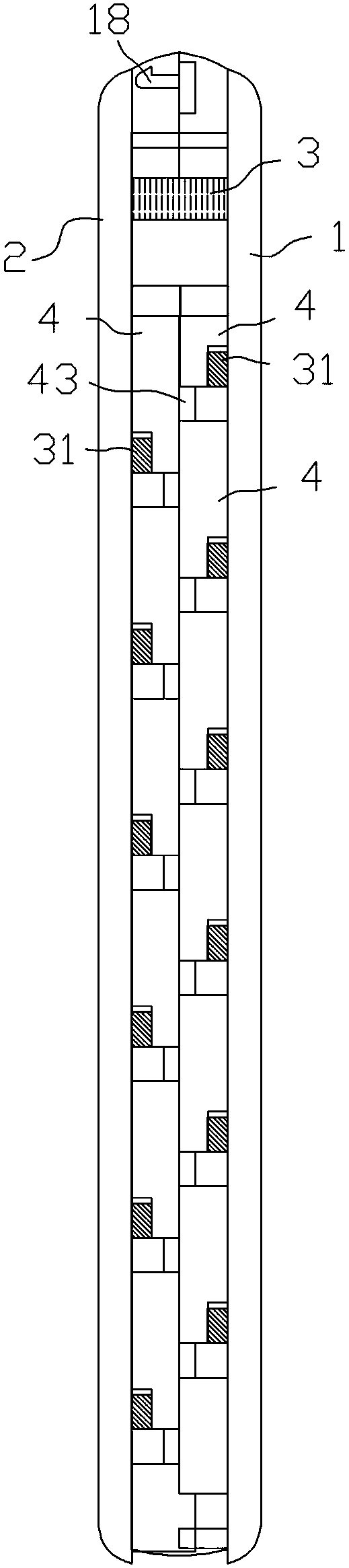

Optical detection device of multi-channel real-time fluorescence detector

InactiveCN110967324AHigh detection sensitivityHigh excitation light intensityFluorescence/phosphorescenceDetector arrayFluorescence

The invention discloses an optical detection device of a multichannel real-time fluorescence detector. The optical detection device comprises a sample block. A plurality of sample holes for placing sample tubes for detection are formed in the sample block. Each sample hole is correspondingly provided with an excitation optical fiber and a transmitting optical fiber. The excitation optical fibers are arranged on one side of the sample hole. The emission optical fibers are arranged on the other side of the sample hole, the excitation optical fibers are connected with the excitation light sources, each excitation optical fiber is correspondingly connected with one excitation light source, and the emission optical fibers are sequentially connected with the emission optical fiber light emittingmodule, the micro lens array and the fluorescence detector array. The excitation optical fiber and the emission optical fiber are arranged on the side face of the sample hole, detection on the upperportion or the bottom of the sample tube is not needed, design of the hot cover is not affected, and pollution of the detector is avoided.

Owner:INST OF ANALYSIS GUANGDONG ACAD OF SCI (CHINA NAT ANALYTICAL

Radio shielding device in mobile phone

InactiveCN101222531AEffective barrierLittle impact on performanceMagnetic/electric field screeningRadio/inductive link selection arrangementsMotherboardRadiofrequency signal

The invention discloses a radiofrequency shielding device inside a mobile phone, which comprises that: a support type PIFA antenna support is arranged on the top or the tail end of a mobile phone mainboard; the side wall near the antenna support is provided with a shielding support and a shielding cover; the lengths of the shielding support and the shielding cover are equivalent to that of the antenna support; the shielding cover is covered on the shielding support; the shielding support keeps close to a copper exposed area of the mainboard, is earthed and is arranged close to the rear wall of the antenna support to ensure that one folding edge of the shielding cover near the antenna support can keep close to the rear wall of the antenna support and extend upward along the rear wall of the antenna support until the top of the antenna support to form a shielding wall which surrounds the antenna and radiates toward the interior of the mobile phone; and other three folding edges of the shielding cover are clamped on the shielding support. The invention reduces the interference of radiofrequency signals of the antenna of the mobile phone to other interior sensitive devices by rationally adjusting the layout of the antenna support, the shielding support and the shielding cover.

Owner:WINGTECH COMM

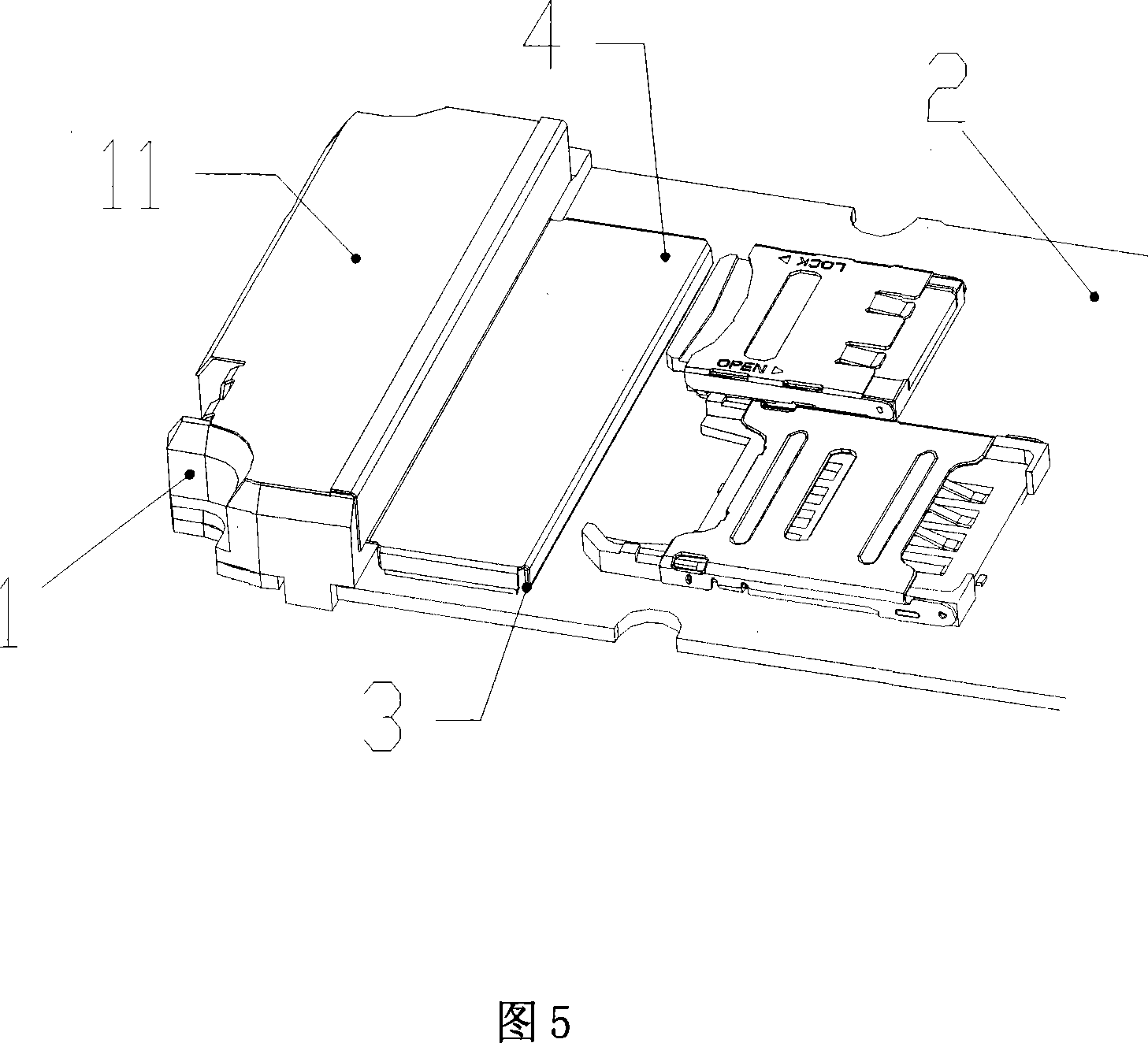

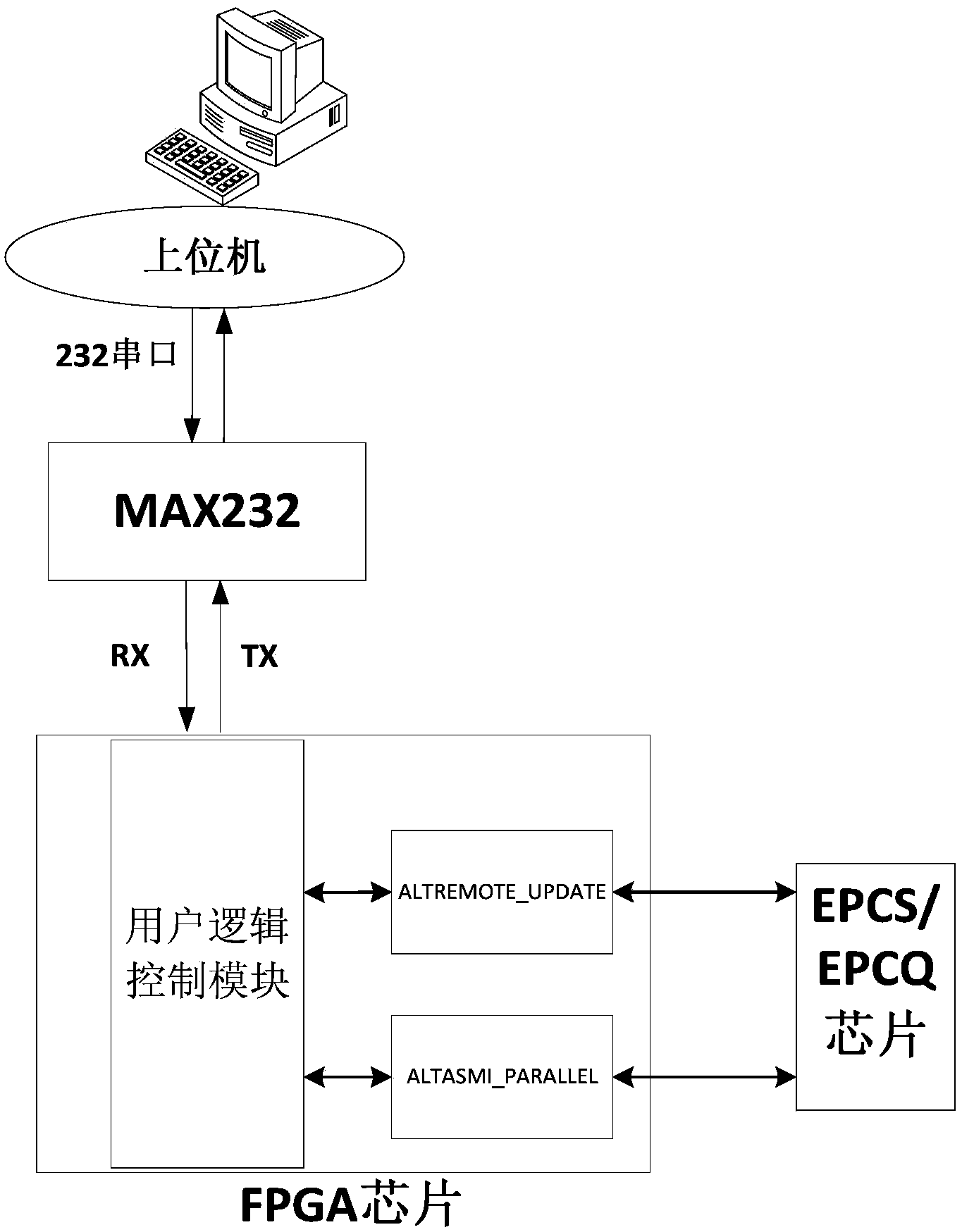

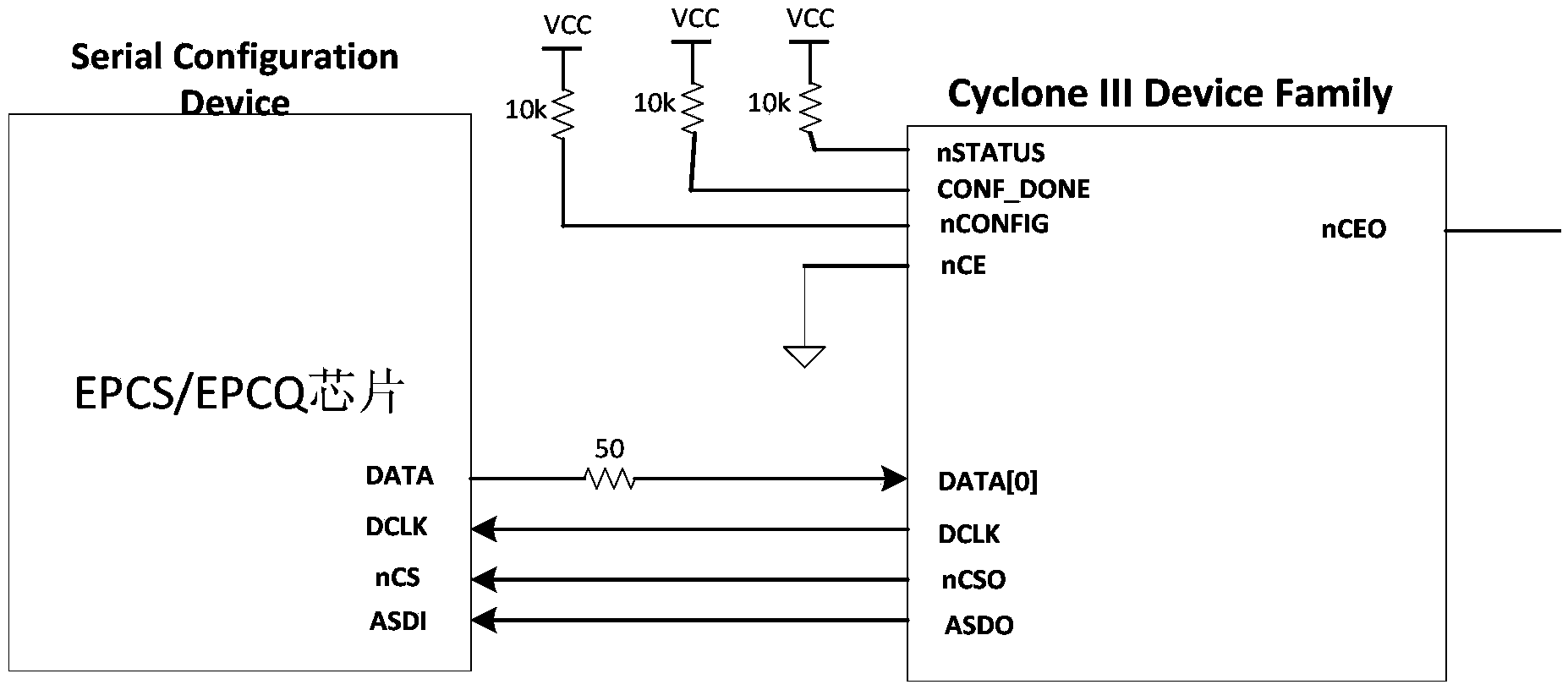

EPCS and EPCQ storer online upgrading method based on IP core in FPGA

ActiveCN104077166AReduce areaDoes not affect the designInput/output to record carriersProgram loading/initiatingSingle chipComputer engineering

The invention discloses an EPCS and EPCQ storer online upgrading method based on an IP core in an FPGA. The EPCS and EPCQ storer online upgrading method is used for solving the technical problem that an existing EPCS and EPCQ storer online upgrading method is poor in practicability. The technical scheme is that an EPCS / EPCQ erase command frame is sent to the FPGA through an upper computer, an FPGA programming file is read and sent to the FPGA frame by frame according to the 232 serial protocol, the upper computer sends a Reconfig command frame to the FPGA, a solid EPCS / EPCQ remote online upgrading module in the FPGA is in charge of analyzing the command frames sent by the upper computer and writing an erase command into the IP core according to a command and a format, and the IP core in the FPGA receives the command to carry out corresponding operation on the EPCS / EPCQ connected with the FPGA according to the command. The method can finish online upgrading of EPCS / EPCQ of the single-chip FPGA in one time, prevents a system from being disassembled and is strong in practicability.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

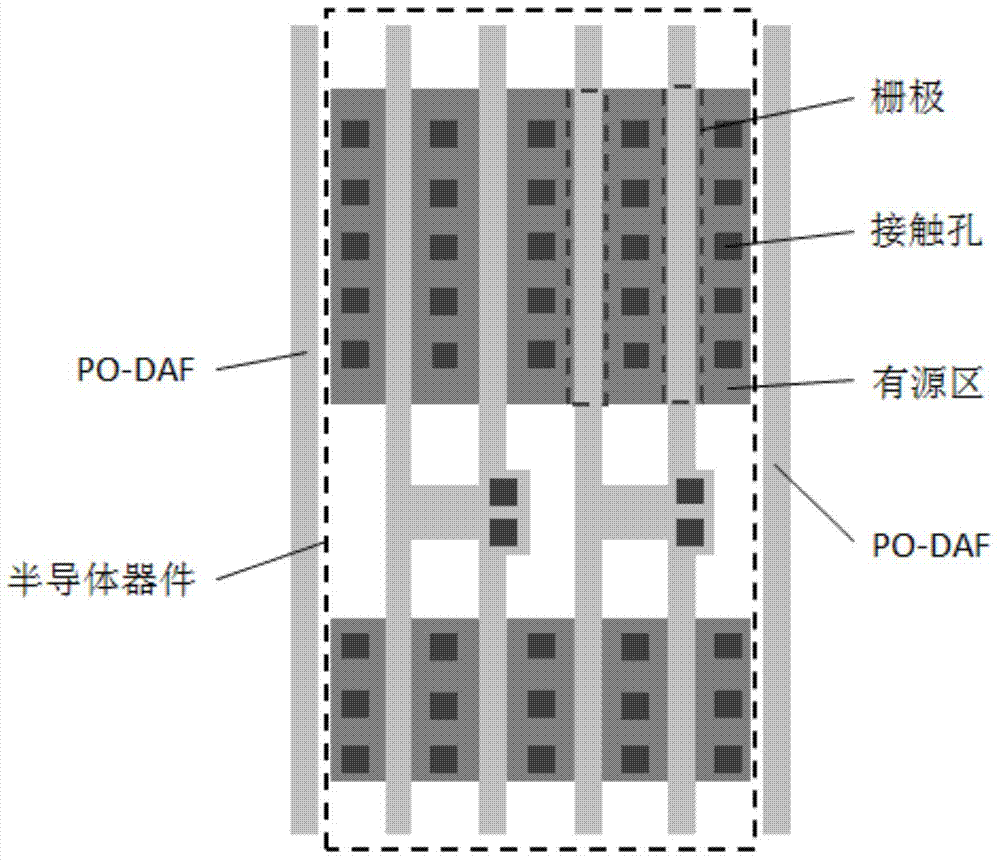

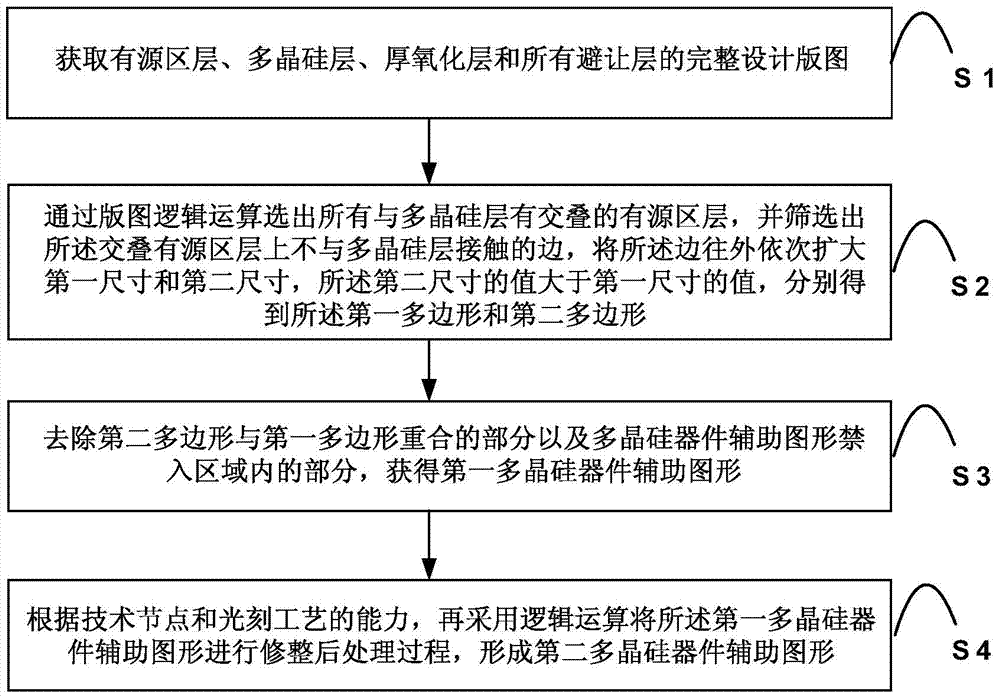

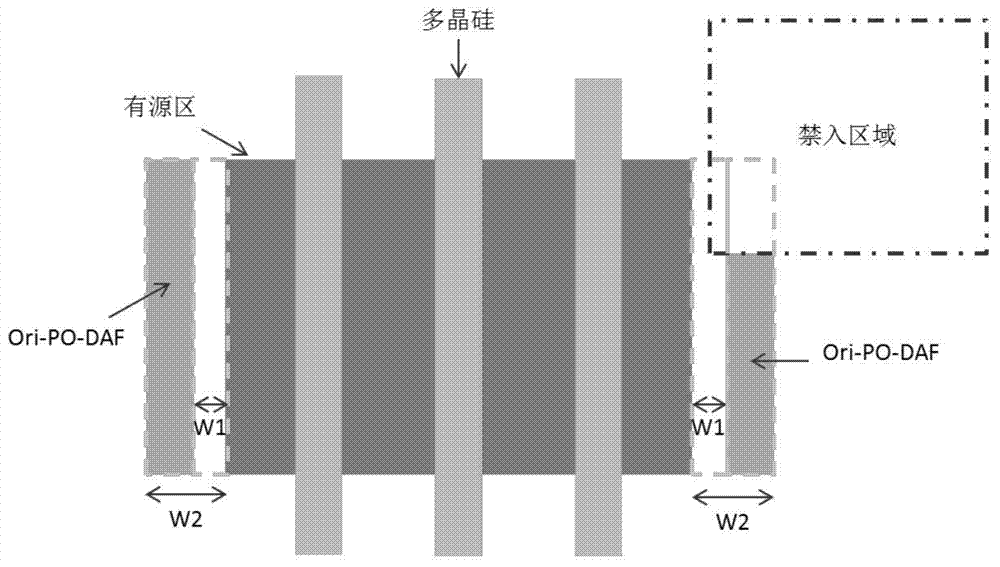

Drawing method for polycrystalline silicon layer device auxiliary graphs

ActiveCN103886153ADoes not affect the designAvoid wastingSpecial data processing applicationsPolycrystalline siliconOxide

The invention discloses a drawing method for polycrystalline silicon layer device auxiliary graphs. The drawing method includes the steps that a complete design layout of active area layers, a polycrystalline silicon layer, a thick oxide layer and all avoidance layers is obtained; the active area layers overlapped with the polycrystalline silicon layer are selected through the layout logic operation, edges, which are not in contact with the polycrystalline silicon layer, of the active area layers which are overlapped with the polycrystalline silicon layer are screened, the edges are expanded outwards by a first size and a second size sequentially, the value of the second size is larger than that of the first size, and a first polygon and a second polygon are obtained respectively; the part, coinciding with the first polygon, in the second polygon and the part of a prohibiting area of the polycrystalline silicon layer device auxiliary graph are removed, and the first polycrystalline silicon device auxiliary graph is obtained; finally, the first polycrystalline silicon device auxiliary graph is processed after being finished with the logic operation according to a technical node and the photolithographic process capacity, and the second polycrystalline silicon layer device auxiliary graph is formed. Thus, the drawing method can overcome the defect of leak adding due to design negligence, and much precious time is saved for on-time production of products.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Printing ink with tough effect and surface finishing technology for paper packing boxes

InactiveCN108059874AImprove appearance gradeStrong friction resistanceInksOther printing apparatusSurface finishingPOLYETHYLENE WAX

The invention relates to the field of packing and printing, and especially relates to a printing ink with a tough effect and a surface finishing technology for paper packing boxes. The printing ink comprises following raw materials in percentage by weight: 43 to 53% of polyurethane resin, 15 to 25% of epoxy resin, 3 to 6% of tri(propylene glycol) diacrylate, 3 to 6% of polyethylene wax, 1 to 3% ofphoto initiator TPO, 1 to 3% of photo initiator 369, 4 to 10% of silica, 4 to 8% of talcum powder, and 6 to 10% of bentonite. The printing ink is used to decorate the surface of a paper packing box by the provided surface finishing technology. The surface of the processed paper packing box has dark luster. People can feel flannelette touch when touching the surface of the paper packing box. The appearance of the paper packing box is upgraded, and the wear resistant performance of the surface of the paper packing box is strengthened.

Owner:SHANGHAI TOBACCO GRP CO LTD +1

Holographic anti counterfeit polyurethane membrane

InactiveCN1709692AHigh strengthGood optical performanceSynthetic resin layered productsCalcium biphosphatePolyester

The present invention relates to one kind of counterfeit-resistant polyester-base film which contains two intrinsic surfaces and two exterior ones, and everyone of the intrinsic surface has a definitive proportional crystallizing polyester and polyester-based film trimming materials. One of the extrinsic surfaces is a holographic counterfeit-resistant film, the other is a holographic counterfeit-resistant film or a generic polyester-based film. The holographic counterfeit-resistant film contains 10-100 percent amorphous polyester and 0-90 percent additive carrier according to mass percent. The generic polyester-base film contains 50-90 percent crystal polyester and 10-50 percent additive carrier according to mass percent. The additive carrier talked about upward contains silicon dioxide, kaolin, calcium phosphate or barium sulfate, besides crystallizing polyester, and the content of the additive carrier is 3000pp which is counted according to mass percent. The holographic counterfeit-resistant polyester-based film, so that the holographic counterfeit-resistant design can be die stamped at first hand. It will increase of efficiency, reduce the cost of production.

Owner:WEIFANG FUWEI PLASTIC

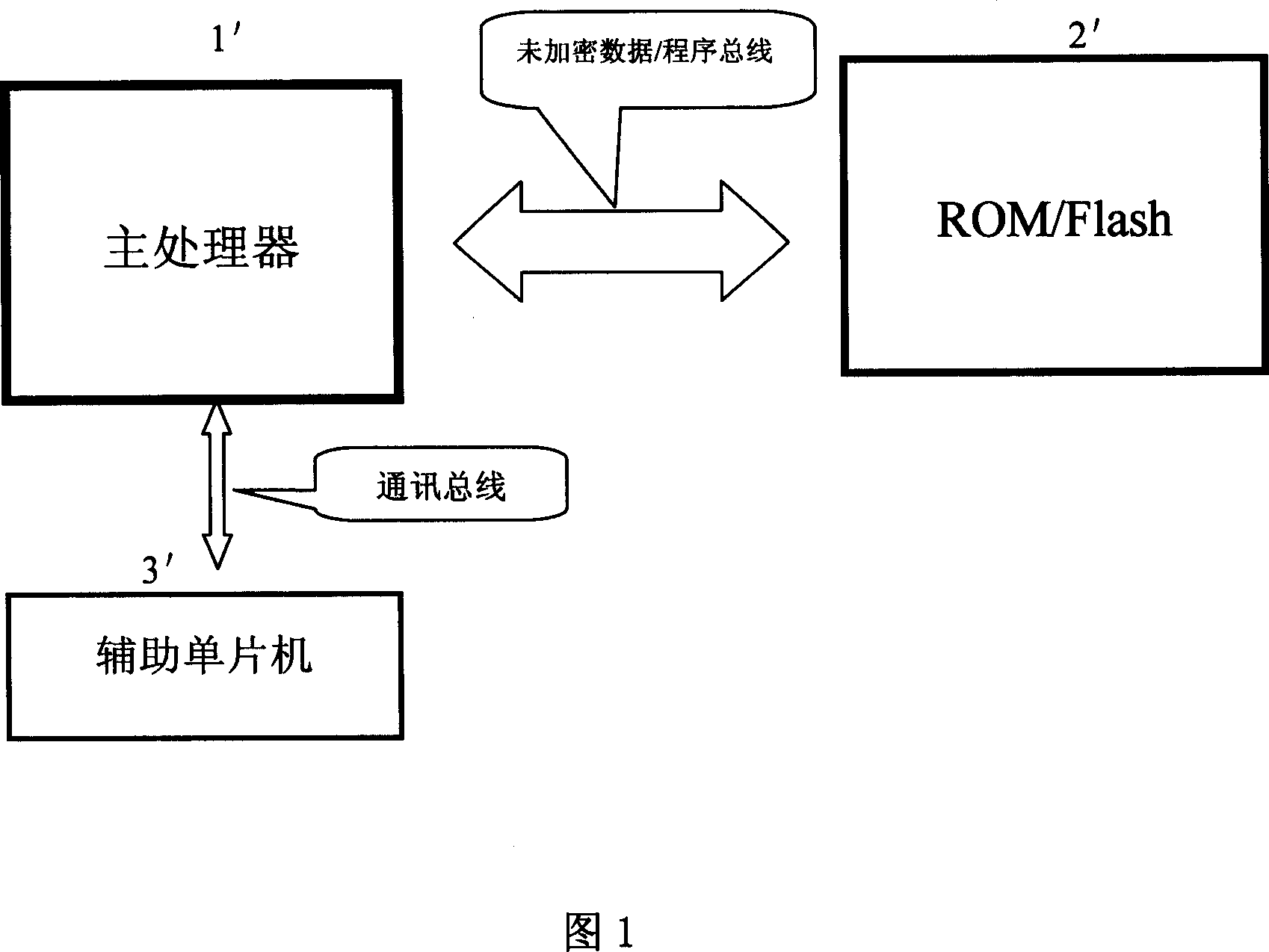

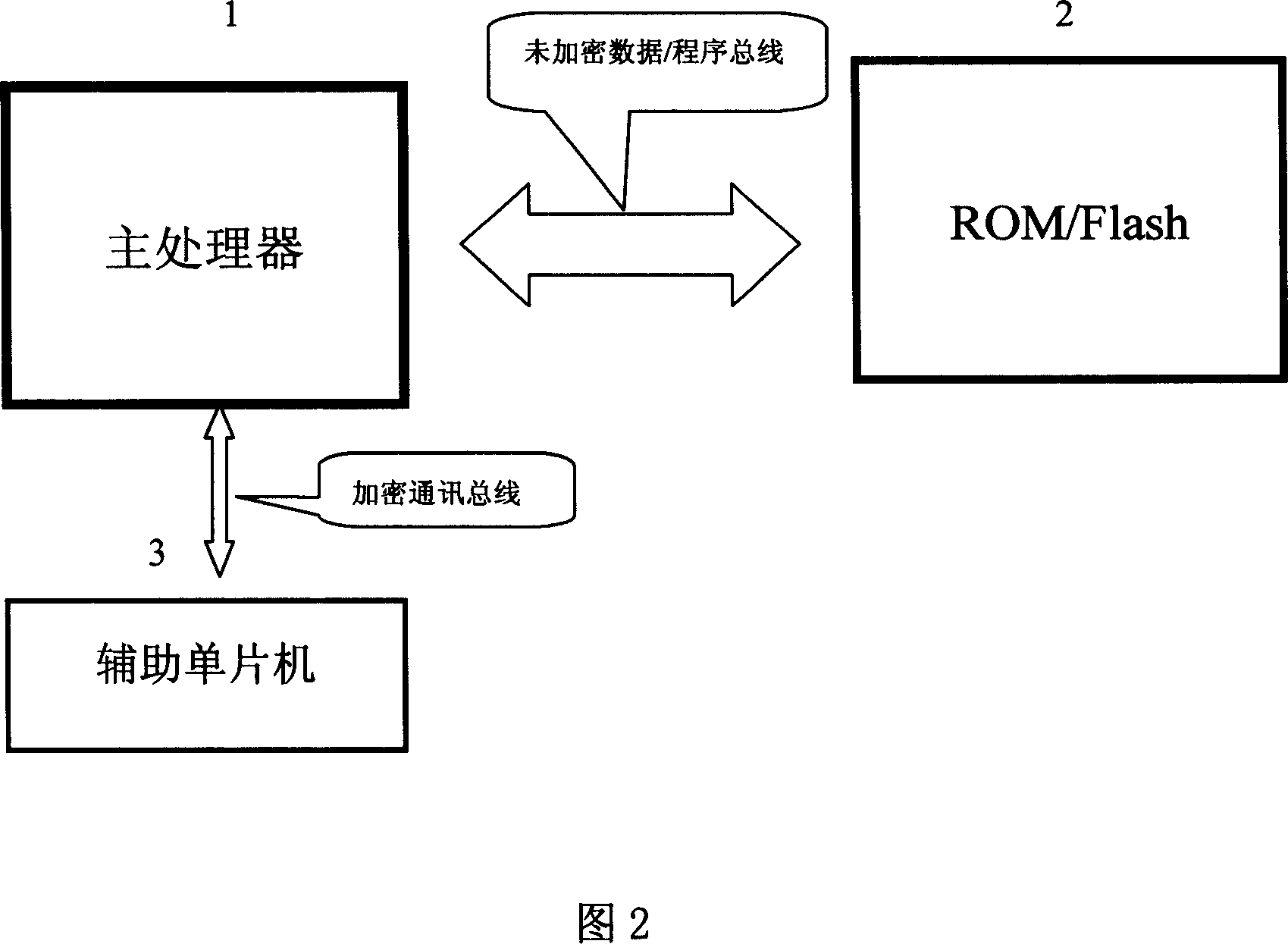

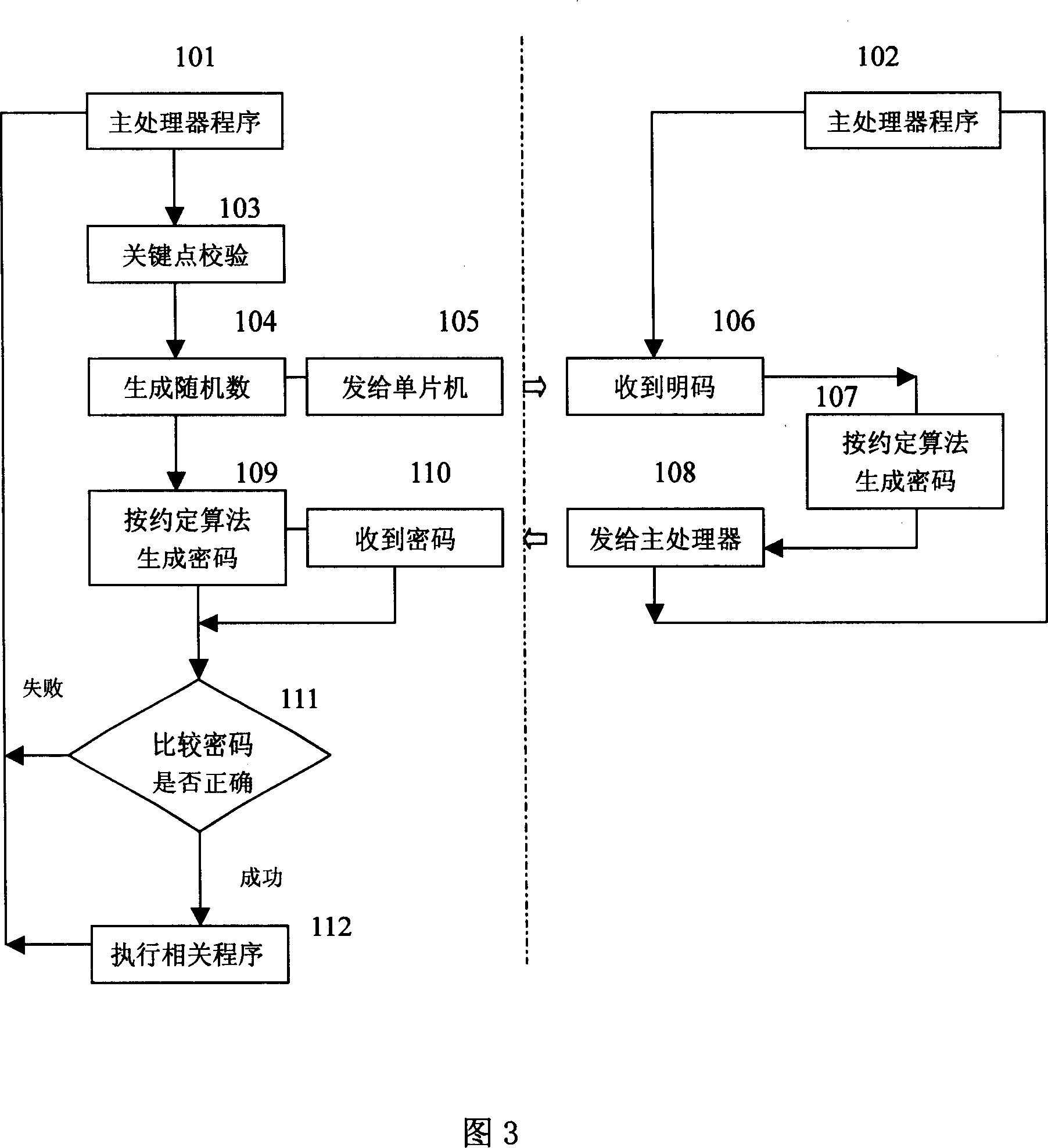

System encrypted method using multifunctional assistant SCM

ActiveCN1971470AEasy to modify and upgradeFunction increaseDigital data processing detailsInternal/peripheral component protectionMicrocontrollerCryptography protocols

The invention discloses a system enciphering method adopting multi-purpose auxiliary singlechip, it is in multiple microprocessor system, the support microprocessor (for example power management support microprocessor) that its function is relatively simple and the amount of software programme is few is substituted with singlechip which equipped with inner read only program memory, the code checking of the stipulated enciphering protocol algorithm is added to the program of main processor and auxiliary singlechip to avoid the program to be read out and copied, so the purpose of system encryption can be achieved.

Owner:XIAMEN PRIMA TECH

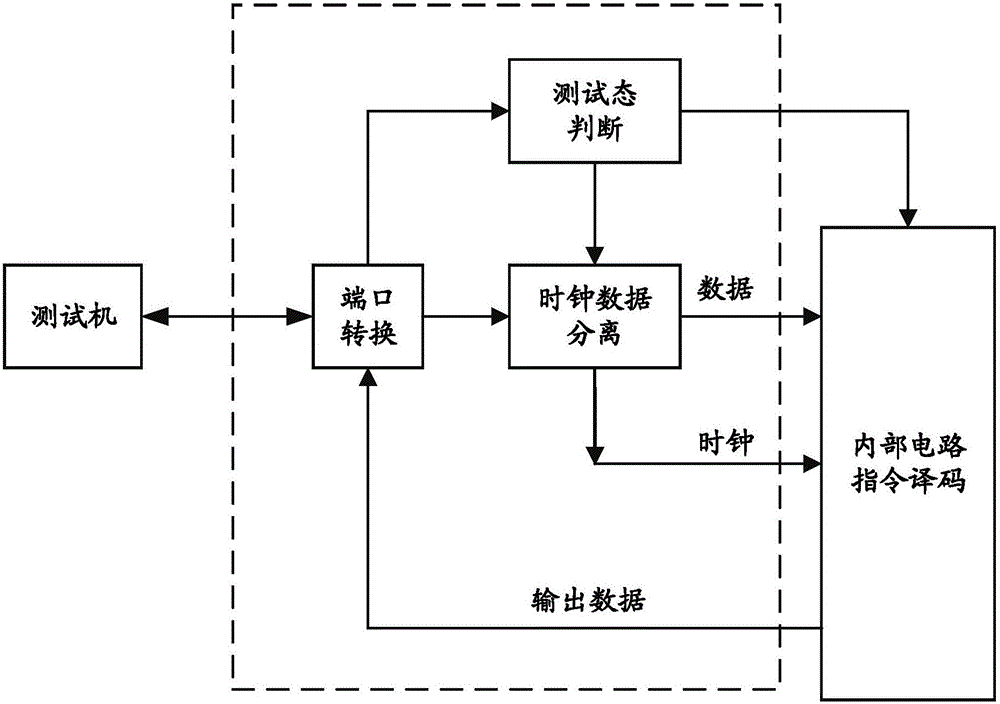

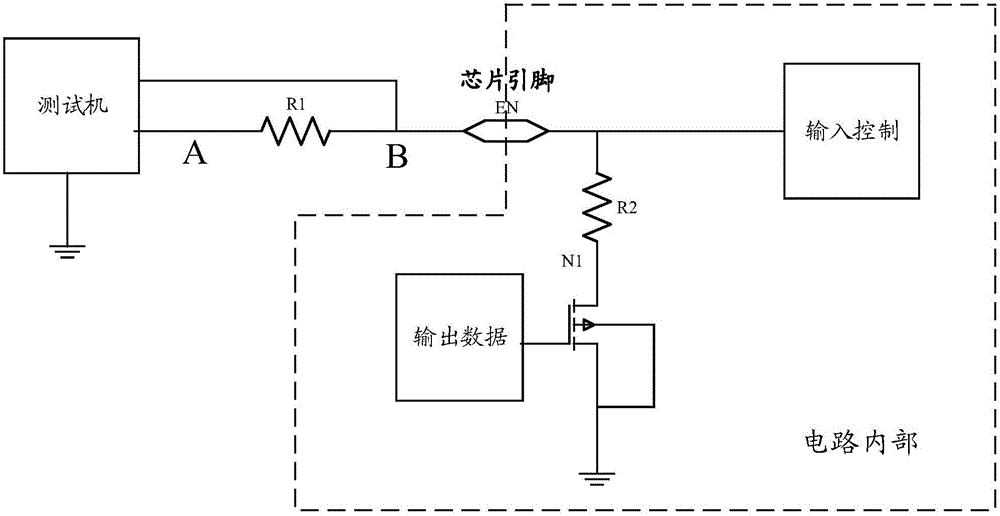

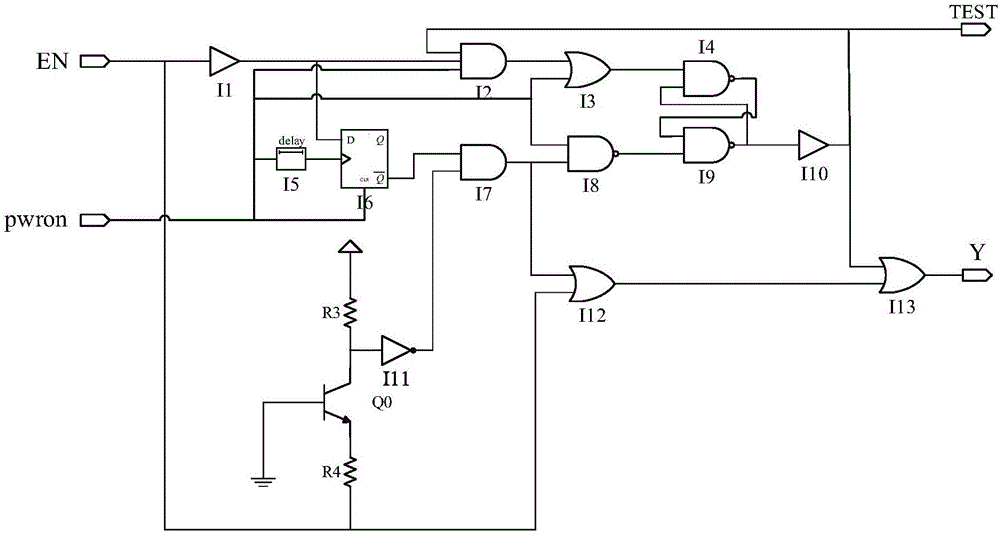

Integrated circuit testing circuit structure capable of realizing single-port multifunctional multiplexing

ActiveCN106443408ASimple structureFirmly connectedElectronic circuit testingMultiplexingPackage testing

The invention relates to an integrated circuit testing circuit structure capable of realizing single-port multifunctional multiplexing. The circuit structure includes a port conversion module, a test state determination module, and a clock data separation module; the port conversion module converts the port between the input state and the output state, discriminates the input data and output data, realizes the data exchange between a test machine and a test circuit; the port conversion module is connected with an internal circuit and the test machine, the test state determination module determines whether an input signal determination circuit enters into the test state, the test state determination module is connected with the clock data separation module, the port conversion module and the internal circuit, the clock data separation module separates the input data into a clock signal and a data signal and transmits the input data to the internal circuit, and the clock data separation module is connected with the port conversion module and the internal circuit. By means of such a circuit structure, only one present port can realize the wafer testing and packaged testing of an integrated circuit, so that the circuit structure is wide in application.

Owner:CRM ICBG (WUXI) CO LTD

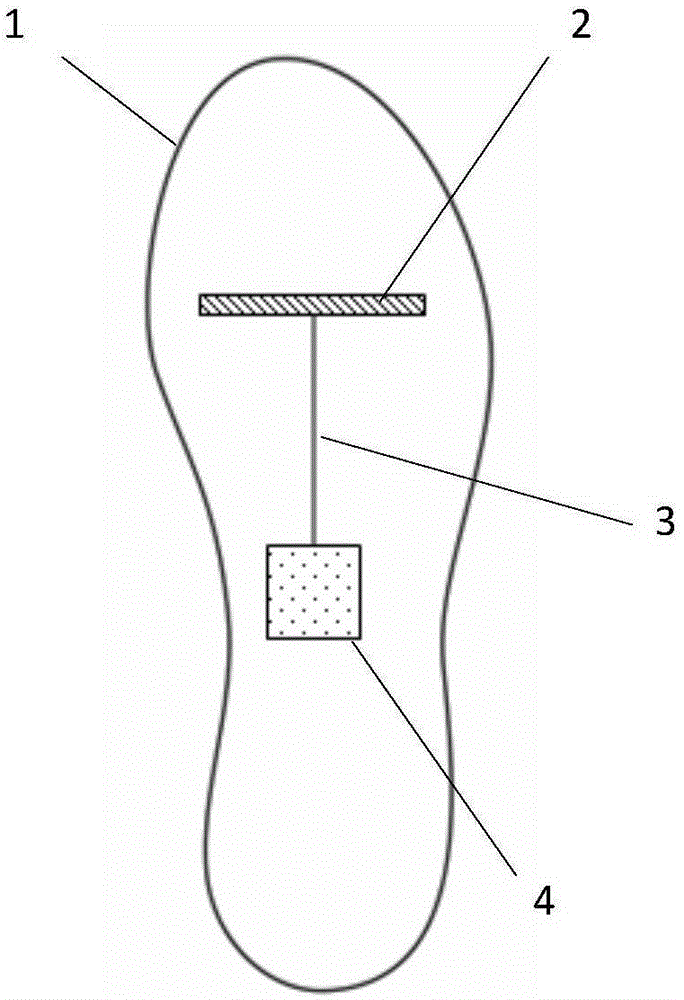

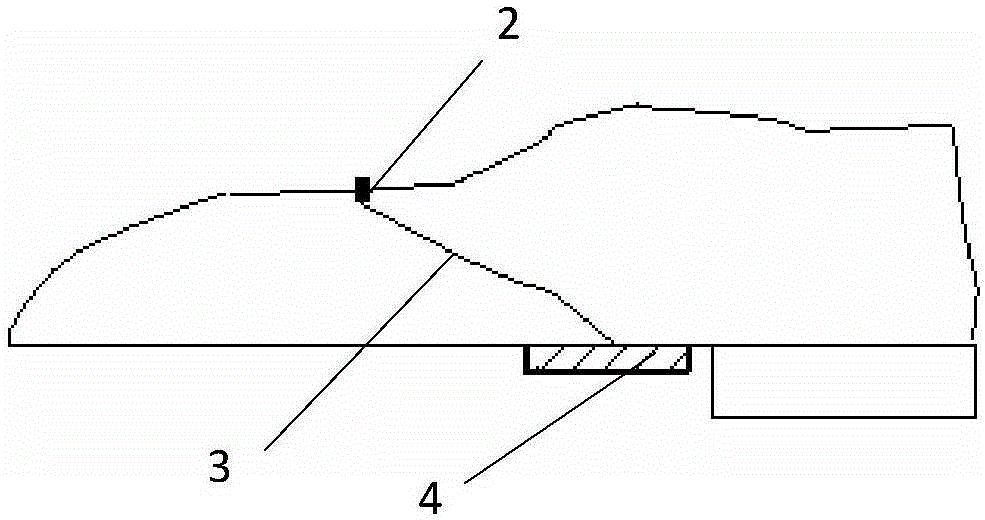

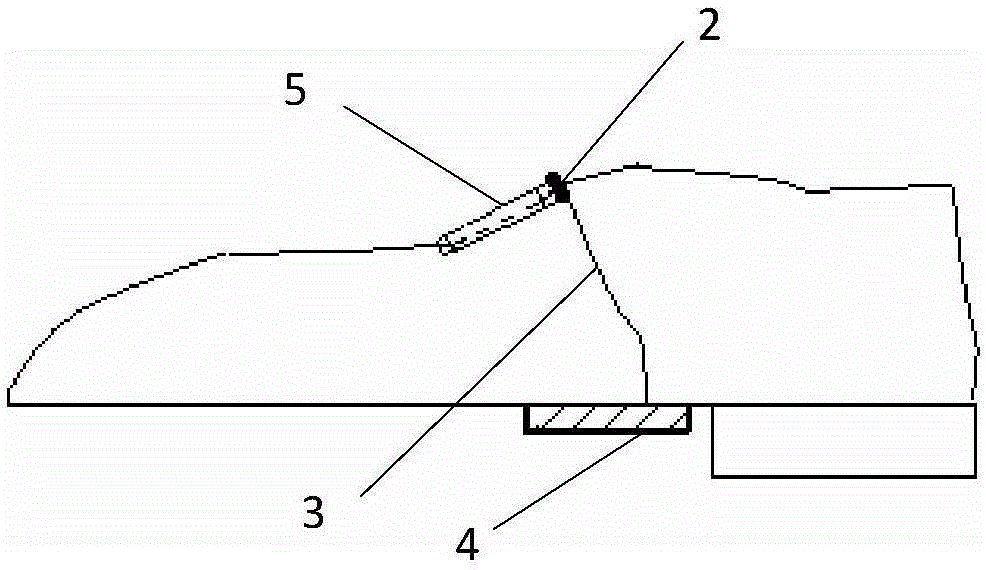

Shoes capable of collecting energy

ActiveCN105167308ADoes not affect the designReduce the occupied areaBatteries circuit arrangementsElectric powerElectricityElectrical battery

The invention discloses a pair of shoes capable of collecting energy. Each shoe comprises a piezoelectric material and a battery, wherein the piezoelectric material is associated with a bendable part of the shoe, so that when the shoe moves, the bendable part bends to extrude the piezoelectric material so as to output power; the battery is arranged on the shoe and is electrically with the piezoelectric material so as to store the power. According to the pair of shoes, the energy is collected by utilizing the extrusion pressure generated by bending of the shoes, so that a complete and convenient energy utilization mode is provided.

Owner:LENOVO (BEIJING) CO LTD

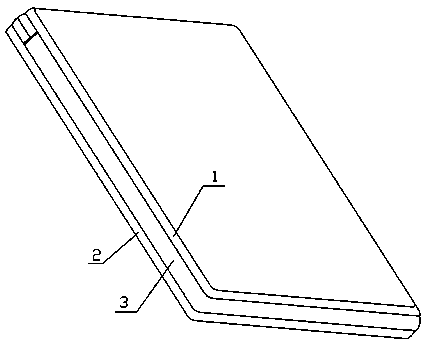

Waste heat recycle device for automobile cooling water

InactiveCN103306852ALow temperature start is beneficialReduce wearLiquid coolingInternal combustion piston enginesHeat transmissionHeat conducting

The invention relates to a waste heat recycle device for automobile cooling water and belongs to the field of waste heat recycle. Waste heat of the cooling water is recovered for low-temperature start of an automobile; the waste heat recycle device is provided with a heat storage and exchange device (1) internally equipped with a phase change heat storage material (3); the waste heat recycle device is internally provided with independent heat exchange units for transmitting and circulating heat outside with different heat-conducting working media and different circulation pipelines to heat an object; water serves as the heat-conducting working medium; the waste heat can be transmitted into the heat storage and exchange device (1) through the corresponding heat exchange units, and recovered and stored in the phase change heat storage material (3); the heat can also be transmitted outside to preheat the cooling water for the low-temperature start of an engine; in addition, preheated machine oil can be pumped into a main oil gallery of the engine first through the circulation pipeline of the heat transmission working medium, namely the machine oil, enters friction pairs to establish oil pressure, and can greatly reduce the friction during the low-temperature start of the engine; and the waste heat recycle device is energy-saving, environment-friendly, simple in structure, easy to implement and convenient to mount and use, does not influence the original automobile design, facilitates standard and industrial production, and is applicable to various motor vehicles.

Owner:高志男

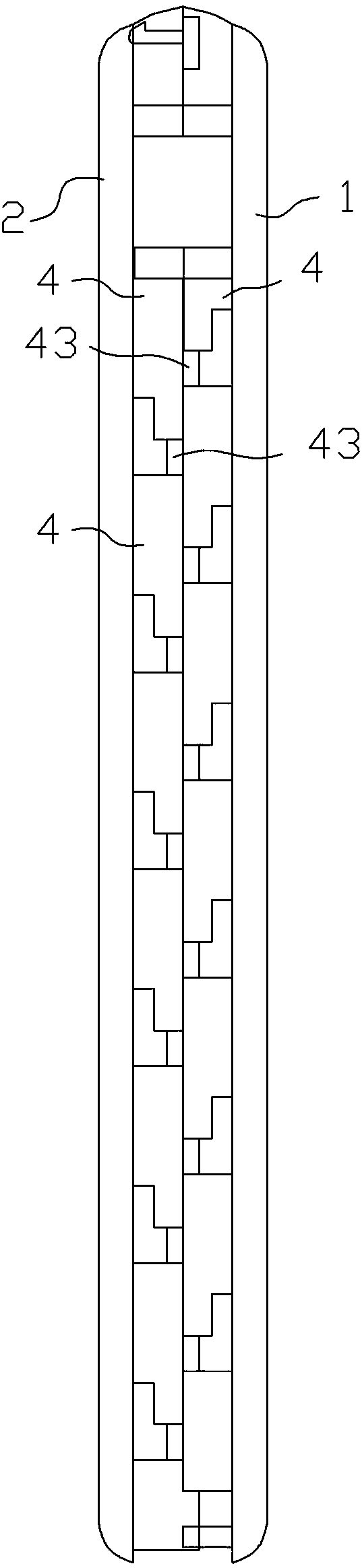

Mating connection structure for shell

ActiveCN103997866AEnable connectivityAchieve disassemblyCasings/cabinets/drawers detailsMating connectionAgricultural engineering

A mating connection structure for a shell comprises a plurality of staggered connection teeth provided on two shell pieces, and a connection frame for connecting the two shell pieces, wherein the connection frame is fixedlysecured to the connection teeth on the two shell pieces through a fixing sheet arranged on the connection frame, the staggered connection teeth restrict the relative movement of the two shell pieces in up and down directions with top blocks arranged on the connection teeth, and the connection frame restricts the relative movement of the two shell pieces on in back and forth as well as left and right directions. Said mating connection structure has a simple structure and excellent connection strength, and does not need to occupy the usage space inside the shell, so that the circuit board design for the shell is facilitated, the volume of the shell casing is reduced, and therefore the shell has a more attracting appearance, enhancing its market competitiveness and reduces the production cost.

Owner:GUANGZHOU KENTLI ELECTRONICS TECH CO LTD

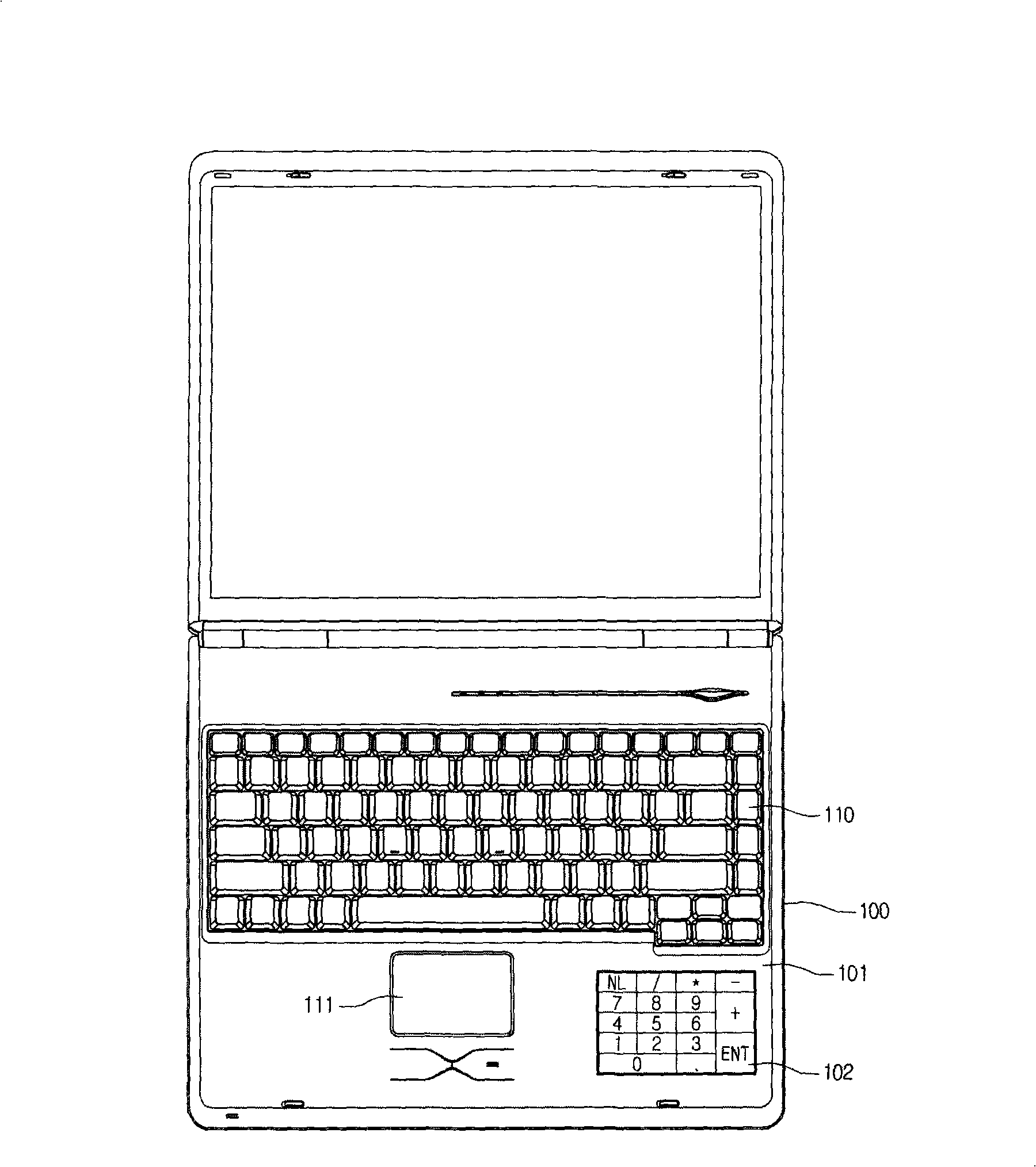

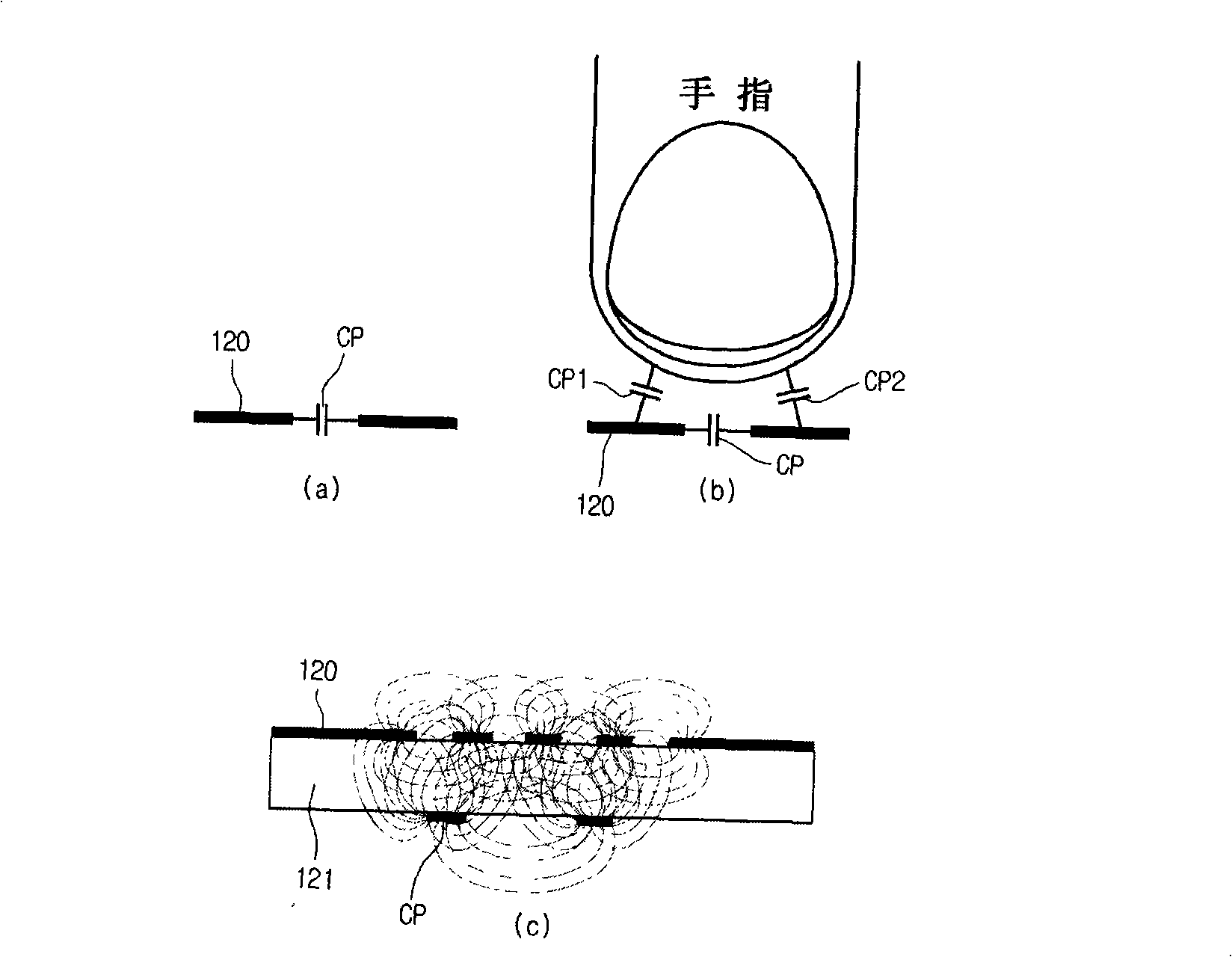

Portable computer and its press key input device

InactiveCN101320308AAdd button functionDoes not affect the designDigital data processing detailsInput/output processes for data processingEngineeringStatic electricity

The invention provides a portable computer and a keystroke device, in particular to a device and a method of performing keystroke by using the change of electrostatic capacity. The key device of the portable computer is characterized in that the keystroke device comprises a plurality of electrostatic capacity units sensing the electrostatic capacity, a signal checkout unit and a signal transmission unit. The electrostatic capacity units are arranged on the lower part of a main frame. The signal checkout unit checkouts the sensing signals of the electrostatic capacity unit in the form of a keying signal. And the signal transmission unit transmits the checkout sensing signals to a system according to the signal checkout unit.

Owner:LEJIN ELECTRONICS KUNSHAN COMPUTER CO LTD

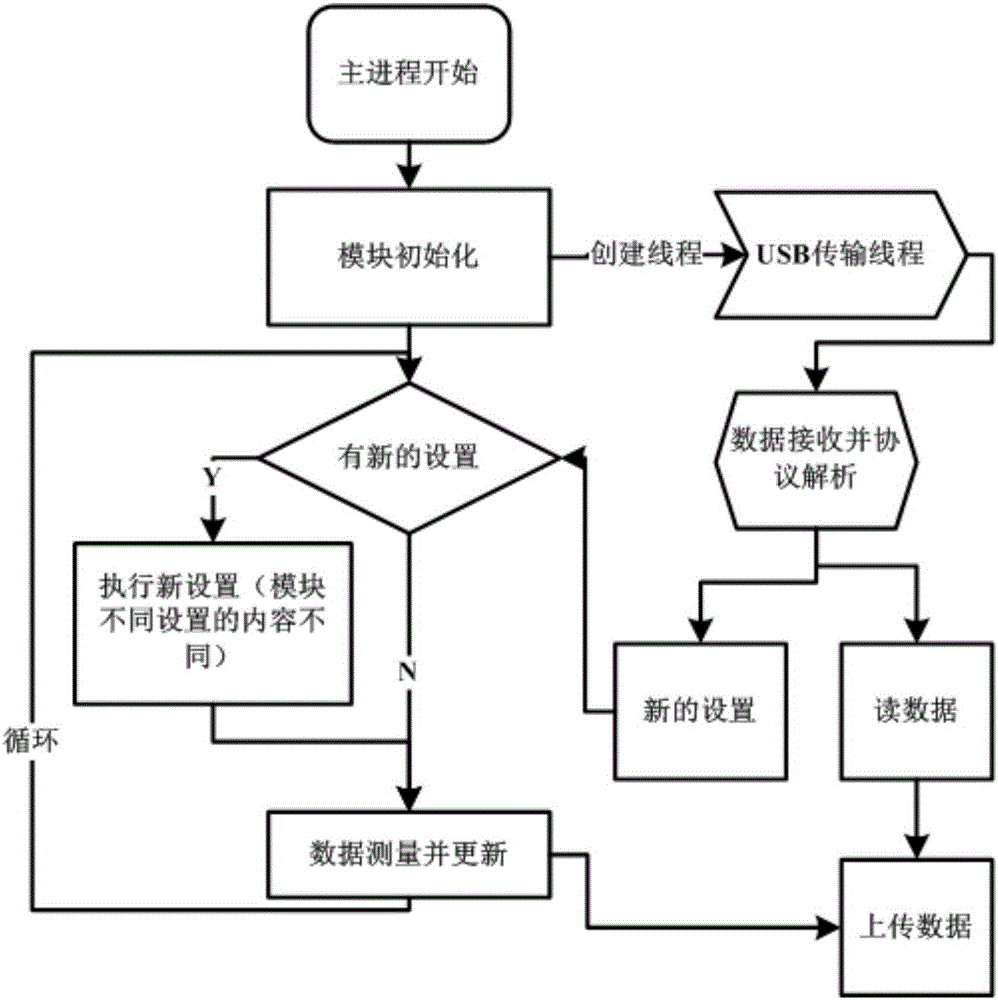

USB communication based modular function expansion method and system for digital oscilloscope

ActiveCN105868132ARealize automatic receivingAchieve interactionElectric digital data processingModularityUSB

The invention discloses a USB communication based modular function expansion method for a digital oscilloscope. The method comprises the following steps: (1) the digital oscilloscope and an external connection device are prearranged; (2) a supporting USB device interface and a USB device drive are arranged, and an identification code of the external connection device is preset; (3) a command and data are packaged; (4) initialization is performed, a USB event monitoring thread is established, and whether a USB accessing event or a USB pulling out event happens is judged; if the USB accessing event happens, the type of the external connection device is judged; if the USB pulling out event happens, the external connection device of which the USB is pulled out is interpreted, and a marker of the device is reset; (5) after the type external connection device is determined, the external connection device is initialized, and the marker of the external connection device is set, a host process judges the marker and jumps to a corresponding operation interface, and data are received and displayed; a USB transmission thread is established for receiving data and analyzing communication protocols, new setting is performed, and data are read; (6) whether new setting is performed is judged; (7) the data are uploaded. The invention further discloses a function expansion system.

Owner:UNI TREND TECH (CHINA) CO LTD

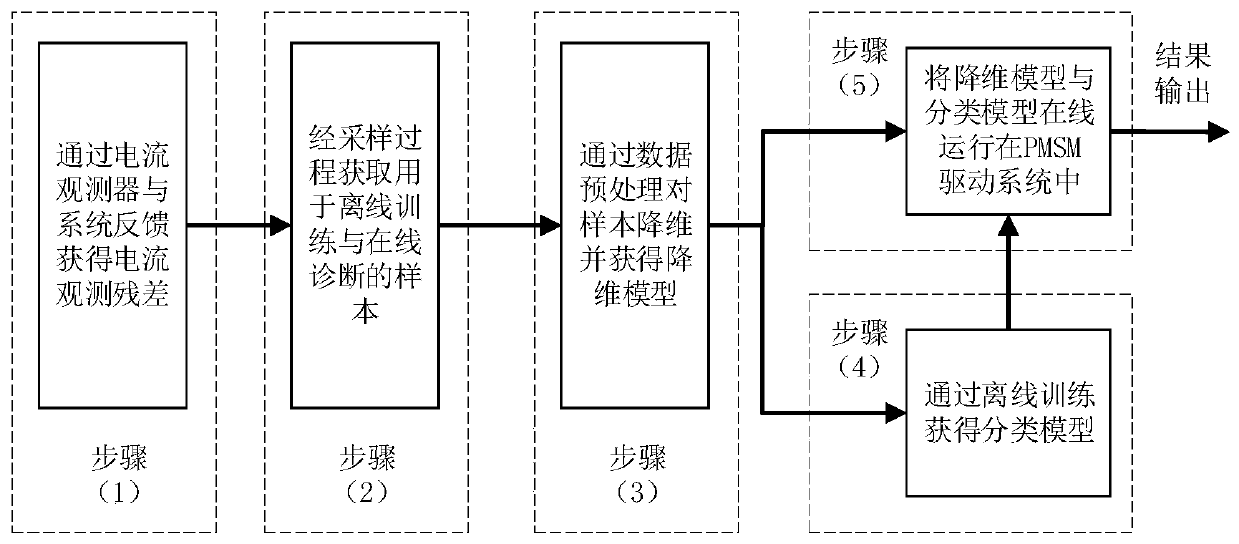

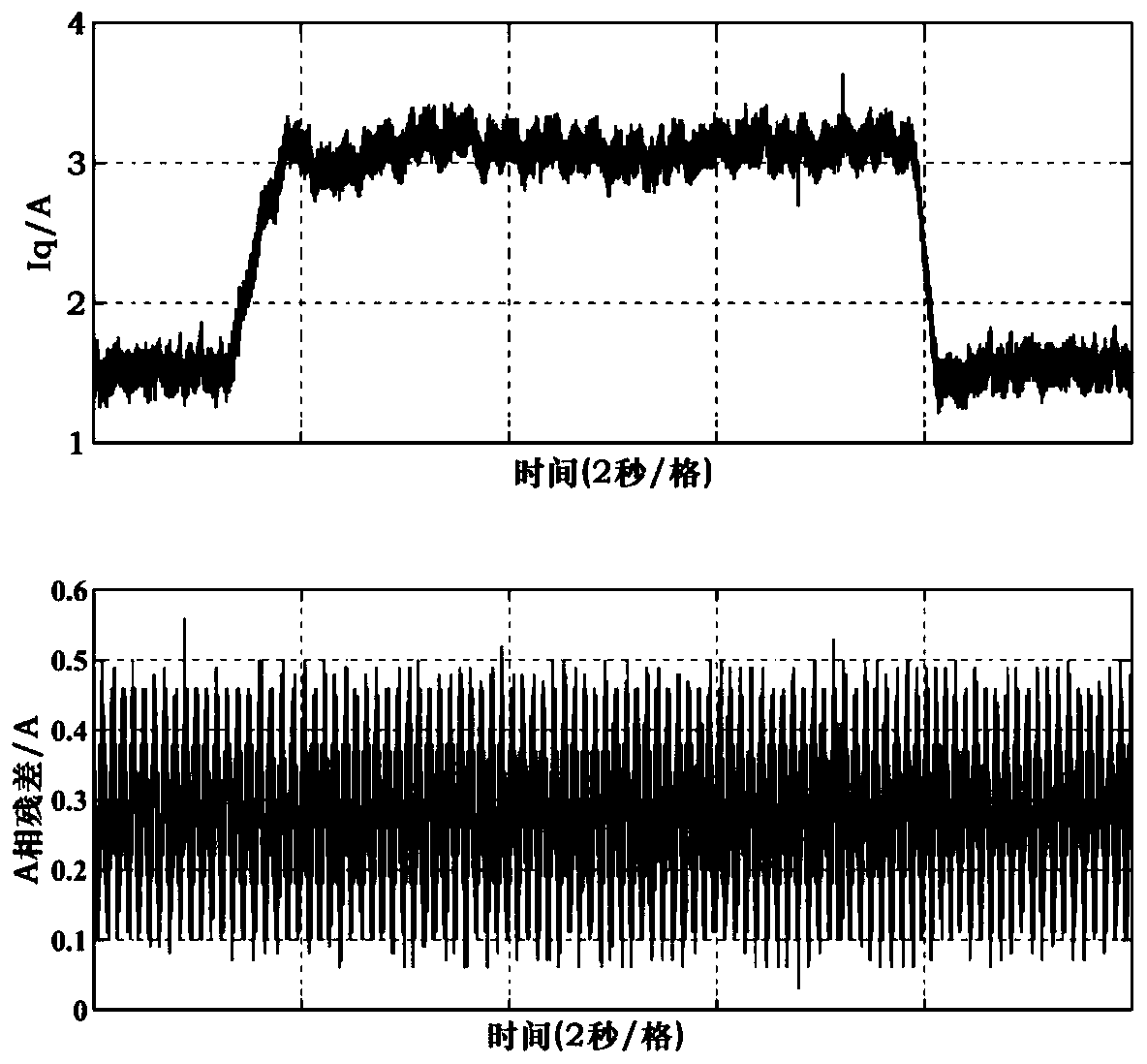

PMSM drive system inverter open-circuit fault online diagnosis method

ActiveCN111551872AAdd hardwareDoes not affect drive controlContinuity testingData dimensionality reductionFailure diagnosis

The invention relates to a PMSM drive system inverter open-circuit fault online diagnosis method, which can carry out online fault diagnosis and positioning on various inverter open-circuit faults. The method comprises the steps: introducing a Luenberger observer to track a PMSM three-phase current so as to obtain a three-phase current observation residual error as a fault diagnosis basis; designing a sampling strategy, and obtaining an original sample set for training; in offline training, introducing a principal component analysis method to preprocess an original sample set to obtain a datadimension reduction model, and then acquiring a classification model by training a support vector machine; finally, operating the dimension reduction model and the classification model in a driving system, and achieving the online diagnosis and positioning of faults. According to the method, hardware equipment is not added, and driving control is not affected; meanwhile, the method is not affectedby load and model parameter changes; through machine learning of actual working conditions, the method does not depend on a diagnosis basis set manually, and the possibility of misdiagnosis is reduced.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

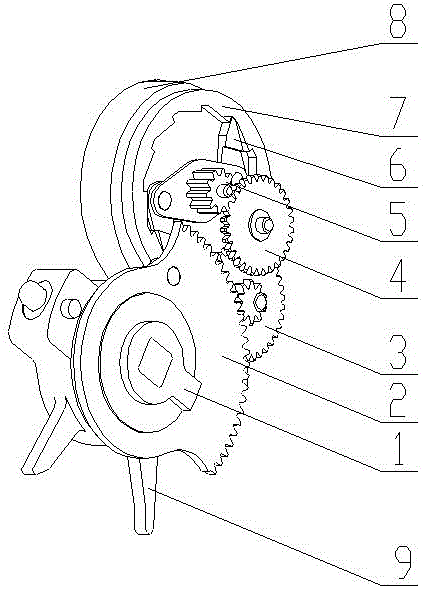

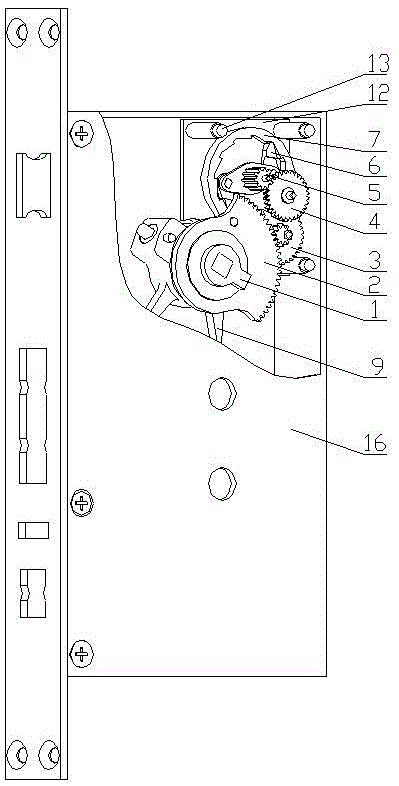

Power generation device in lock body of door lock

PendingCN105649899ACompact structureSmall sizeFrom muscle energyNon-mechanical controlsClutchElectric generator

A power generation device in a lock body of a door lock is characterized by comprising an input shaft, an input gear, a gearing-up mechanism, a micro generator, a clutch rotating shaft component and a lock body casing. Except the lock body casing, other parts are installed in the lock body, a sector gear is installed on the input shaft to rotate together with the input shaft, the input shaft and an outer door handle are coaxial, and the input shaft is driven by the outer door handle. An outside mechanism controls connection relations of the clutch rotating shaft component and the input shaft by controlling a clutch pin on the clutch rotating shaft component. When a door does not need to be opened, the outer door handle drives the input shaft to rotate, drives the generator is generate electricity and does not drive the clutch rotating shaft component to rotate. When the door needs to be opened, the outer door handle drives the input shaft to rotate, drives the generator to generate electricity and drives the clutch rotating shaft component to rotate.

Owner:北京摇光智能科技有限公司

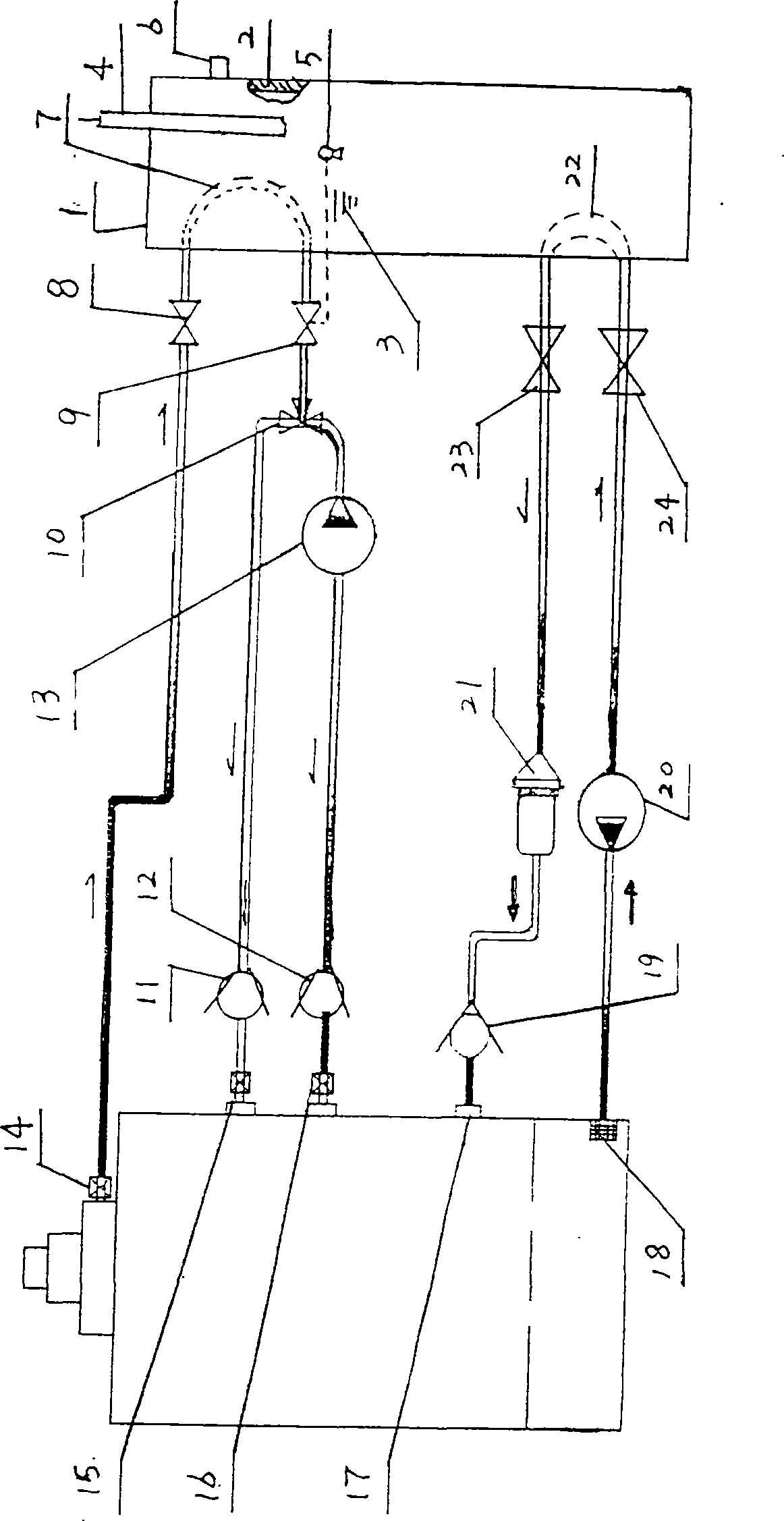

Process for recovering liquefied petroleum gas from dry distillation tail gas of oil shale

InactiveCN101597506ASave engineering investmentReduce energy consumptionGaseous fuelsSpecial form destructive distillationCombustionOil shale gas

The invention discloses an improved comprehensive utilization process for producing oil by oil shale by graded dry distillation as well as recovering and extracting liquefied petroleum gas (LPG) from dry distillation tail gas, which is the improvement on the prior process, namely a gas full-cycle oil shale graded dry distillation process and a device thereof. Oil gas produced from the oil shale through dry distillation passes through a water scrubbing tower, an electrostatic oil trap and an oil-water separation tank to produce the shale oil; and the dry distillation tail gas utilizes the process to recover the LPG, and residual cold gas enters a circulating gas heating furnace. The process has the advantages that the process recovers the LPG, reduces a calorific value of the gas for combustion when the oil shale has lower quality, possibly cannot meet the heat supply demand of the heating furnace, and can reserve an interface on the heating furnace through which the shale oil is returned to combust to supplement the heat. The process has high comprehensive utilization degree, fully recovers the LPG in the dry distillation tail gas, and increases the gain.

Owner:DALIAN UNIV OF TECH

Palm print authentication-based car starting method

ActiveCN104228767AAchieve normal startupDoes not affect the designAnti-theft devicesCharacter and pattern recognitionComputation complexityPalm print

The invention relates to the field of cars, in particular to a palm print authentication-based car starting method. The palm print authentication-based car starting method provided by the invention comprises the following steps: 1, performing collection on palm prints of a hand by using a palm print collection instrument, then, transmitting collected palm print information to a palm print processing and recognition unit, and performing preprocessing on the palm print information by the palm print processing and recognition unit; 2, performing classification authentication on the palm print information by using a field feature line segment classifier. The palm print authentication-based car starting method disclosed by the invention has the beneficial effects that discriminant authentication is performed on the palm print information by using comparatively popular nearest feature line classification, and thus, a car owner can realize car starting only by inputting the own palm print information and passing authentication, and other people cannot start the car; the problems of extension inaccuracy and computational complexity of a nearest feature line are also improved.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL +1

HTTP web page dynamic outputting method and system

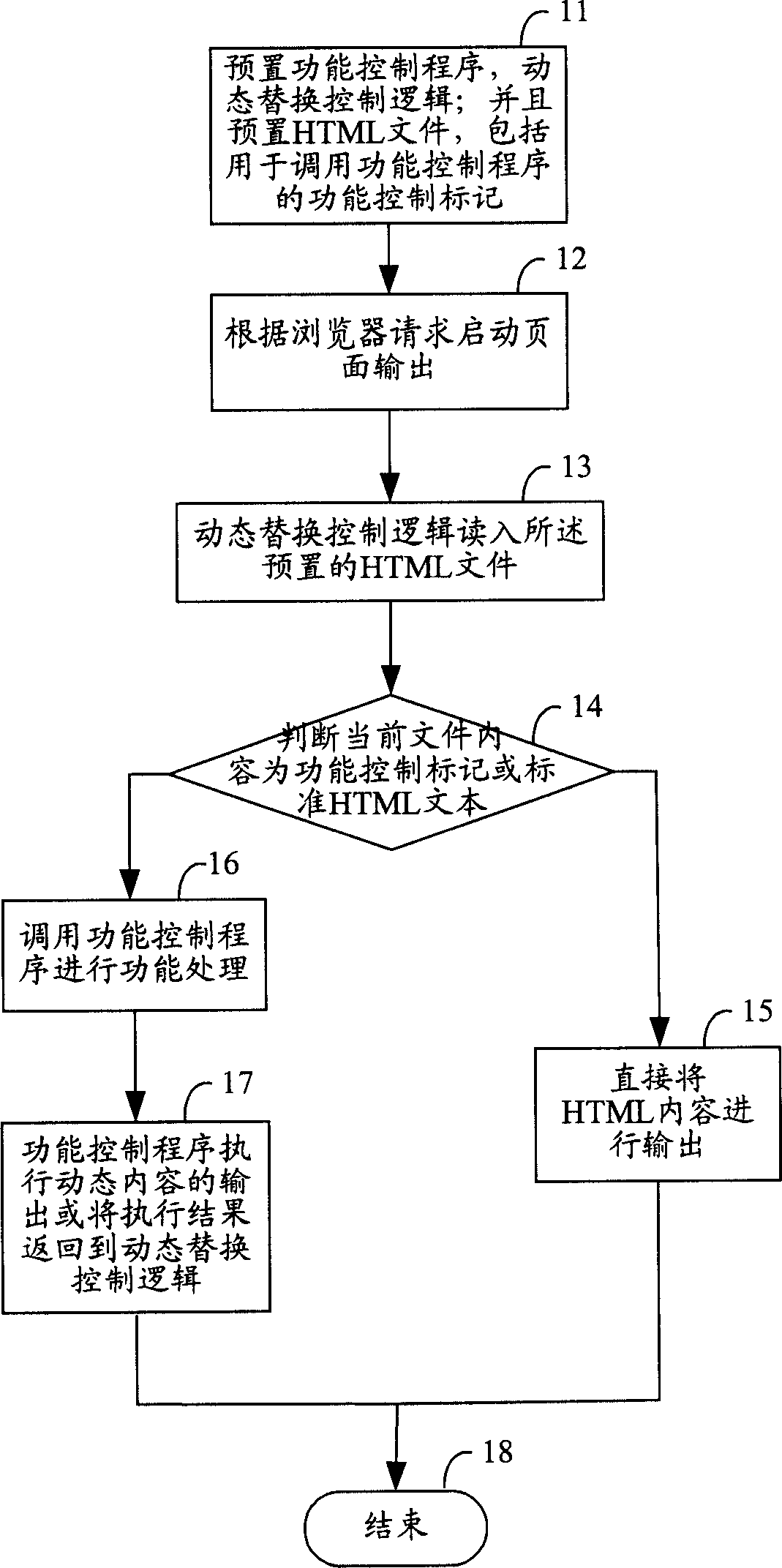

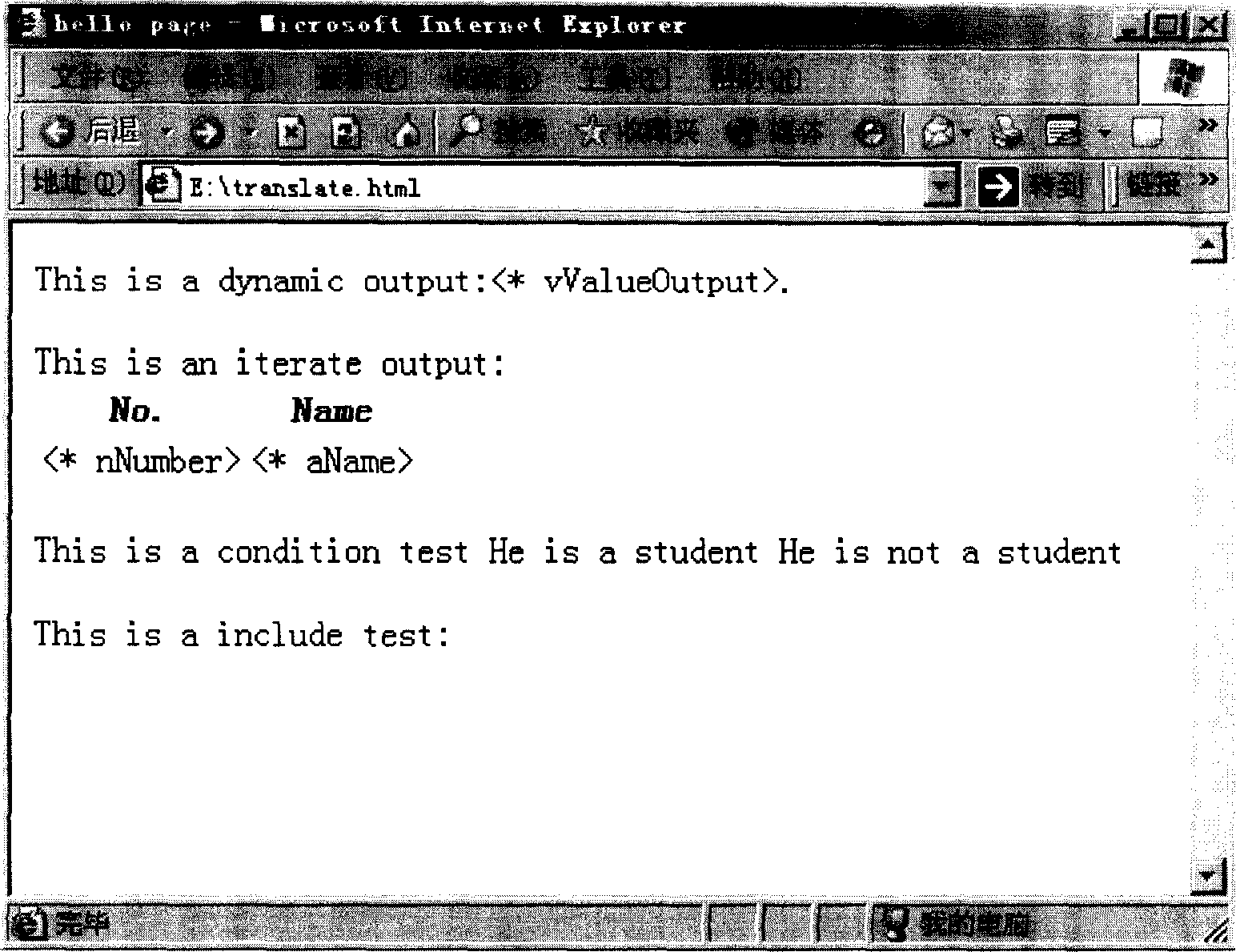

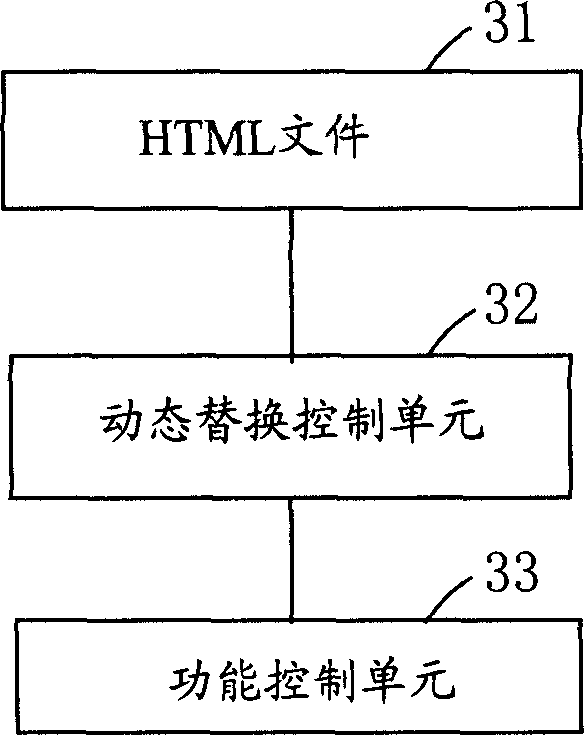

InactiveCN1741018AImprove development efficiencyDoes not affect the designSpecial data processing applicationsComputer scienceControl logic

The present invention relates to a method for making HTTP web page dynamic output and its system. Said method includes the following steps: 1). Presetting HTML file, including predefined function control mark correspondent to dynamic contents; presetting function control program, and dynamic substitution control logic for semantically processing the described mark and calling function control logic; 2). Dynamic substitution control logic can read in HTML file, for function control mark in the file the dynamic substitution control logic can call function control program to make operation or dynamic content output; and 3). Dynamic substitution control logic can output the static contents in HTML file.

Owner:北京华三通信技术有限公司

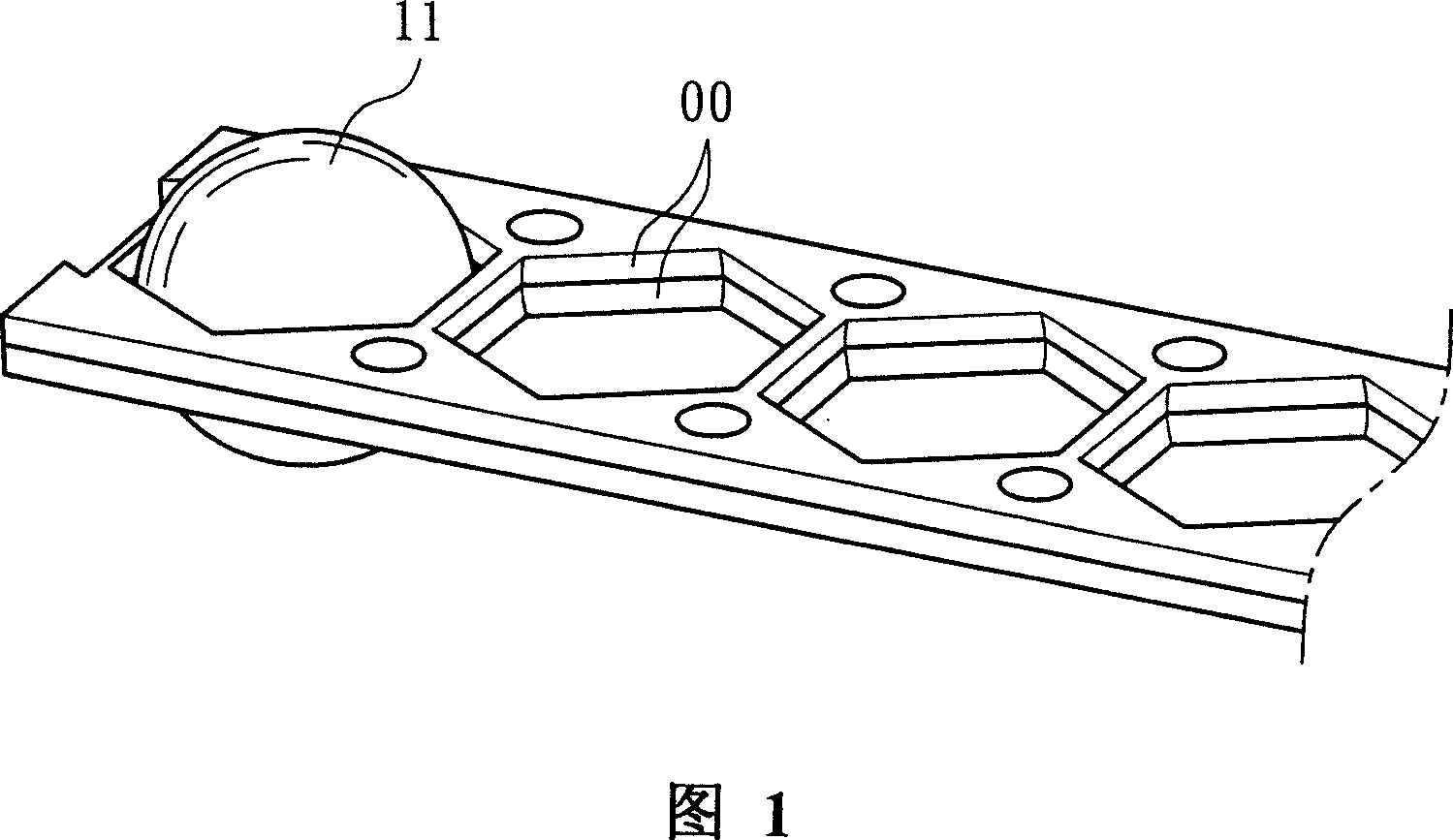

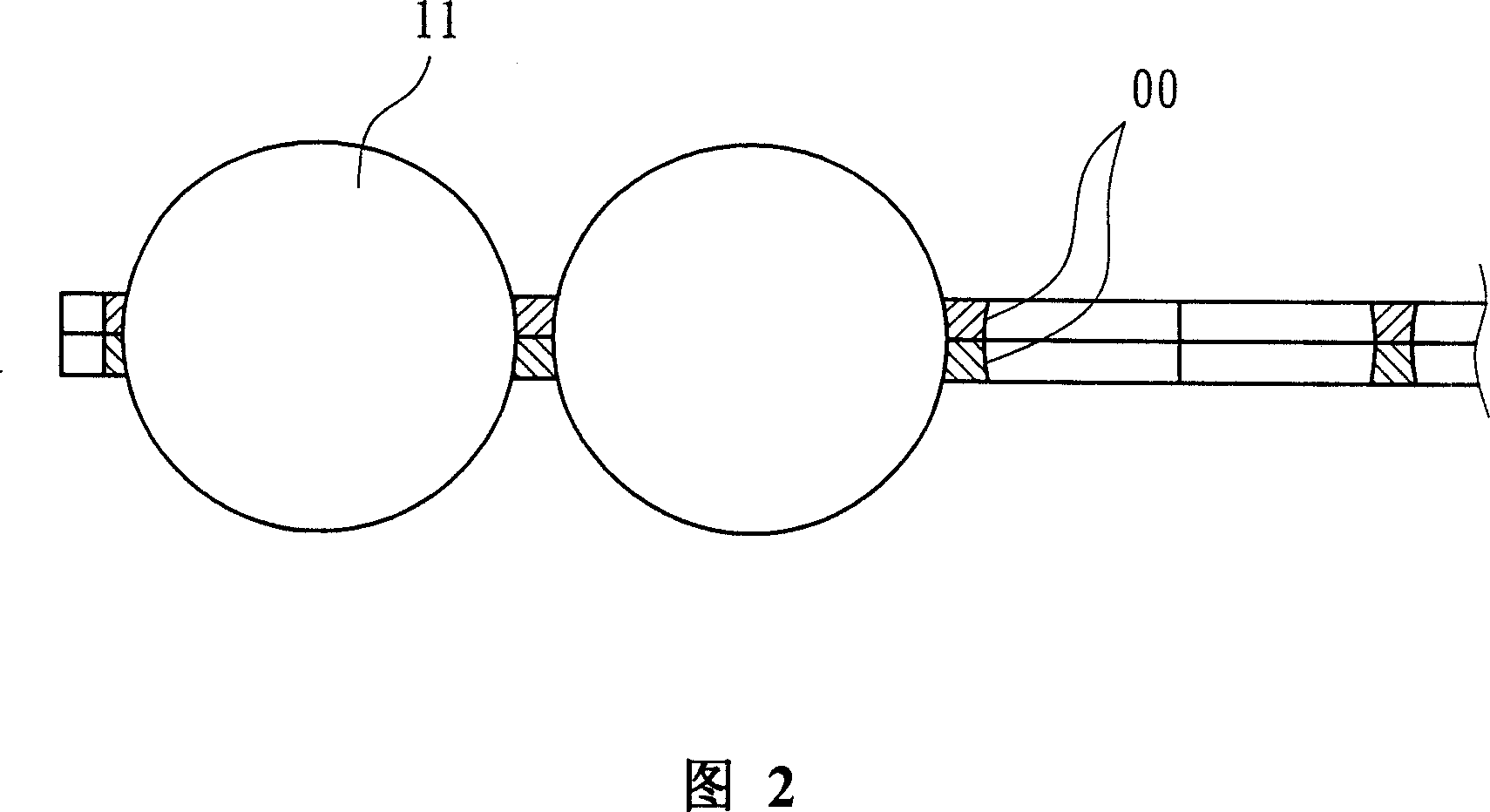

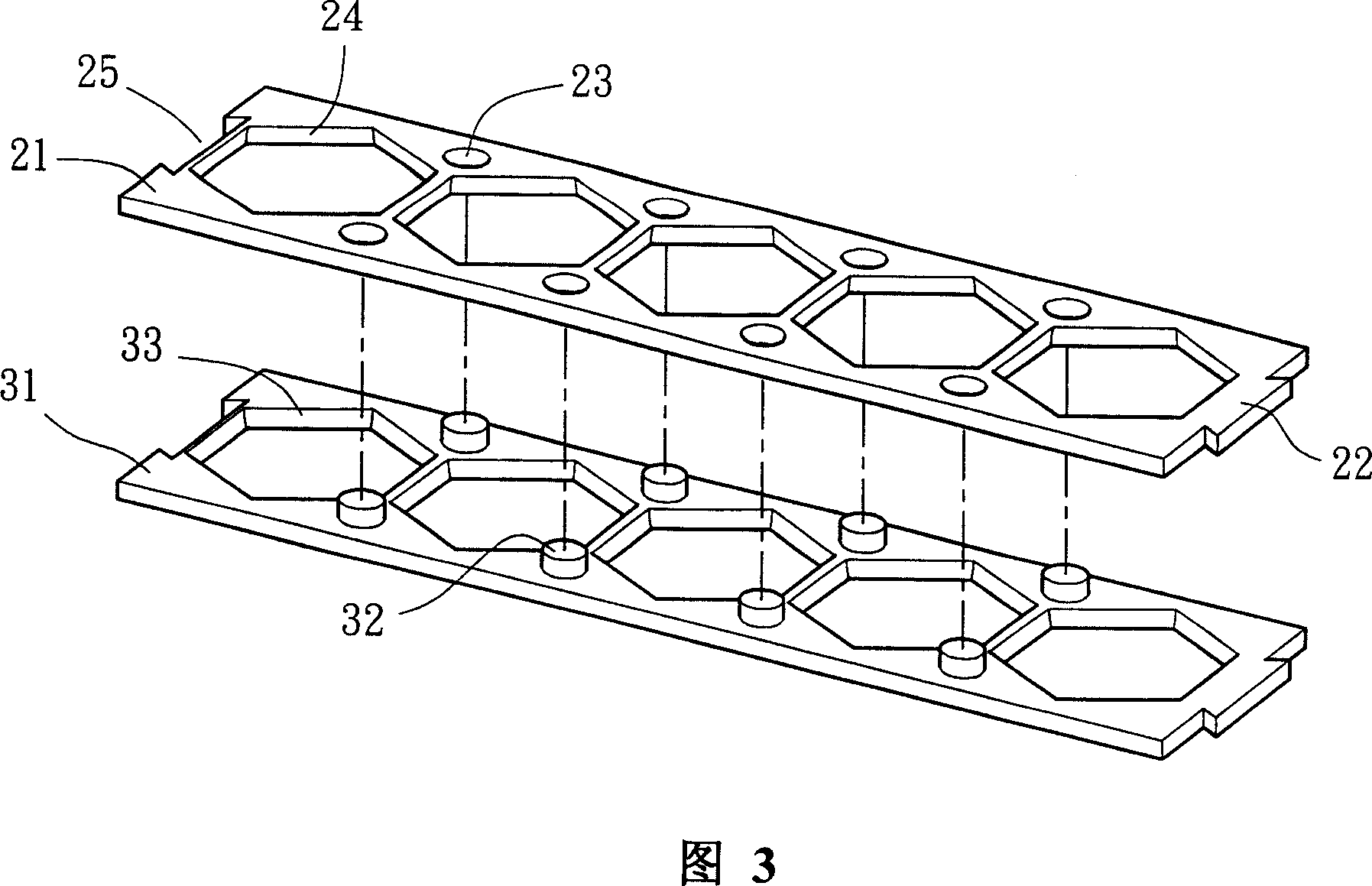

Rolling membrane retaining module set

InactiveCN1924383ALower development cost priceExtend your lifeLinear bearingsBearing componentsMechanical engineeringMembrane configuration

This invention discloses one roller parts keeping mode set, which is characterized by the following: setting upper and down thin board combination parts with isolation space by use of beehive structure as rolling parts for effective positioning without over friction limitation due to the beehive structure on rolling parts.

Owner:HIWIN TECH