Drawing method for polycrystalline silicon layer device auxiliary graphs

A technology of polysilicon devices and auxiliary graphics, applied in instruments, special data processing applications, electrical digital data processing, etc., can solve the problems of PO-DAF missing addition, time and resource loss, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

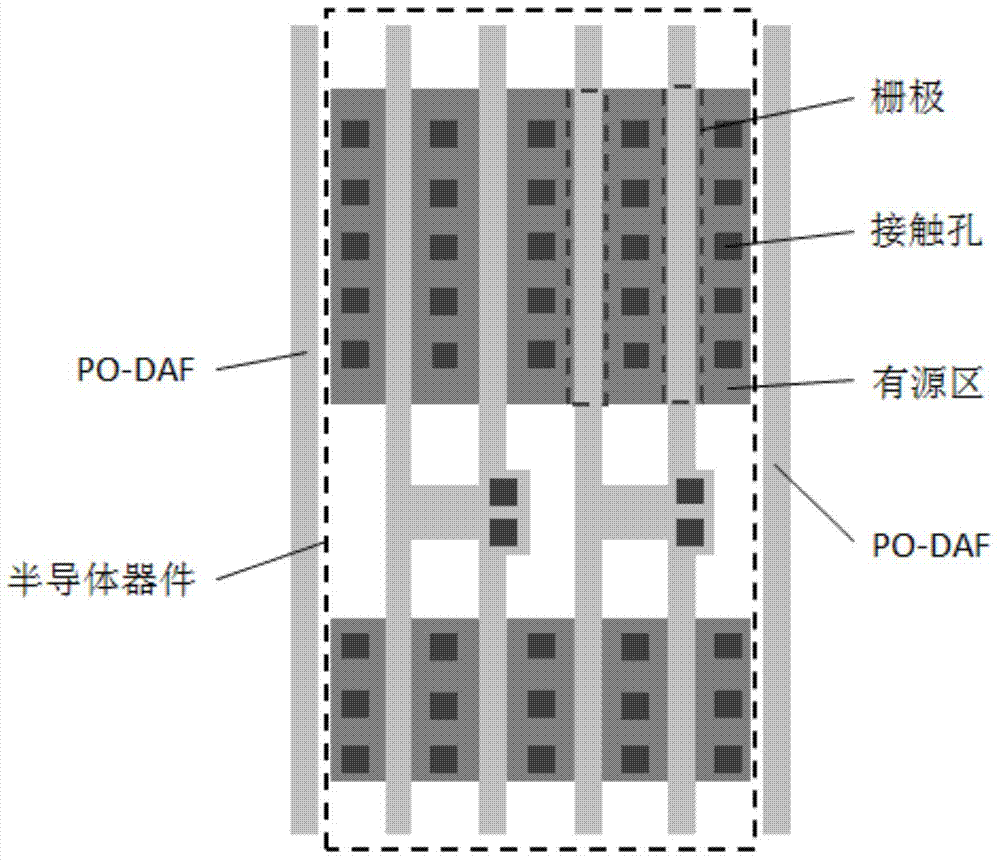

[0031] It should be noted that the present invention proposes a method for drawing auxiliary graphics of polysilicon layer devices, which is Figure 1 After transmission to the semiconductor manufacturing company, at this stage, technicians may find that PO-DAF is missing due to design negligence, and can perform compensation and correction processing on the polysilicon layer device pattern on the spot.

[0032] The specific embodiment of the present invention will be further described in detail below in conjunction with the accompanying drawings.

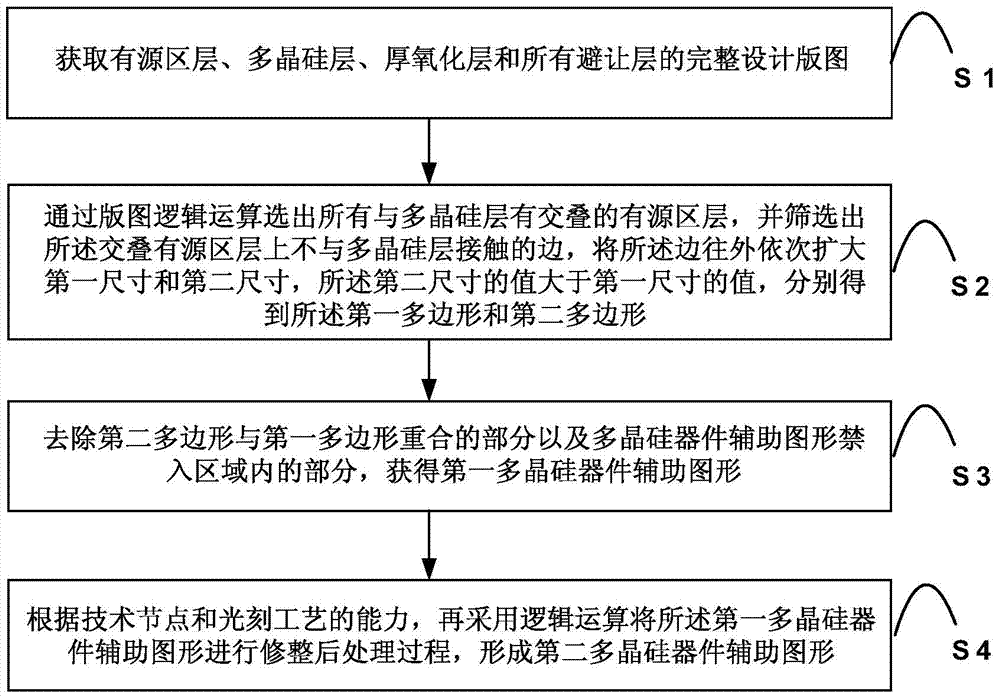

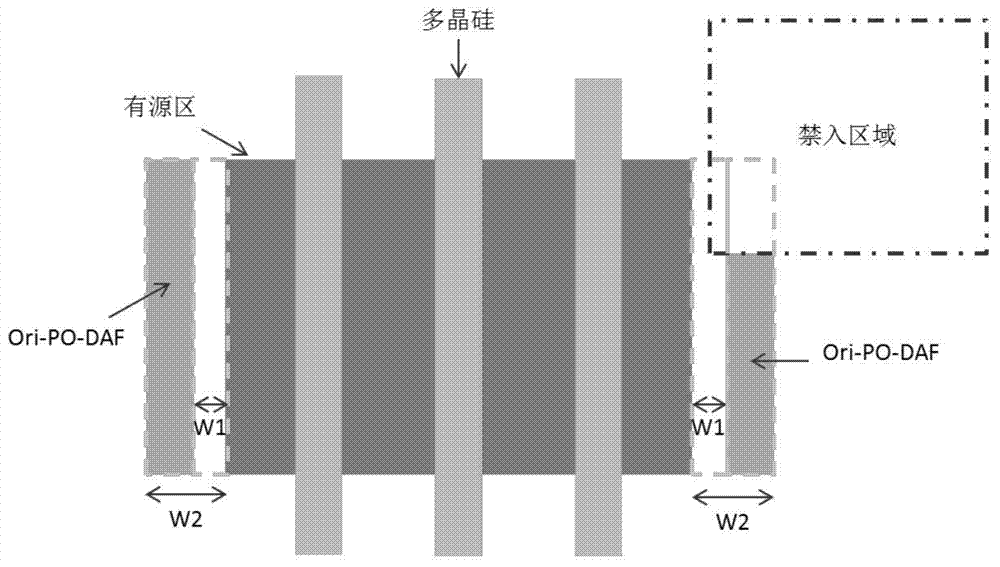

[0033] see figure 2 and image 3 , figure 2 Shown is a schematic flow chart of the polysilicon layer device auxiliary pattern drawing method of the present invention. As shown in the figure, in the embodiment of the present invention, the method specifically includes the following steps:

[0034] Step S1: Obtain the complete design layout of the active area layer (AA), polysilicon layer (PO), thick oxide layer (MOX) and all k...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More