System and method for verifying embedded memory controller based on assertion

A storage controller and verification system technology, applied in instruments, special data processing applications, electrical digital data processing, etc., can solve the problem of difficulty in obtaining an accurate judgment on the completeness of logic simulation verification, the increase in logic simulation time and labor costs, and simulation testing. The huge amount of incentive data and other problems can shorten the verification and debugging time, improve the functional coverage, and reduce the labor cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

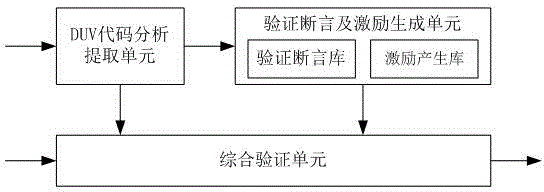

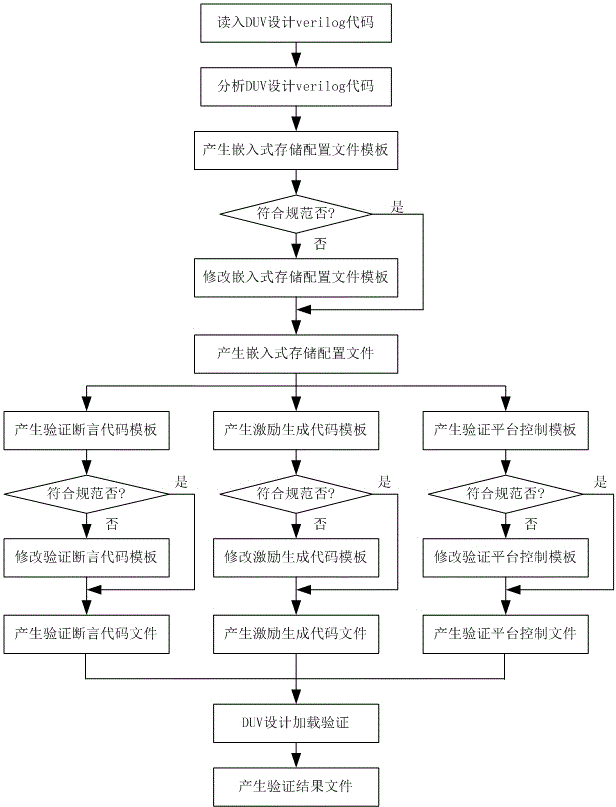

[0013] The assertion-based embedded storage controller verification system described in this embodiment has a structure including: (1) DUV code analysis and extraction unit, (2) verification assertion and stimulus generation unit, (3) comprehensive verification unit; here, DUV means Verified design; Among them, (1) DUV code analysis and extraction unit: adopts a structured code analysis method to complete the comprehensive coverage of the DUV design Verilog code, and efficiently extract the embedded storage information and controller protocol information; ( 2) Verification assertion and incentive generation unit: Based on the storage controller verification assertion library and incentive generation library, as well as embedded storage configuration information, the verification assertion code and incentive generation code for storage controller logic verification are generated; (3) Comprehensive verification unit: According to the configuration information of embedded storage,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More