Over-etching rate test structure, forming method thereof and over-etching rate measurement method

A technology of testing structure and over-etching, which is applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve problems such as cumbersome process, and achieve the effect of simplifying complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

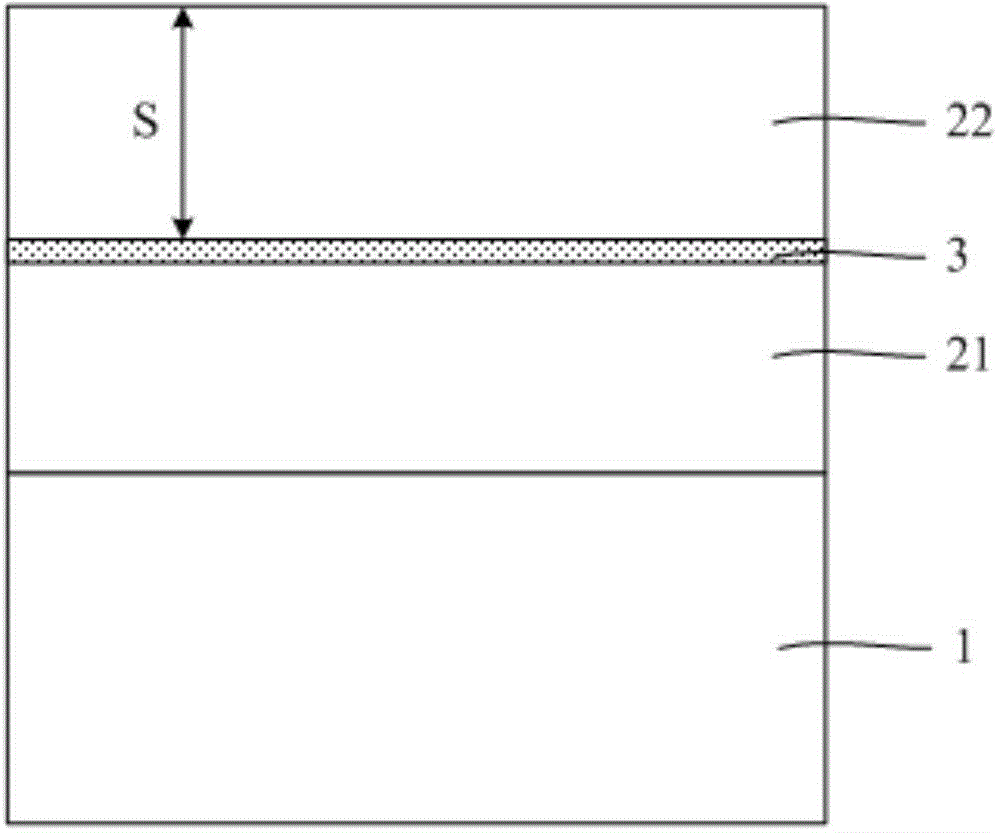

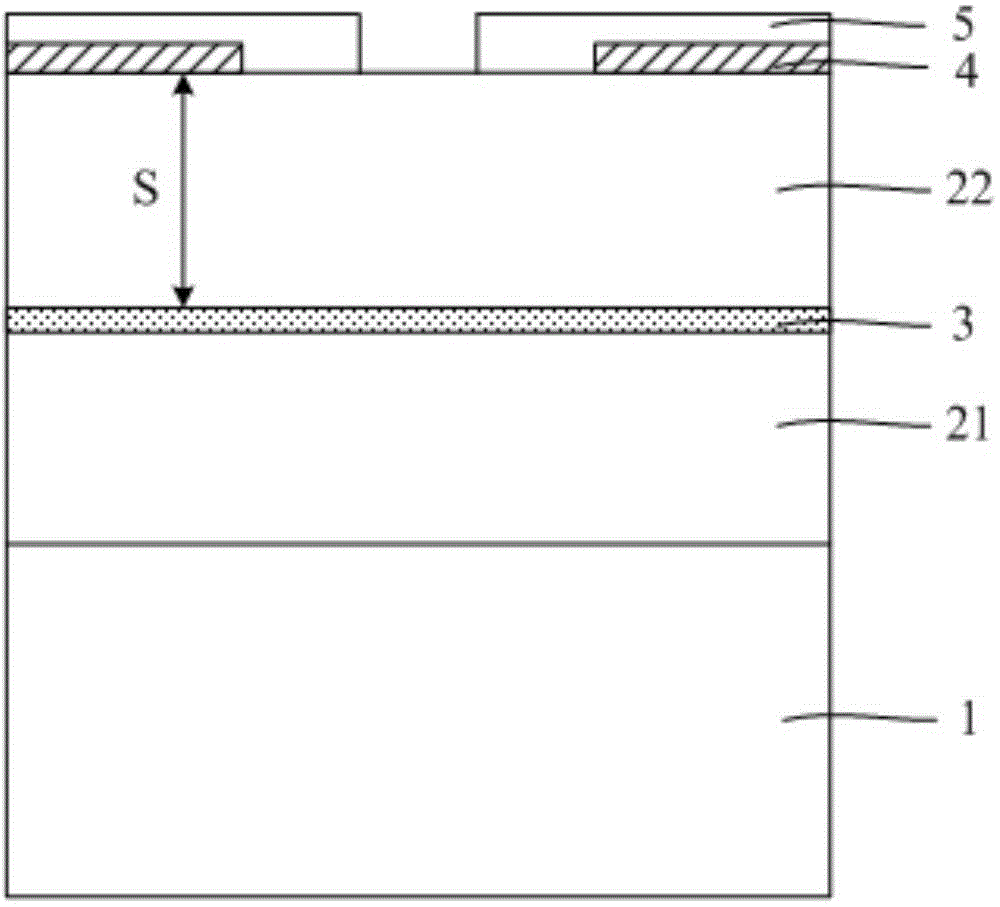

[0071] This embodiment provides a method for forming a test structure for overetching rate, including:

[0072] refer to Figure 7 , a substrate 110 is provided, and the substrate 110 includes a first region 111 and a second region 112 located at different positions.

[0073] The substrate 110 may be a semiconductor substrate known in the art such as a silicon substrate, a silicon germanium substrate, or the like. Semiconductor devices such as transistors, interconnection lines, and plugs may also be formed in the substrate 110 .

[0074] The substrate 110 also includes a chip area (not shown), and the first area 111 and the second area 112 are located outside the chip area.

[0075] In order to save the occupied area of the first area 111 and the second area 112 , the first area 111 and the second area 112 are in contact. Figure 7 In order to distinguish, the first area 111 and the second area 112 are separated by a straight line.

[0076] In other embodiments, the fir...

no. 2 example

[0123] This embodiment provides a test structure, refer to Figure 15 ,include:

[0124] a substrate 110, the substrate 110 comprising a first region 111 and a second region 112 at different positions;

[0125] a first interlayer dielectric layer 121 located on the first region 111;

[0126] A second interlayer dielectric layer 122 located on the second region 112, the thickness of the second interlayer dielectric layer 122 is smaller than the thickness of the first interlayer dielectric layer 121;

[0127] A first etch stop layer 131 located on the second interlayer dielectric layer 122, the upper surface of the first etch stop layer 131 is flush with the upper surface of the first interlayer dielectric layer 121;

[0128] The third interlayer dielectric layer 123 located on the first etching stop layer 131 and the first interlayer dielectric layer 121, the first interlayer dielectric layer 121, the second interlayer dielectric layer 122 and the third interlayer dielectric ...

no. 3 example

[0138] This embodiment provides a method for measuring the overetching rate.

[0139] refer to Figure 15 , providing the test structure of the overetch rate formed by the first embodiment.

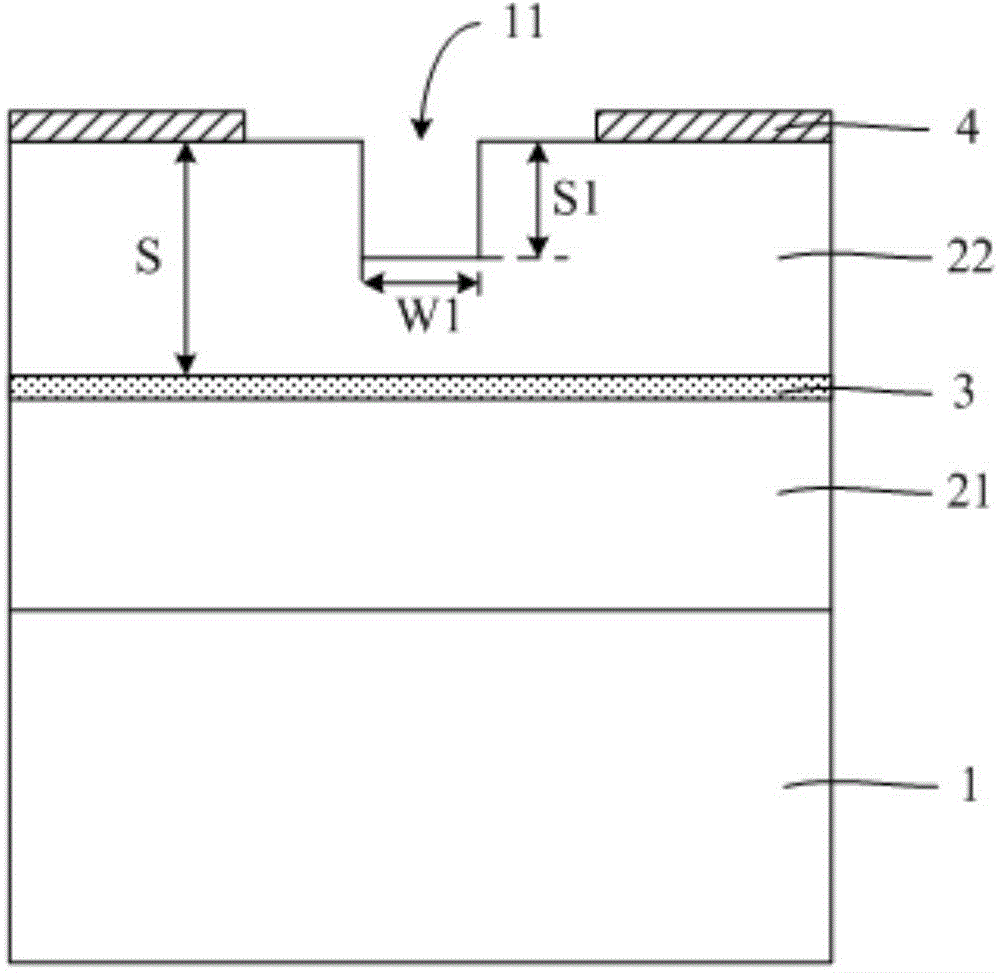

[0140] The first through hole 161 and the second through hole 162 are in the shape of a truncated cone with a larger top and a smaller bottom.

[0141] Since the first through hole 161 is not blocked by the first etch stop layer 131 , it is etched into the first interlayer dielectric layer 121 , and the depth of the bottom of the first through hole 161 entering the first interlayer dielectric layer 121 is S3 .

[0142] Since the bottom of the first through hole 161 will be etched into the first interlayer dielectric layer 121, the bottom of the first through hole 161 will not increase due to lateral etching, and the diameter of the bottom of the first through hole 161 remains b1 . Since the top opening of the first through hole 161 does not have a mask layer of a corresponding size, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com