Novel wafer-level mems chip packaging structure and packaging method

A chip packaging structure and wafer-level technology, applied in the direction of microstructure devices, manufacturing microstructure devices, microstructure technology, etc., can solve the problem of limited operable space of MEMS chips and achieve the effect of large operable space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

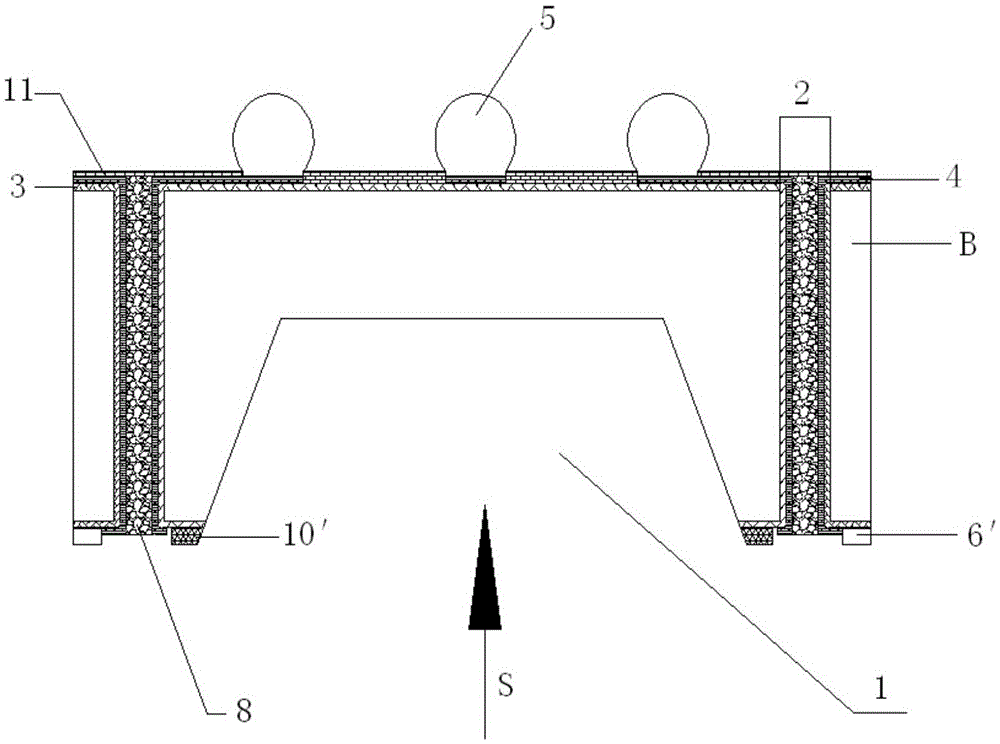

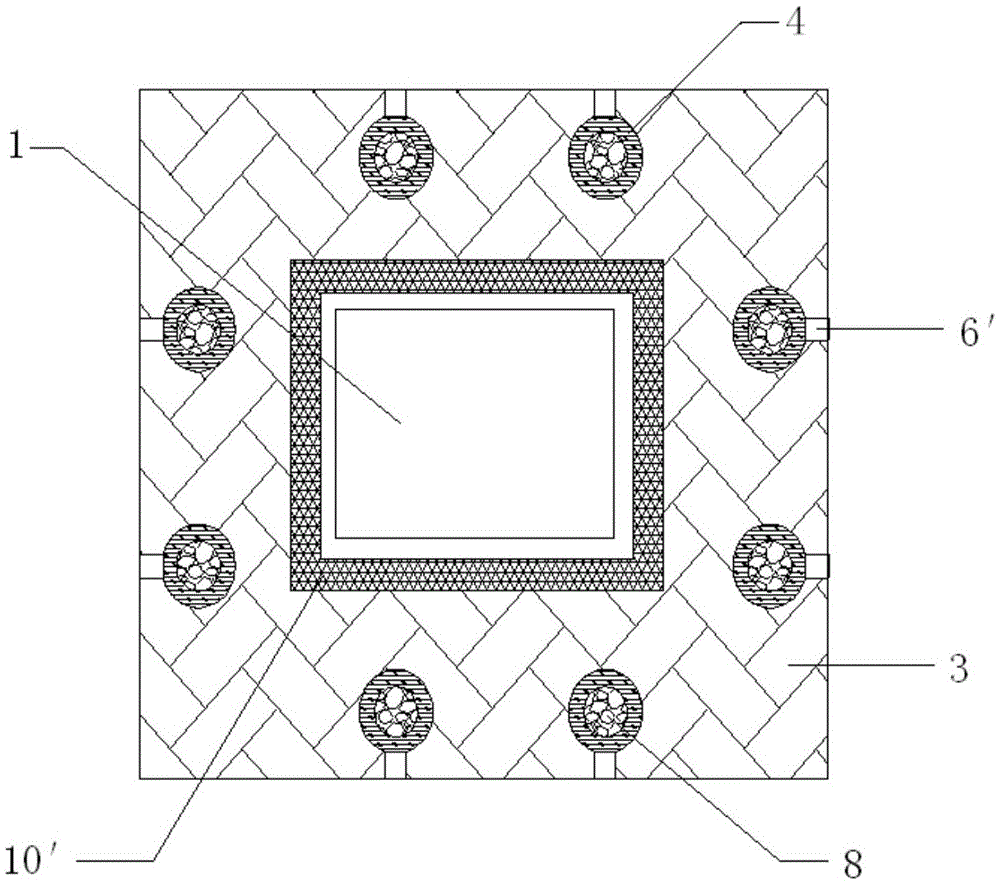

[0041] like Figure 4 As shown, a new type of wafer-level MEMS chip packaging structure, including MEMS chip A and covering silicon plate B.

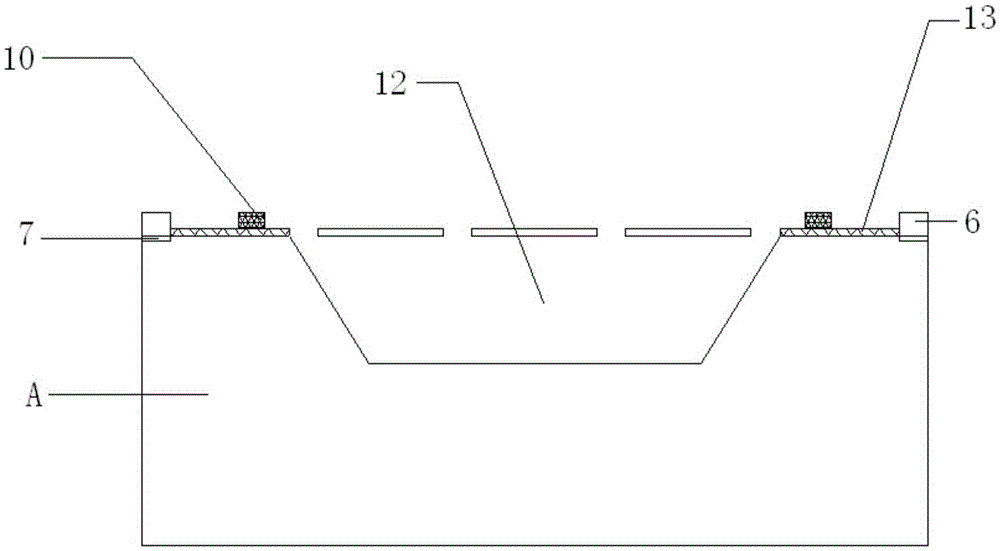

[0042] see figure 1, the front middle part of the MEMS chip has a cavity 12, and several PIN pins 7 are arranged on the front periphery of the MEMS chip, and a layer of first layer is covered on the front of the MEMS chip except the cavity and the PIN pins. Insulating layer 13, the first insulating layer is used to isolate the silicon on the MEMS chip to prevent short circuit. The material of the first insulating layer can be inorganic non-metallic material, such as silicon dioxide, or a polymer insulating material, such as photolithography Glue etc. The first insulating layer is provided with a first sealing ring 10 with a set width and a set height located on the periphery of the cavity, and a first metal bump 6 is made on each of the PIN pins; usually the first The width of a sealing ring is more than 10 μm, and the first sealing ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More