Hardware accelerator and chip

A hardware accelerator and accelerator technology, applied in the field of communication, can solve the problems of complex communication process, communication system errors, communication systems cannot affect each other, etc., to avoid mutual influence and achieve the effect of load balancing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The technical solutions in the embodiments of the present invention will be clearly described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

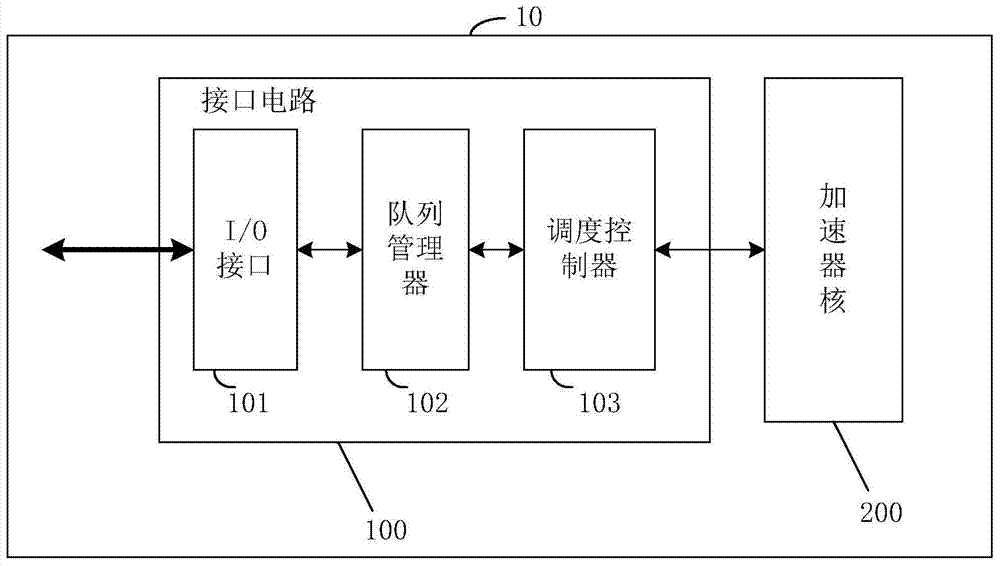

[0030] Such as image 3 as well as Figure 4 As shown, Embodiment 1 of the present invention provides a hardware accelerator 10, including: an interface circuit 100 and an accelerator core 200 coupled to the interface circuit 100;

[0031] The interface circuit 100 includes: an input / output (I / O) interface 101, a queue manager 102, and a scheduling controller 103;

[0032] The I / O interface 101 is configured to receive a first task request, the first task request carries identifi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More