Patterned photoresist layer forming method and wafer-stage chip packaging method

A technology of photoresist layer and packaging method, which is applied in the field of semiconductors, can solve the problems of simplifying the manufacturing process, reducing manufacturing costs, disadvantages, etc., and achieve the effects of simplifying the manufacturing process, simple forming process, and reducing manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

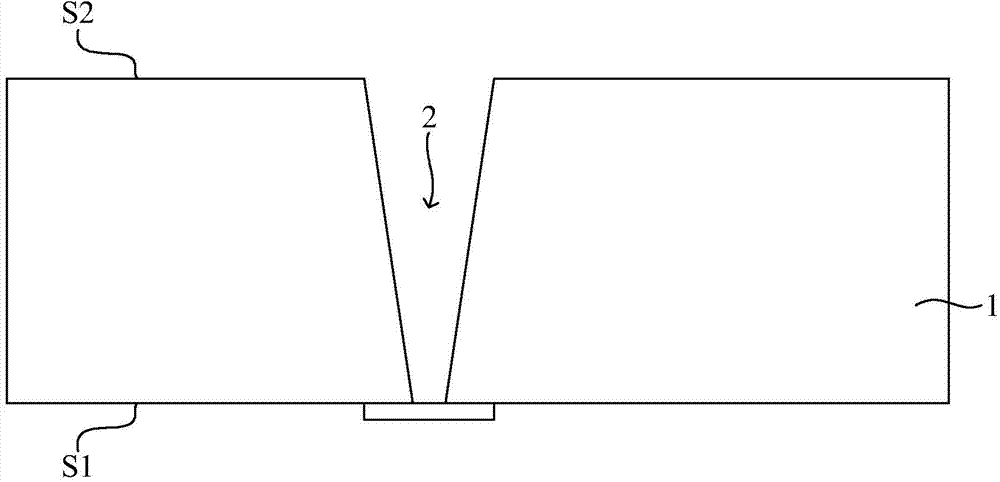

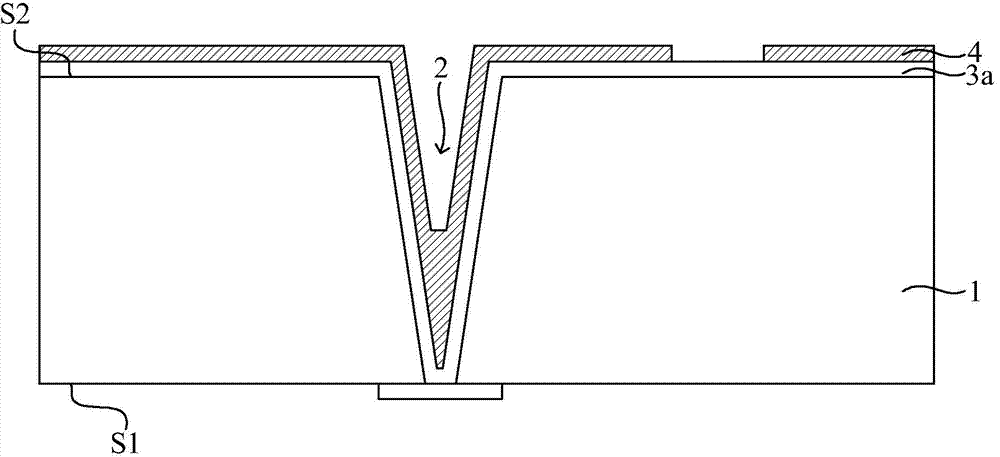

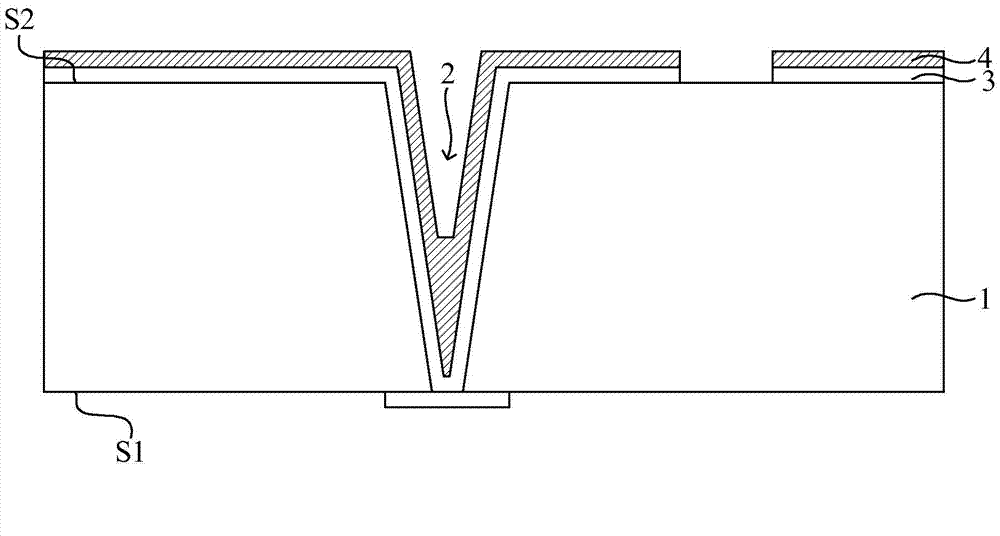

[0048] After research, it is found that in the existing wafer-level chip packaging method based on through-silicon via technology, the reason why the patterned photoresist layer located in the through-hole is difficult to remove is:

[0049] like figure 2 As shown, the patterned photoresist layer 4 is made by a photolithography process using a photoresist with the same viscosity and a high viscosity. The photolithography process includes: a glue coating step, a soft baking step after glue coating 1. An exposure step after soft baking, due to the high viscosity of the patterned photoresist layer 4, will bring the following effects: 1) the viscosity of the patterned photoresist layer 4 and the viscosity of the patterned photoresist layer 4 In direct proportion, the thickness of the patterned photoresist layer 4 is uneven, especially the patterned photoresist layer 4 filled at the bottom of the through hole 2 is relatively thick; 2) the patterned photoresist layer 4 has strong a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More