Pulse swallowing type clock synchronization circuit

A clock synchronization and pulse-swallowing technology, applied in the field of pulse-swallowing clock synchronization circuits, can solve the problems of synchronization failure and high circuit board design requirements, and achieve the effects of simplifying design, improving convenience, and reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

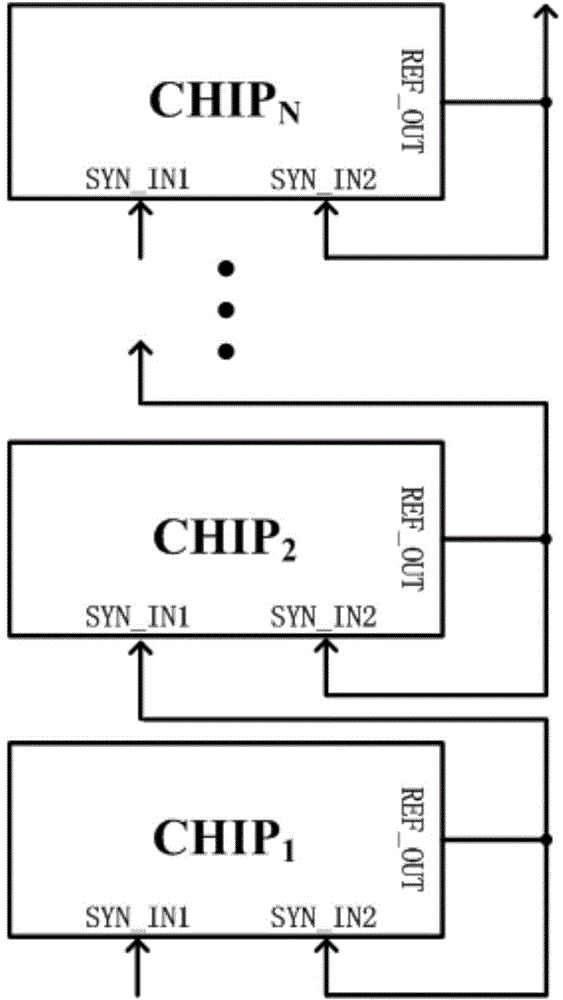

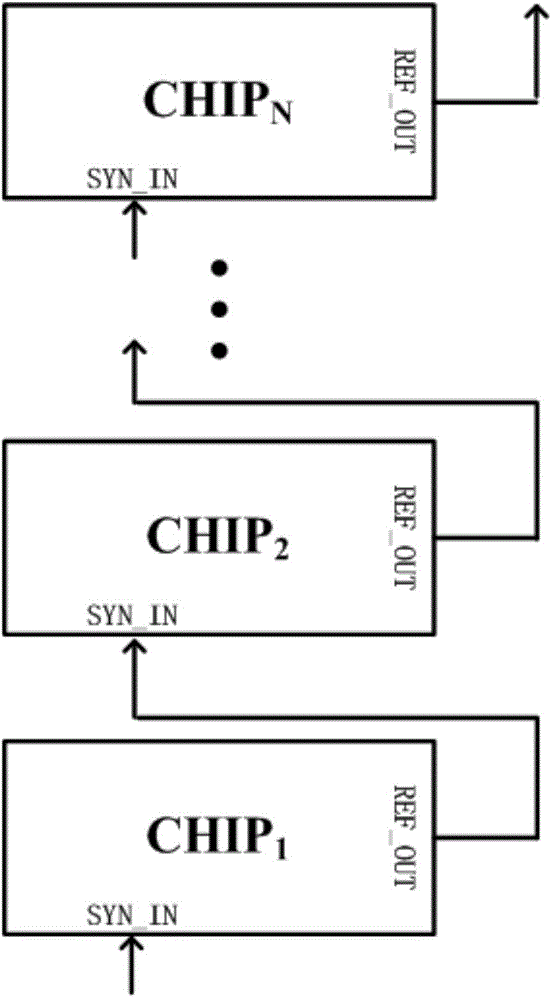

[0016] The multi-chip connection method of the improved pulse-swallowing clock synchronization circuit proposed by this scheme is as follows: figure 2 As shown, since the number of sync pulse input ports is reduced to one, compared to figure 1 With the traditional pulse-swallowing synchronization method, the number of ports of the chip and the number of interconnection lines are greatly reduced. The essence of the improved pulse-swallowing clock synchronization circuit proposed in this program is to cancel the self-loop link of the synchronization pulse signal in the traditional pulse-swallowing clock synchronization circuit, and add a step-by-step variable delay circuit inside the chip to complete similar functions. .

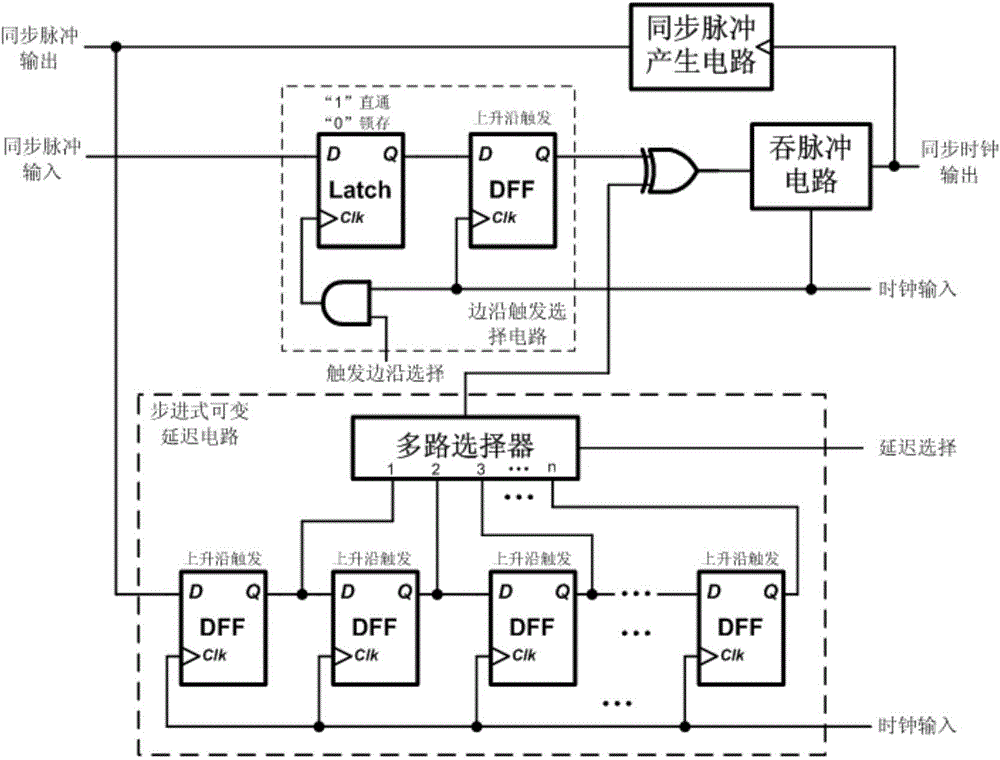

[0017] image 3 Shown, relate to a kind of pulse-swallowing type clock synchronous circuit of the present invention, comprise edge trigger selection circuit, its input end is connected with the synchronous pulse input signal that master chip produces; The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com