Sampling clock generation circuit and analog-digital converter

A technology for generating circuits and sampling clocks, which can be used in analog/digital conversion, analog/digital conversion calibration/testing, code conversion, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

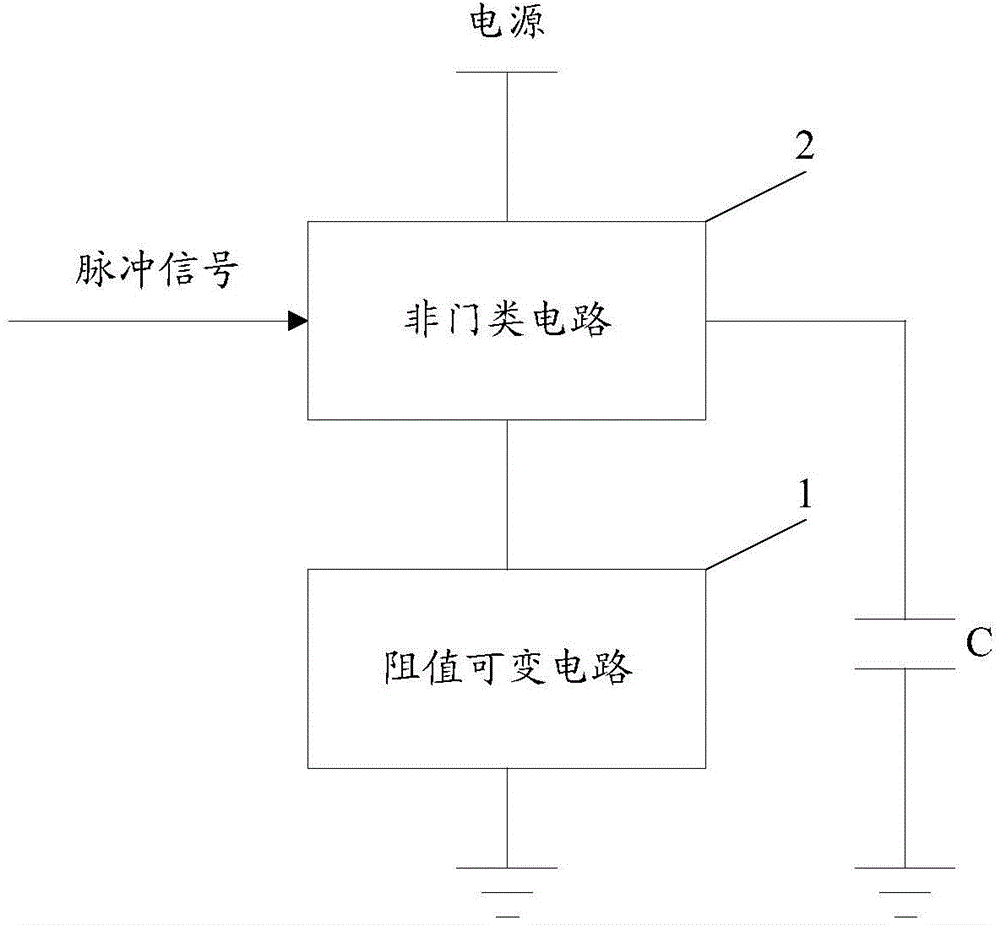

[0051] An embodiment of the present invention provides a sampling clock generation circuit, see image 3 , the sampling clock generating circuit includes a variable resistance circuit 1, a NOT gate circuit 2, and a capacitor C, and the NOT gate circuit 2 includes an input terminal, an output terminal, a power supply terminal and a ground terminal, and the receiving cycle of the input terminal of the NOT gate circuit 2 is The pulse signal of T, the output end of the non-gate circuit 2 is the output end of the sampling clock generation circuit, the output end of the non-gate circuit 2 is connected to one end of the capacitor C, the other end of the capacitor C is grounded, and the power terminal of the non-gate circuit 2 is connected to The power supply, the ground terminal of the NOT circuit 2 is connected to one end of the variable resistance circuit 1, and the other end of the variable resistance circuit 1 is grounded.

[0052] Among them, see Figure 4 , the non-gate circui...

Embodiment 2

[0063] An embodiment of the present invention provides a sampling clock generating circuit. The variable resistance circuit of this embodiment is implemented by using a field effect transistor and a strobe switch. Refer to Figure 7a or Figure 7b , the sampling clock generating circuit includes a variable resistance circuit 1, a NOT gate circuit 2, and a capacitor C, and the NOT gate circuit 2 includes an input terminal, an output terminal, a power supply terminal and a ground terminal, and the receiving cycle of the input terminal of the NOT gate circuit 2 is The pulse signal of T, the output end of the non-gate circuit 2 is the output end of the sampling clock generation circuit, the output end of the non-gate circuit 2 is connected to one end of the capacitor C, the other end of the capacitor C is grounded, and the power terminal of the non-gate circuit 2 is connected to The power supply, the ground terminal of the NOT circuit 2 is connected to one end of the variable resist...

Embodiment 3

[0114] The embodiment of the present invention provides a sampling clock generation circuit, which is different from the second embodiment in that the variable resistance circuit of this embodiment is realized by using one-to-one corresponding resistors and strobe switches, and each resistor corresponds to each The branches after the strobe switches are connected in series are connected in parallel.

[0115] Specifically, such as Figure 12 As shown, the variable resistance circuit 1 may include n resistors R1201-R(1200+n) and n third gating switches K(1201+n) corresponding to the n resistors R1201-R(1200+n) n)-K(1200+2*n), the resistance values of each resistor are different, and each third selection switch includes an input terminal, an output terminal and a control terminal. The branches formed by each resistor in series with the corresponding third select switch are connected in parallel between the ground terminal of the NOT circuit 2 and the ground. The control termi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More