TSV multi-layer chip bonding method

A multi-layer chip and bonding technology, which is applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as large local stress of fillers, chip stress damage, micro cracks, etc., to avoid the risk of cracks, good The effect of protection, avoiding damage and destruction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

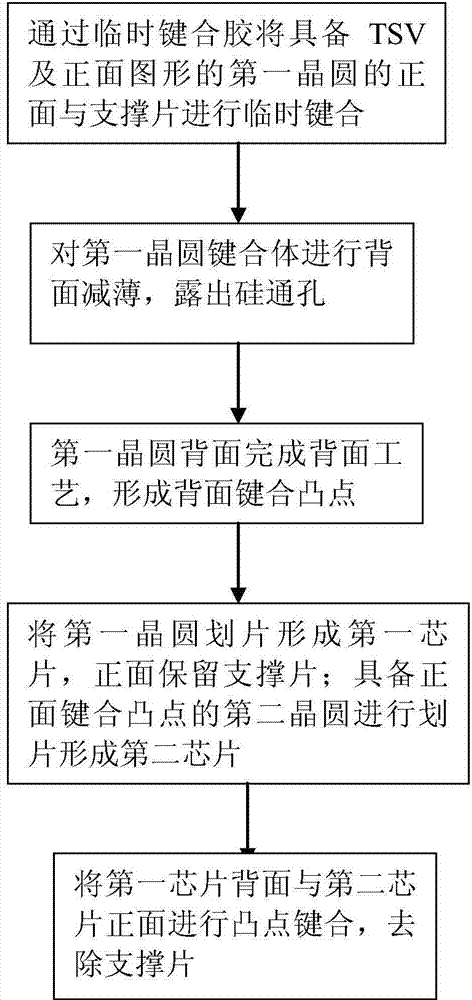

[0037] The present invention provides a kind of TSV multi-layer chip bonding method, and this preferred example is described with two-layer chip and chip bonding method as example, as figure 1 As shown, the method includes: making graphics and bumps on the front of the first wafer, temporarily bonding the front to the support sheet; forming graphics and bonding bumps on the back of the first wafer; cutting the first wafer Round to obtain the first chip, the front of the first chip has a support sheet, and the back has bonding bumps; the second wafer with bumps on the surface is diced to form the second chip; the back bumps of the first chip are combined with the second wafer The front bumps of the two chips are bonded, and the front support sheet of the first chip is removed to obtain a two-layer bonded body between the TSV chip and the chip with the bumps.

[0038] Specifically, the following steps are included,

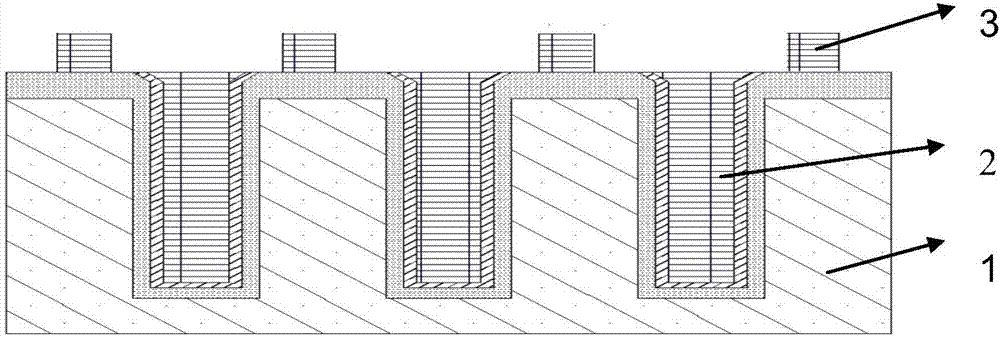

[0039] Step 1, such as image 3 As shown, the first wafer fo...

example 2

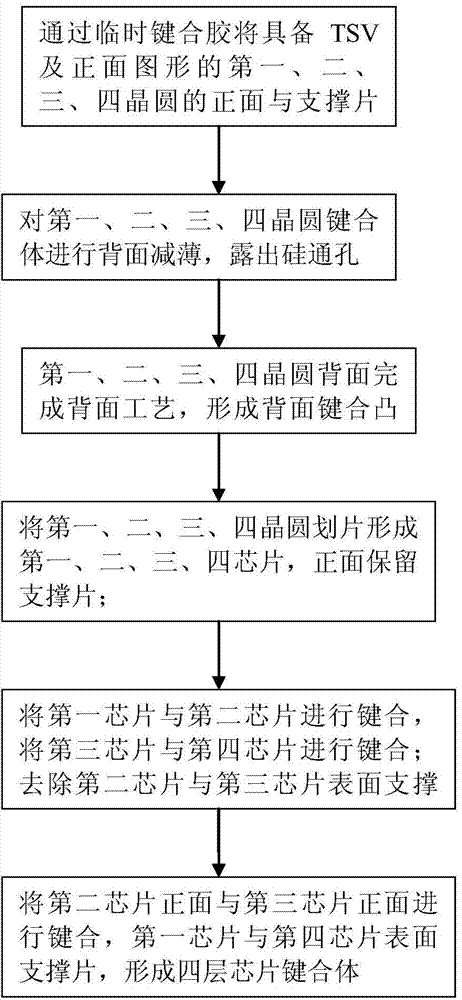

[0046] The present invention provides a kind of TSV multi-layer chip bonding method, and this preferred example uses four-layer chip and chip bonding method, such as figure 2 As shown, the method includes: making graphics and bumps on the front of the first, second or third, and fourth wafers, and temporarily bonding the front to the support sheet; Form graphics and bonding bumps; cut the first, second, third, and fourth wafers to obtain the first, second, third, and fourth chips, the first, second, or third, and fourth chips have support sheets on the front and bonding bumps on the back ; bond the back of the first chip to the back of the second chip or the back of the third chip to the back of the fourth chip; only remove the support sheet on the back of the second chip or the third chip; bond the two-layer bonding body to form four layers Die and die bonded body, remove support sheet.

[0047] Specifically, the following steps are included,

[0048] Step 1, with referenc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More