Patents

Literature

32results about How to "Avoid Fragmentation Risk" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for laser polishing of glass and polishing processing method of glass hole and glass sheet

ActiveCN112404736ASolve micro-cracks on the cut surfaceFix bugsGlass severing apparatusLaser beam welding apparatusGlass chipCw laser

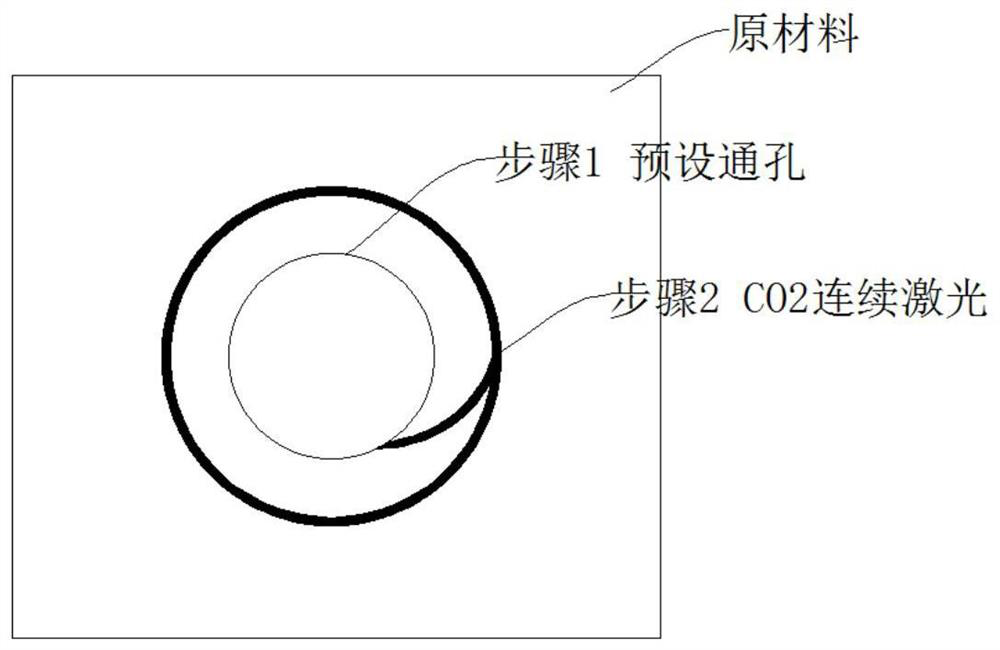

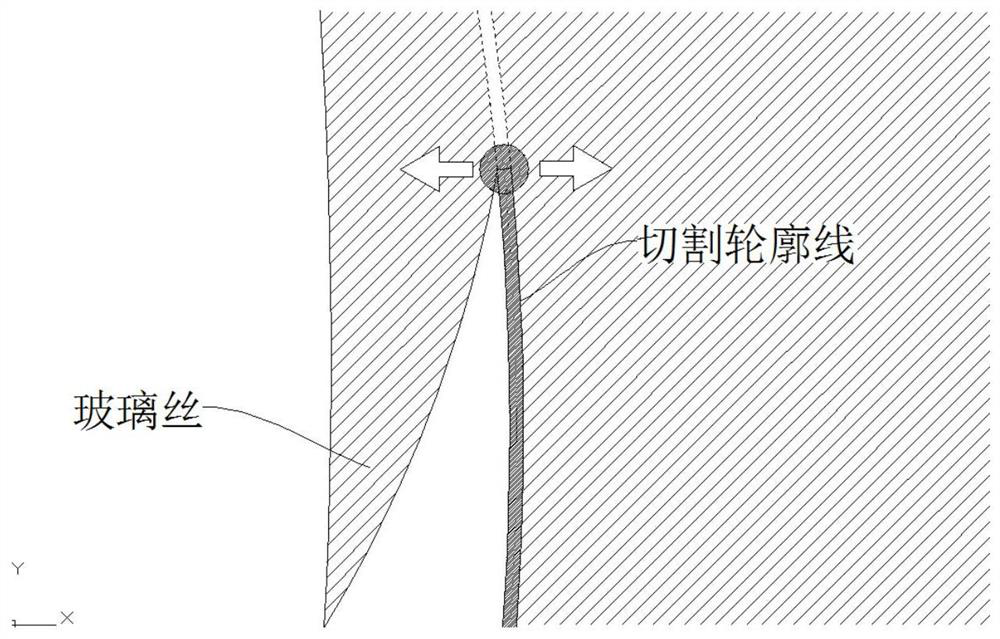

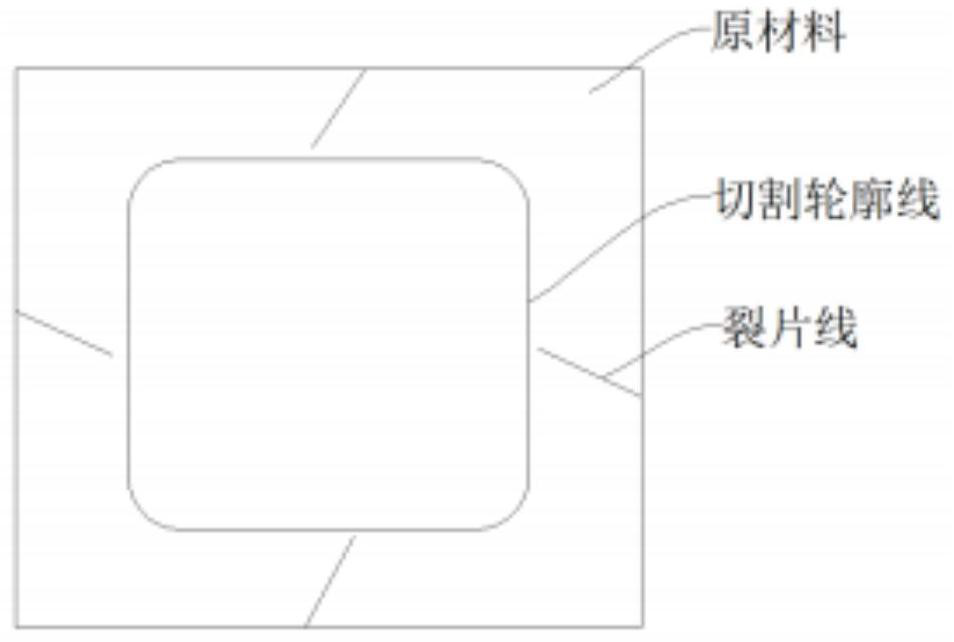

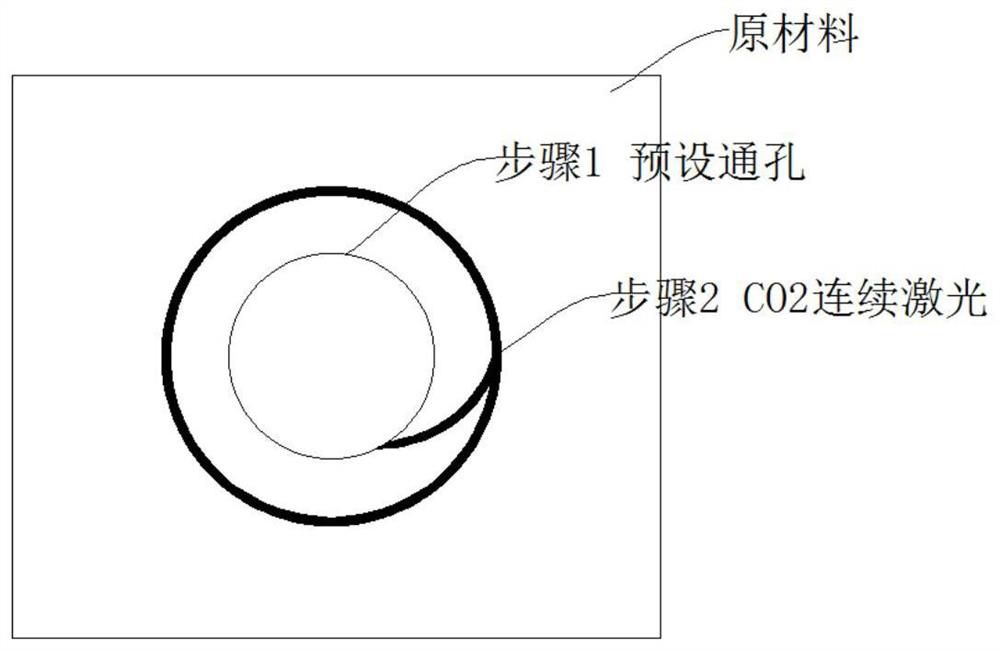

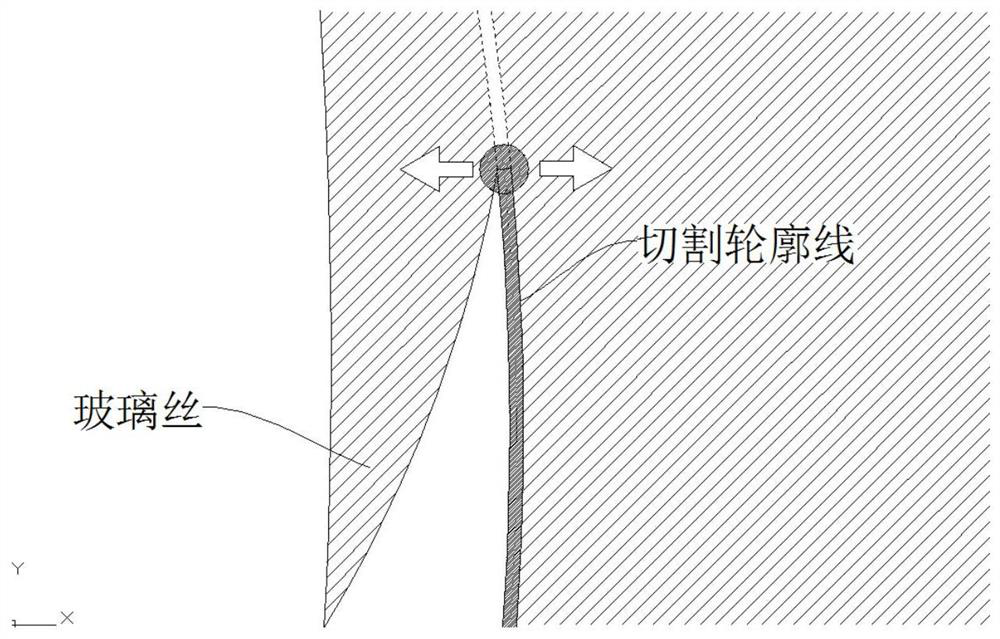

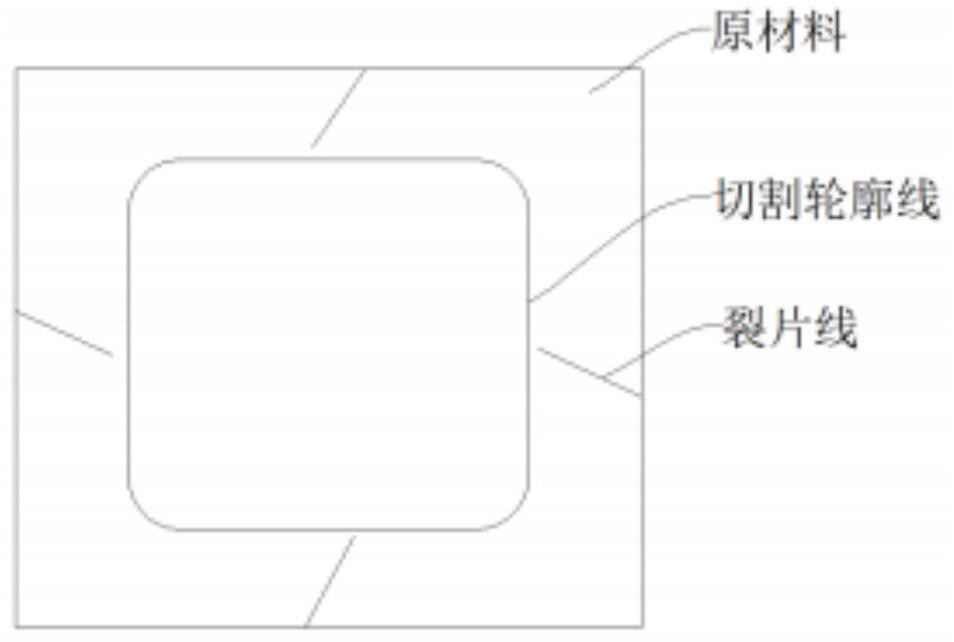

The invention provides a method for laser polishing of glass and a polishing processing method of a glass hole and a glass sheet. The method comprises the following steps of: irradiating a cutting contour line arranged on a glass plate by adopting first laser, and then cutting off the glass along the cutting contour line; and irradiating along a polishing contour line which is 0.3-1.2mm close to the cutting contour line by adopting second laser, and evaporating the glass on the two sides of the polishing contour line to obtain a polished glass product, wherein the second laser is CO2 continuous laser. According to the method, the defects of micro-cracks of a section caused by a conventional cutting mode can be overcome; the polishing contour line is directly irradiated by the CO2 continuous laser, so that glass bodies on the two sides of the polishing contour line are evaporated and removed, a smooth glass side section is obtained, and the mechanical property of the glass is improved;and the method can be applied to edge treatment of glass drilling, inner contour and outer contour, the plane quality of the side surface is optimized, and the potential fragment risk of the subsequent process is solved.

Owner:KORNERSTONE MATERIALS TECH

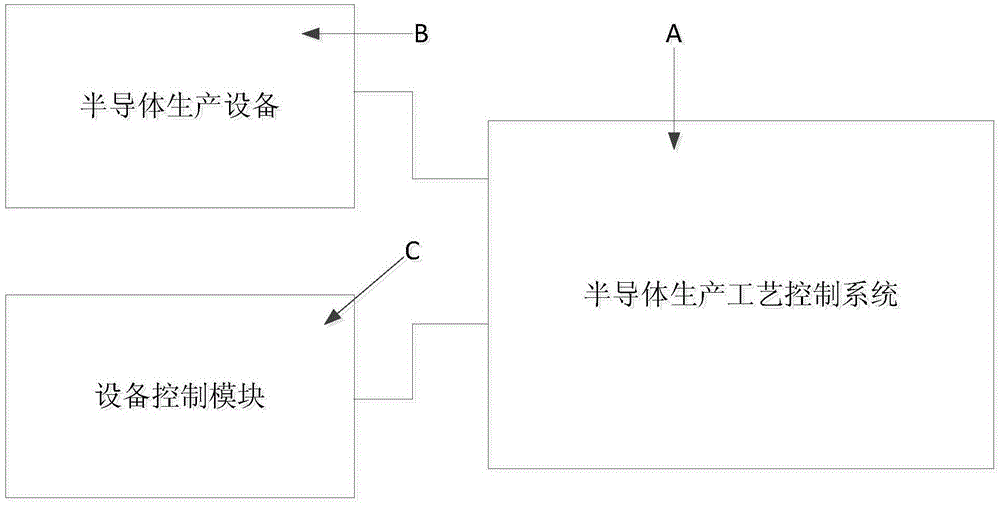

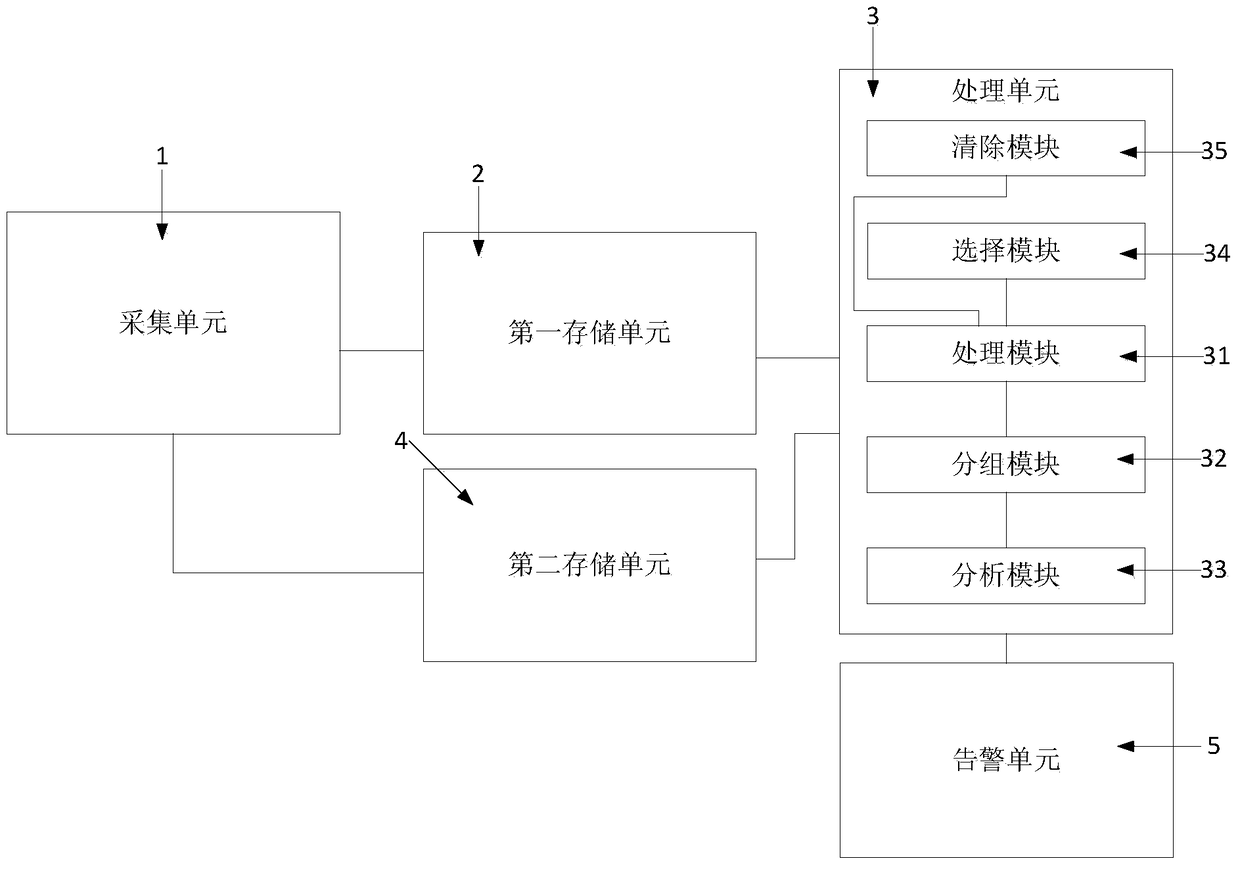

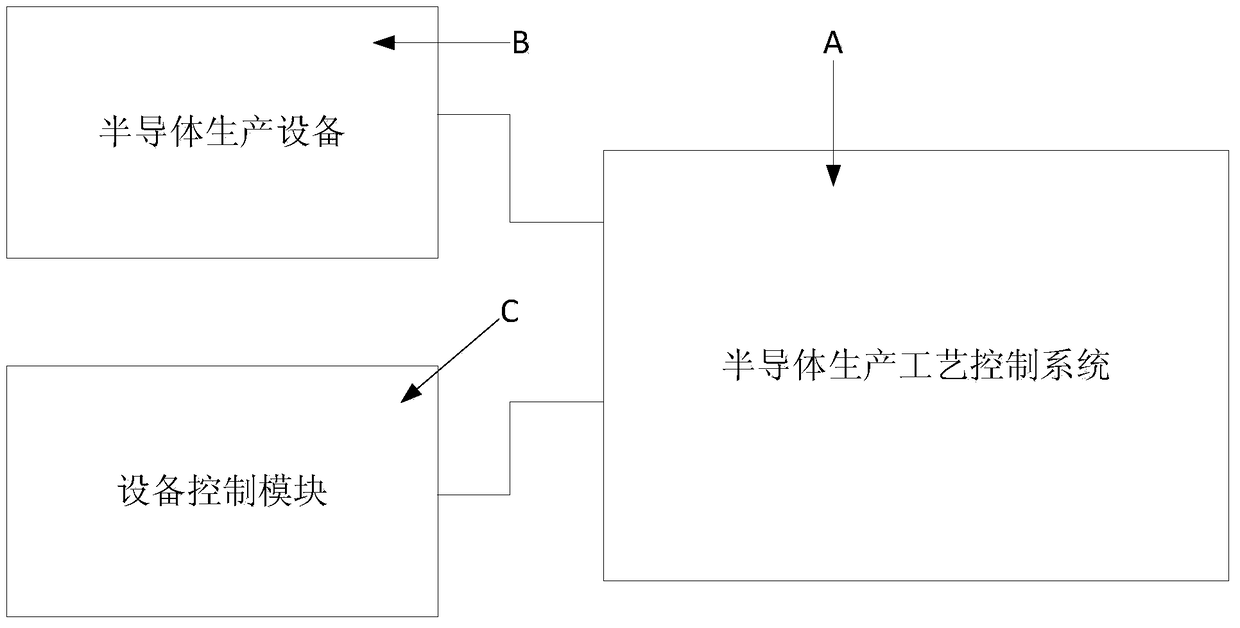

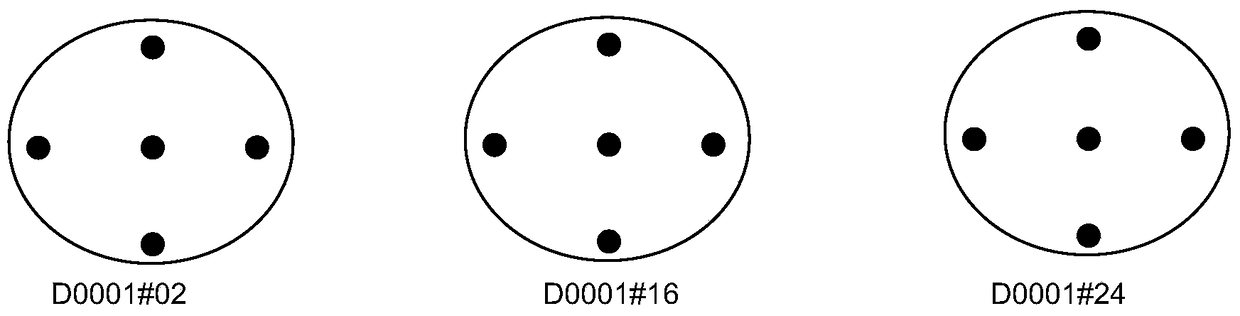

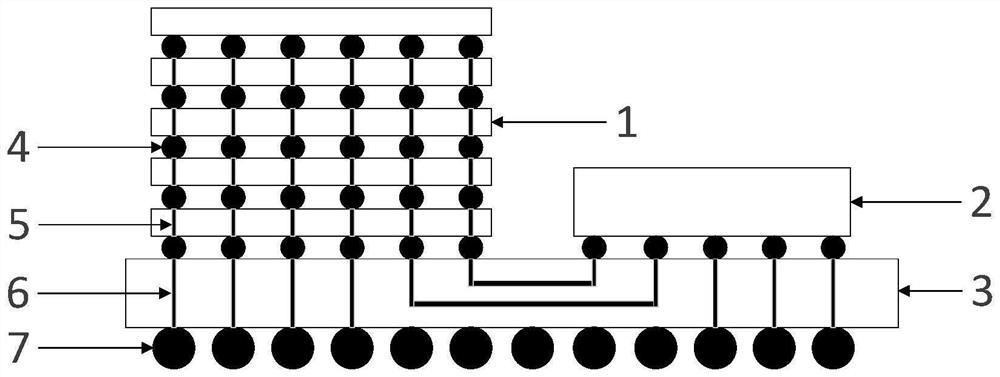

Semiconductor manufacturing process control system and analysis method

InactiveCN105470163AAvoid Fragmentation RiskGuaranteed yieldSemiconductor/solid-state device manufacturingControl systemOriginal data

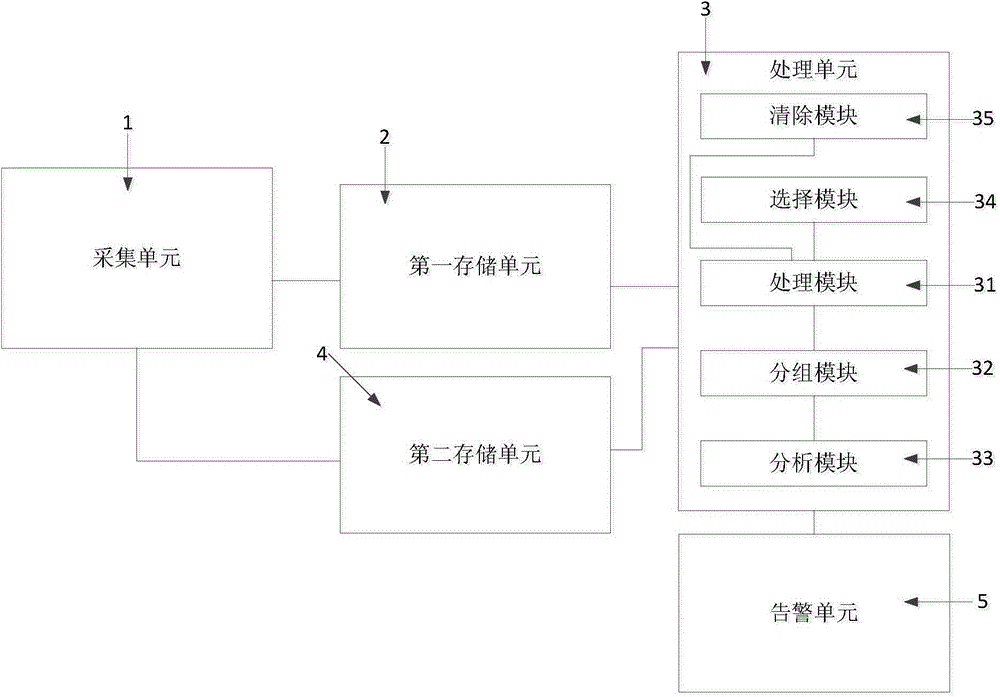

The invention discloses a manufacturing process control system and an analysis method, which belong to the technical field of semiconductor manufacturing process management and control. The semiconductor manufacturing process control system comprises an acquisition unit, a first storage unit, a processing unit and an alarm unit, wherein the acquisition unit acquires wafer original data; the first storage unit stores the wafer original data; the processing unit extracts the wafer original data and processes the wafer original data to obtain multiple groups of grouped data, and analyzes and outputs a variation trend of the grouped data; and the alarm unit receives an analysis result and outputs an alarm signal. The analysis method comprises the steps of: acquiring the wafer original data and storing the wafer original data in the first storage unit; extracting the wafer original data from the first storage unit, and processing the wafer original data to obtain the corresponding grouped data and dividing the grouped data into groups; and analyzing the variation trend of the grouped data, and outputting the analysis result to the alarm unit for alarm. The semiconductor manufacturing process control system and the analysis method have the beneficial effects of reducing alarm time delay and omission, avoiding fragment risk of products, and ensuring product yield.

Owner:SEMICON MFG INT (SHANGHAI) CORP

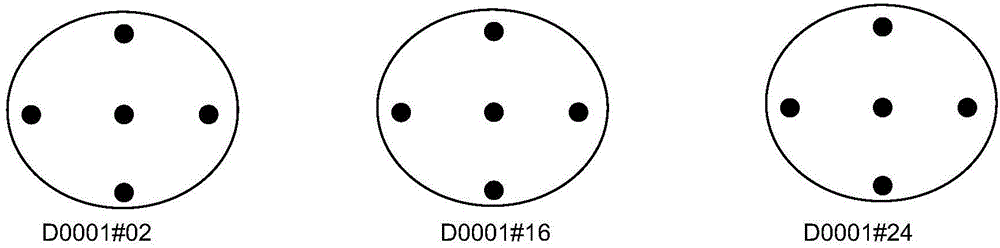

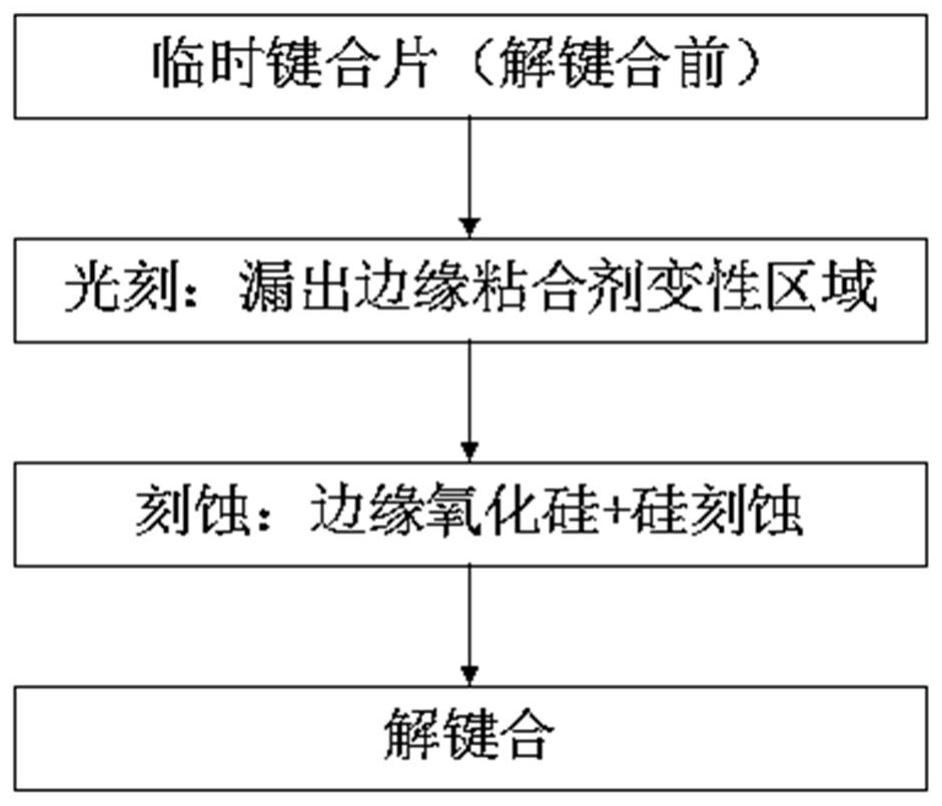

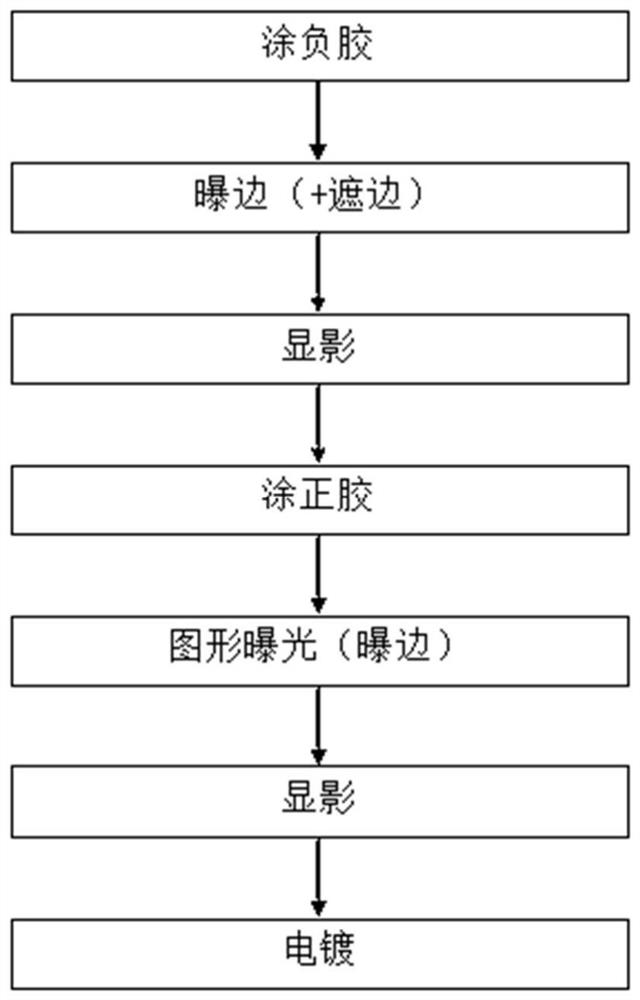

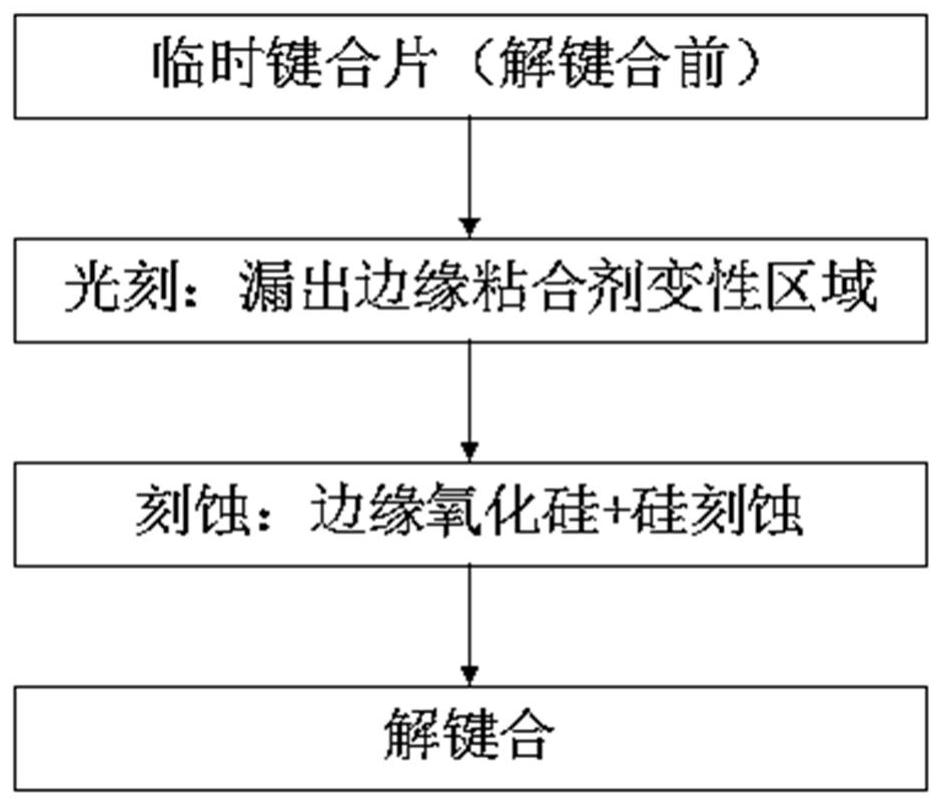

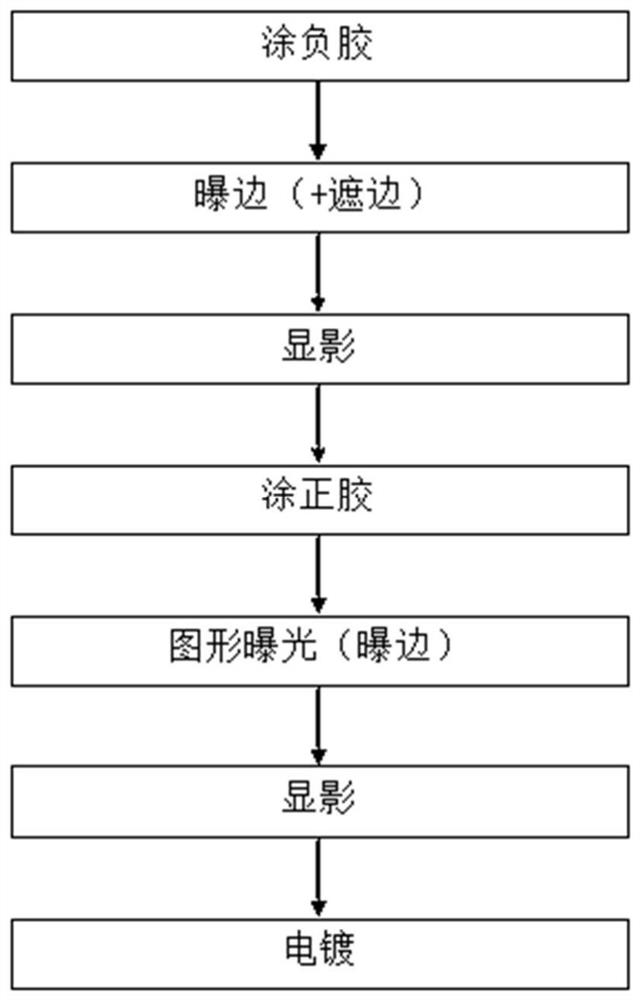

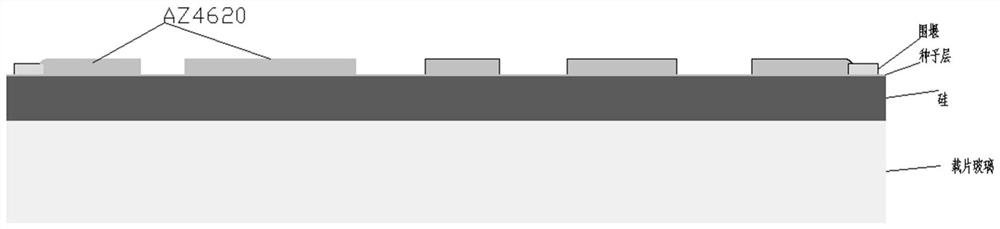

Wafer de-bonding method

ActiveCN111755377ASolve the problem that the debonding cannot be carried out smoothlyAvoid Fragmentation RiskSolid-state devicesSemiconductor/solid-state device manufacturingPretreatment methodBonding process

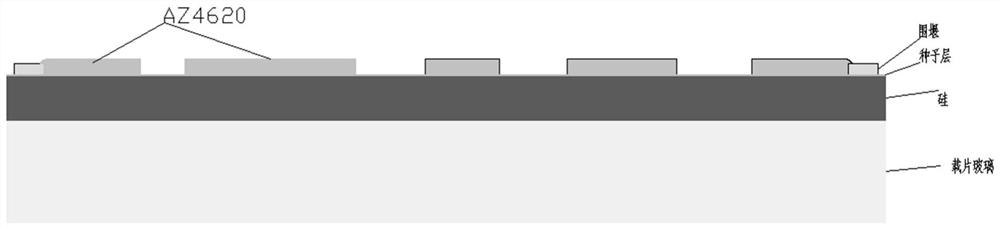

The invention discloses a thin wafer de-bonding method, which comprises the following steps of: 1, removing silicon etching on the outer ring of a silicon wafer undergone glue denaturation or glue overflow; and 2, de-bonding the silicon wafer and slide glass. A etching removal method in the first step comprises the steps of: preparing a mask layer on the wafer side, the mask layer is made of positive or negative photoresist, and the photoresist on the edge of the silicon wafer is removed through an exposure and development process; and directly etching the outer ring of the silicon wafer through a dry etching process. Aiming at the problems of thin wafer temporary bonding glue denaturation and glue extrusion, a de-bonding pretreatment method is adopted, silicon etching on the outer ring ofthe silicon wafer undergone glue denaturation or glue overflow is removed through mask preparation, etching and edge removal and other pretreatment processes, and then the de-bonding process is carried out, so that the problem that de-bonding cannot be smoothly carried out due to temporary bonding glue denaturation is solved, and the risk of fragmentation is avoided.

Owner:珠海天成先进半导体科技有限公司

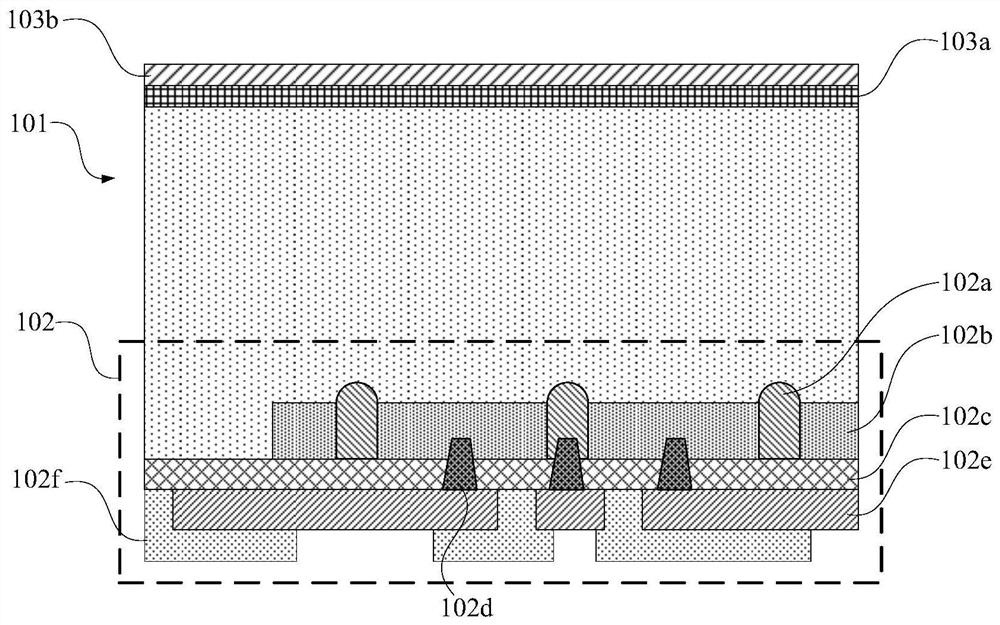

Touch display panel and manufacturing method thereof, and display device

InactiveCN107045409AIncrease contact areaElectrostatic discharge path stabilityInput/output processes for data processingEngineeringDisplay device

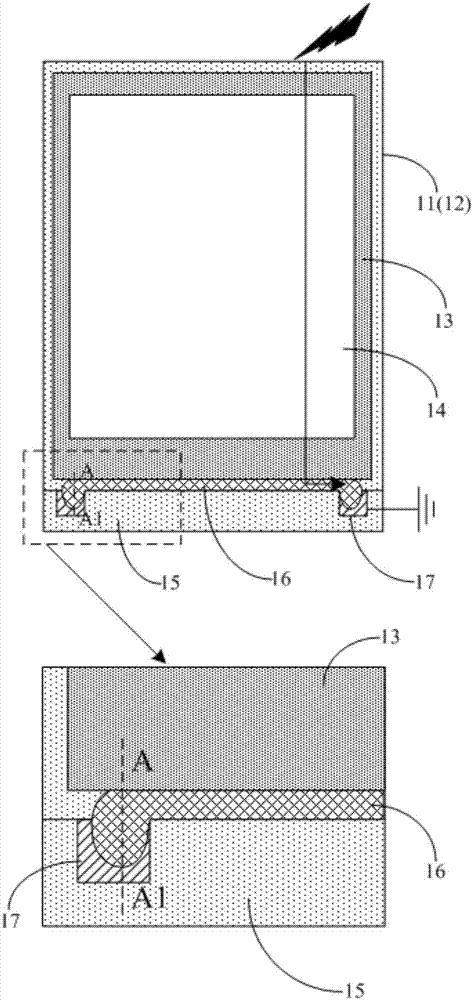

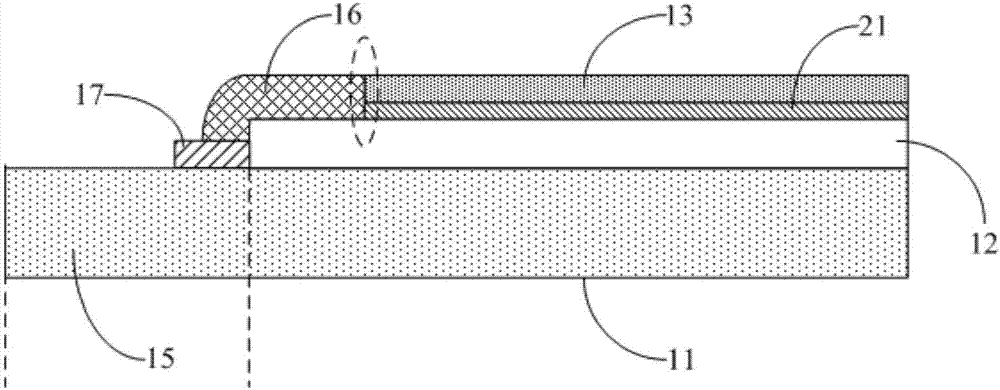

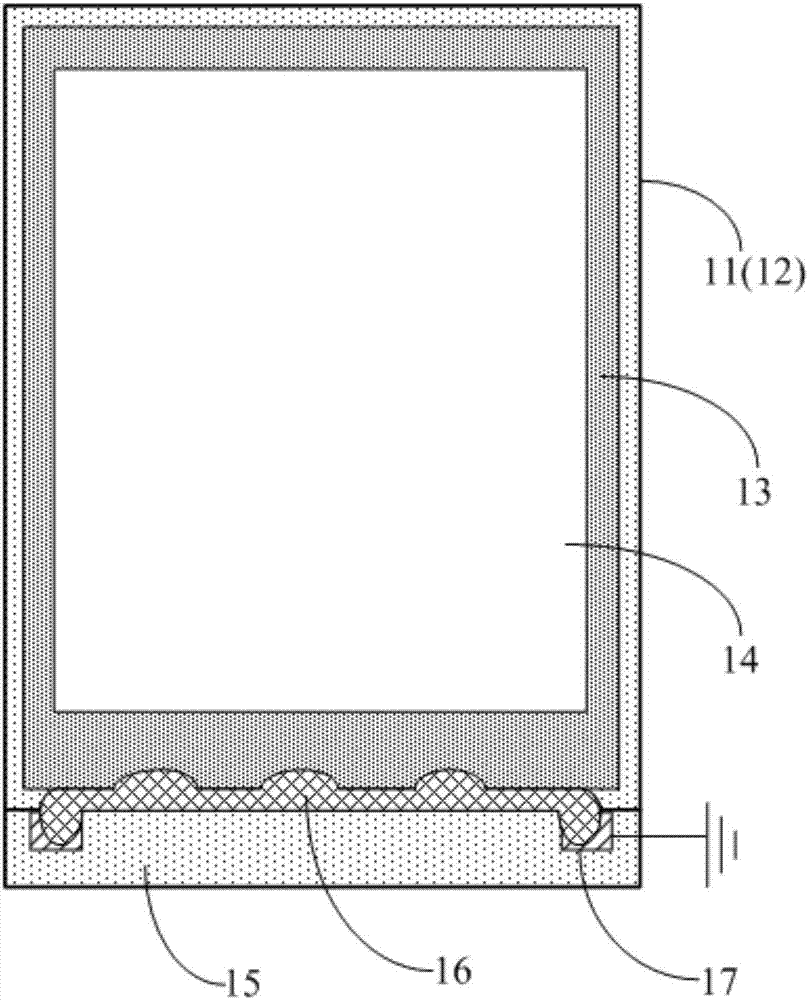

The invention discloses a touch display panel and a manufacturing method thereof, and a display device, aiming at improving the antistatic ability of the touch display panel and preventing the risk of fragments. The touch display panel comprises an array substrate and a subtended substrate which are arranged opposite to each other, a first polaroid arranged at the side, opposite to the subtended substrate, of the array substrate, a second polaroid positioned at the side, opposite to the array substrate, of the subtended substrate, a grounding electrode arranged on the array substrate, at least one conductive bar and a conductive connecting piece; the part of the conductive bar is exposed, and the exposed conductive bar is electrically connected with the grounding electrode by the conductive connecting piece; the conductive bar is positioned between the first polaroid and the array substrate, and the orthographic projection area of the conductive bar on the array substrate is positioned in a non-display area of the array substrate; and / or, the conductive bar is positioned between the second polaroid and the subtended substrate, and the orthographic projection area of the conductive bar on the subtended substrate is positioned in a non-display area of the subtended substrate.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

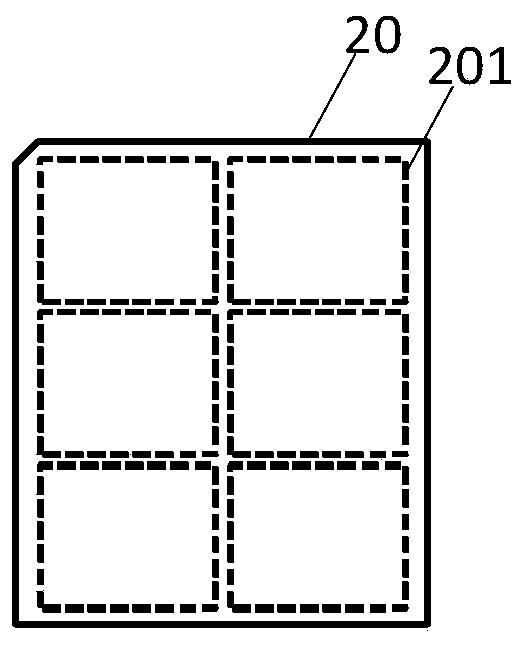

Slotted battery piece and battery piece module

PendingCN110197857ASmall spacingAvoid the risk of fragmentationPhotovoltaic energy generationSemiconductor devicesEngineeringElectrical and Electronics engineering

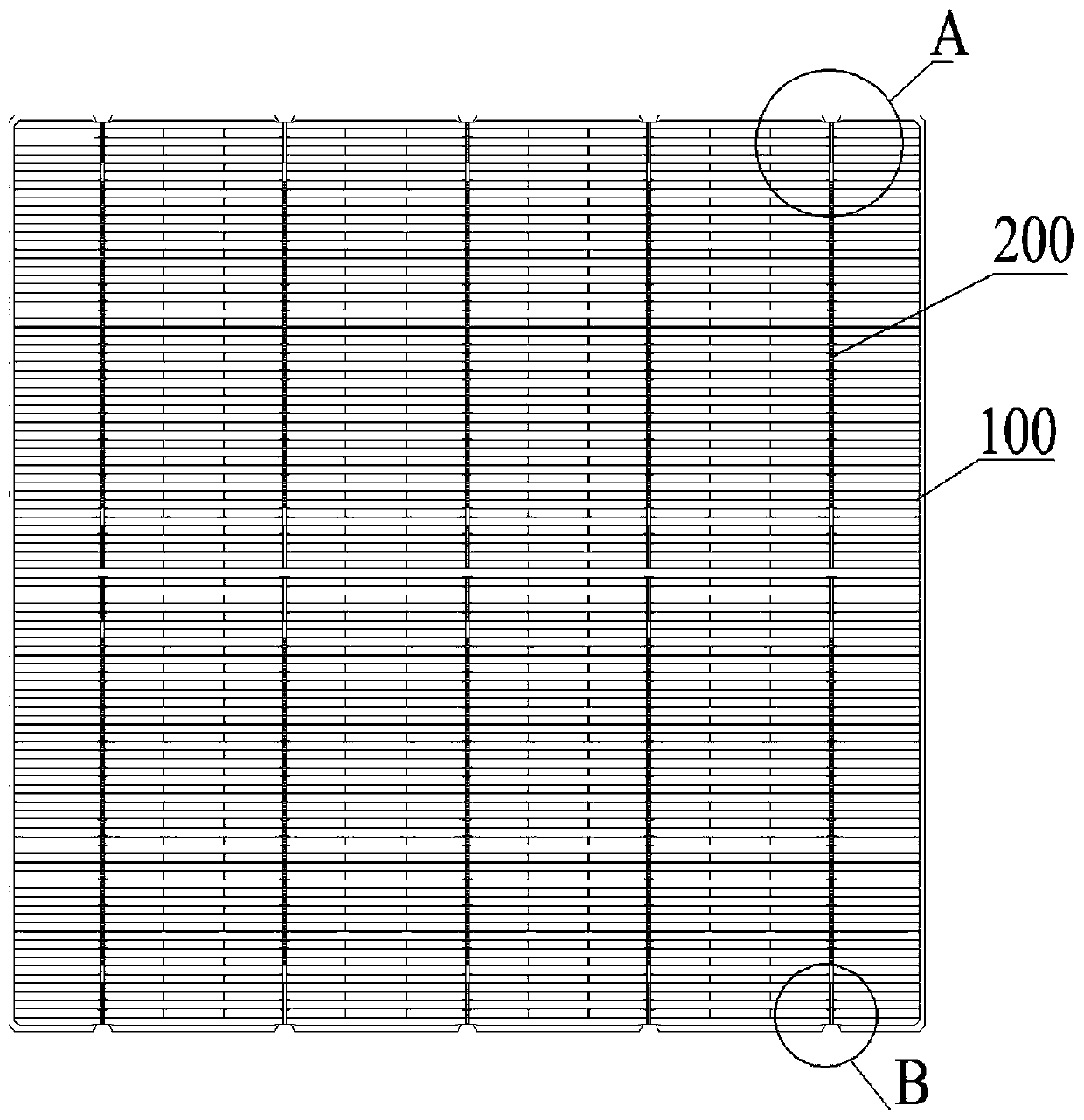

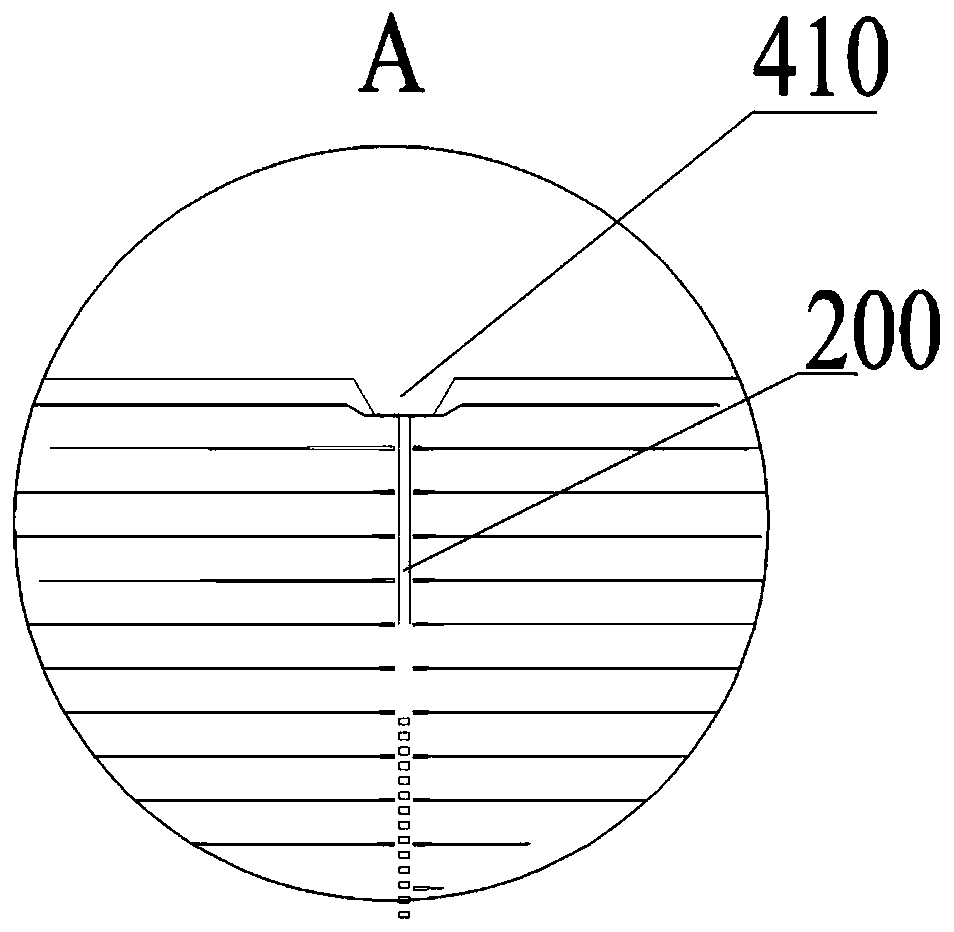

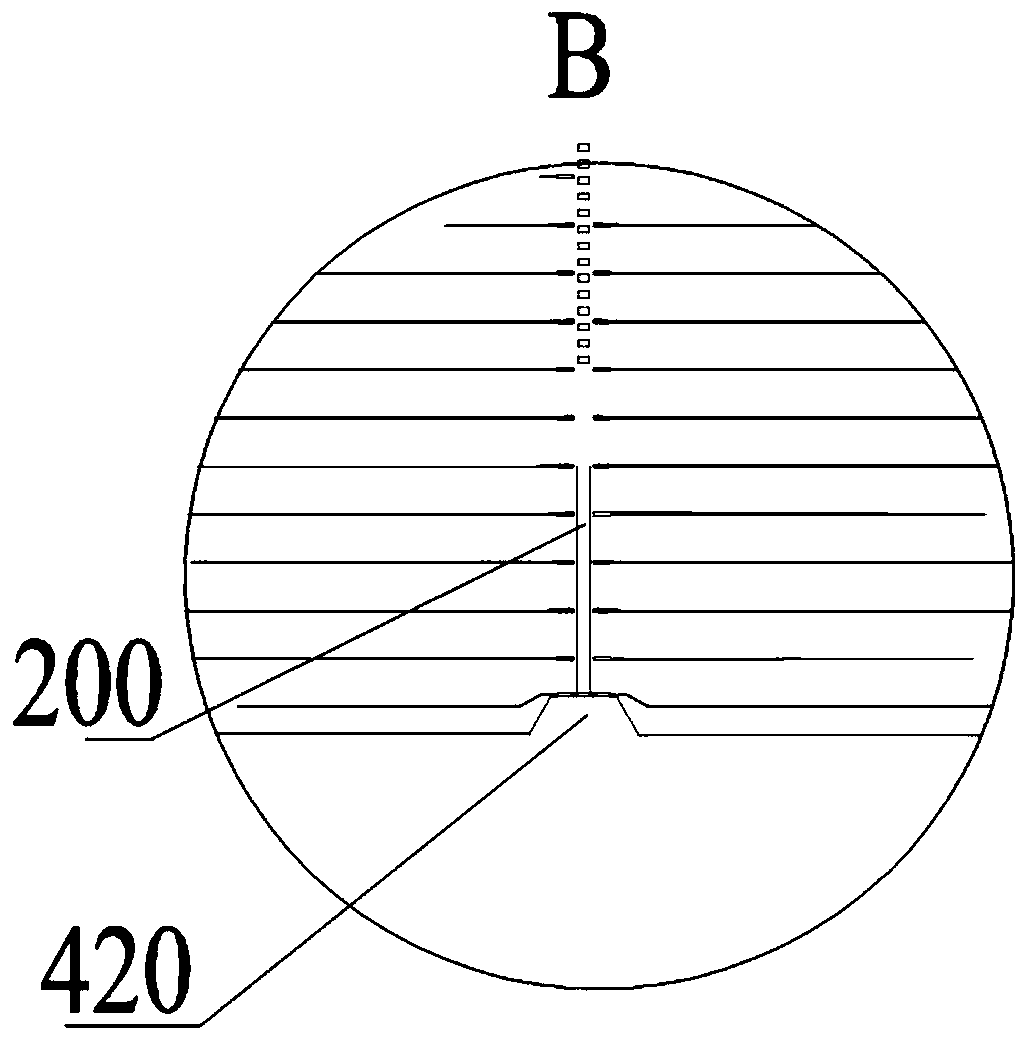

The invention relates to the field of photovoltaics, in particular to a slotted battery piece and a battery piece module. The slotted battery piece comprises a battery piece body, a main grid line isarranged on the front surface of the battery piece body, and a groove is formed at the position, close to the end of the main grid line, on the battery piece body. A first welding layer is laid on themain grid line, a second welding layer corresponding to the first welding layer in position is laid at the back surface of the battery piece body, and the front and rear ends of the first welding layer and the front and rear ends of the second welding layer respectively form a front welding end and a rear welding end. The battery piece module comprises a plurality of slotted battery pieces, and the second welding layer on the previous slotted battery piece is connected with the first welding layer on the current slotted battery piece through a bending welding strip; and the bending welding strip penetrates the groove. The slotted battery piece and the battery piece module can improve module efficiency, reduce the risk of battery piece breakage and reduce single piece cost.

Owner:WUXI SUNTECH POWER CO LTD

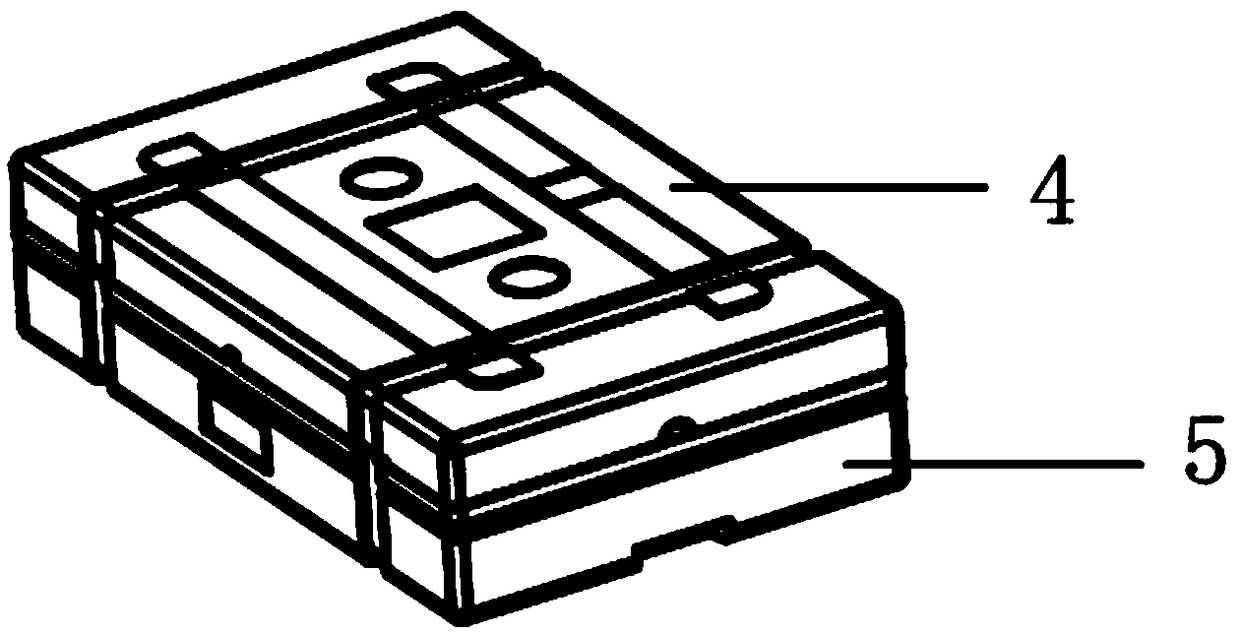

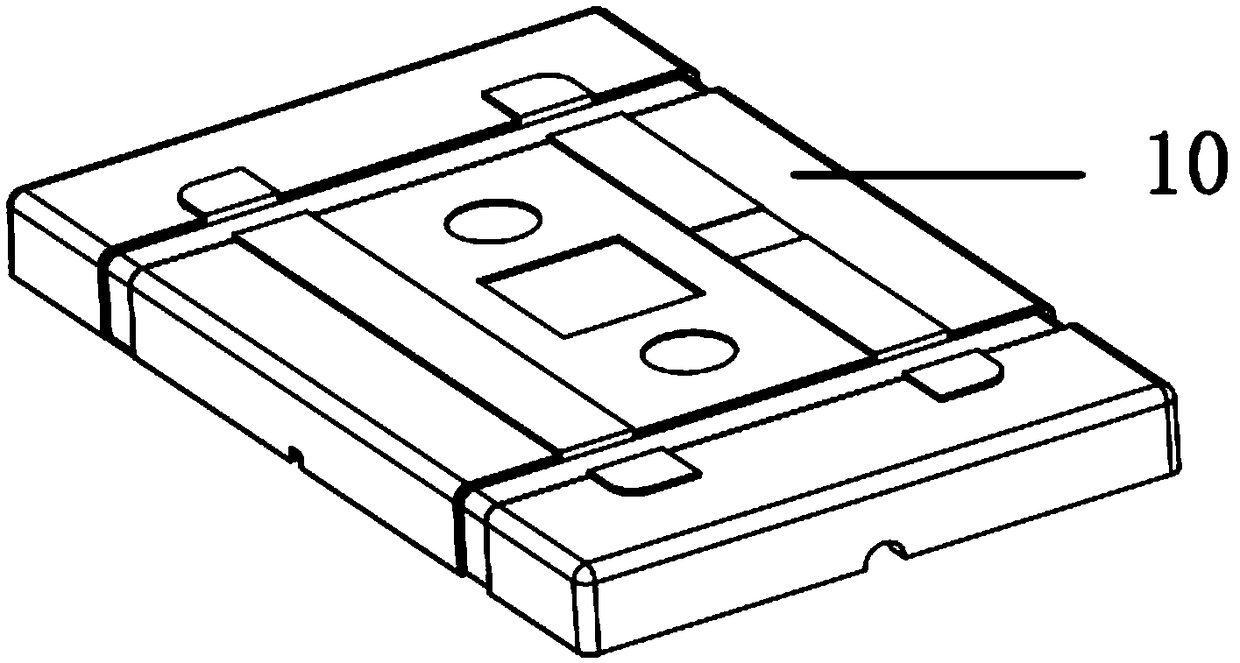

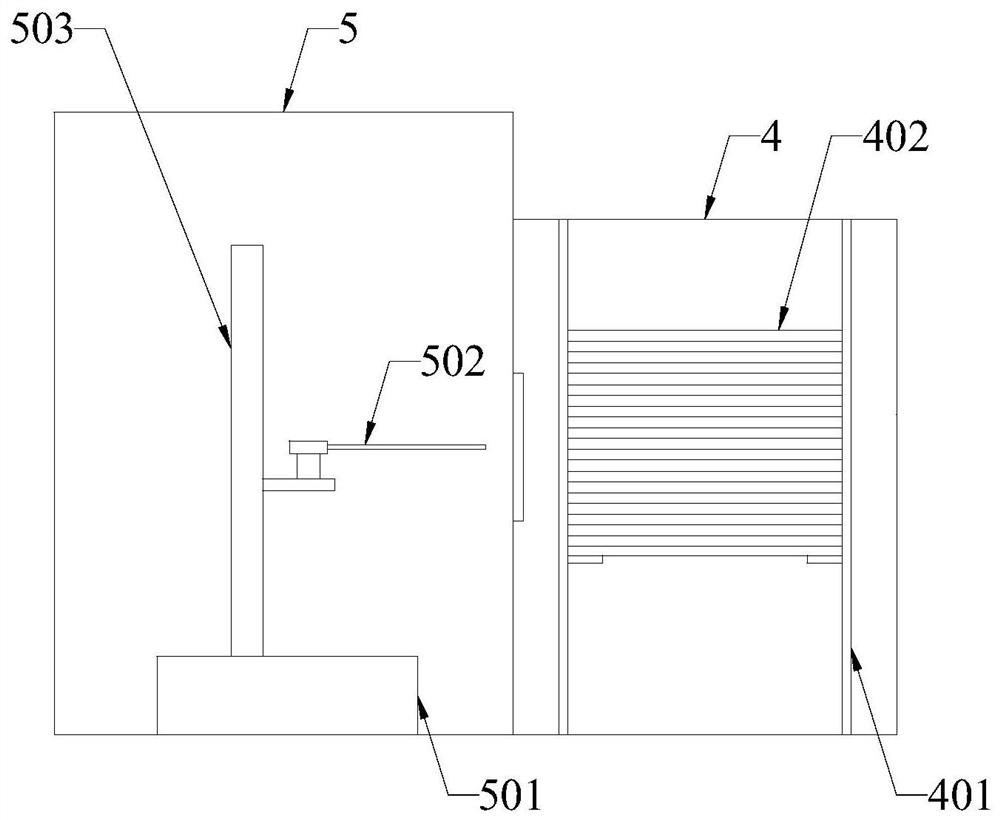

Crystal boat converter

InactiveCN102543794AAvoid Fragmentation RiskSemiconductor/solid-state device manufacturingConveyor partsEngineeringElectrical and Electronics engineering

The present utility model provides a crystal boat converter which comprises a pedestal, the pedestal is provided with a bearing plate, a first positioning area and a second positioning area are further formed along the first direction on the bearing plate, and a first blocking device is arranged on the bearing plate, specifically on the outer edge of one end of the second positioning area, which is far away from an spacing part. The height of the first blocking device is larger than the width of the spacing part, a blocking surface is formed by the first blocking device, and the blocking surface is faced with the spacing part. The second positioning area also comprises a second blocking device which is protruded on the bearing plate, thus operating personnel can be ensured by the first and second blocking devices to displace or fetch the crystal boat in a correct direction, thus the safety of wafers can be increased.

Owner:CHIPMOS TECH INC

Wafer processing method

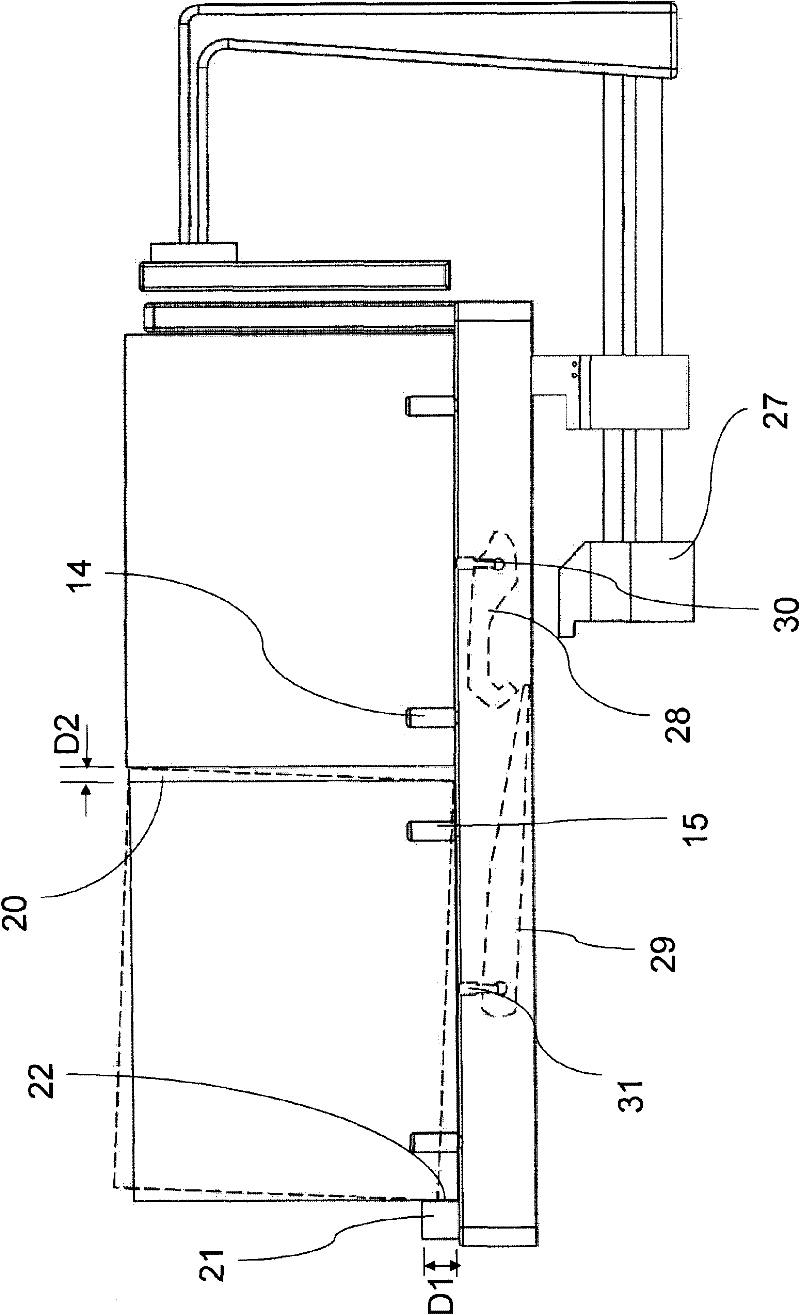

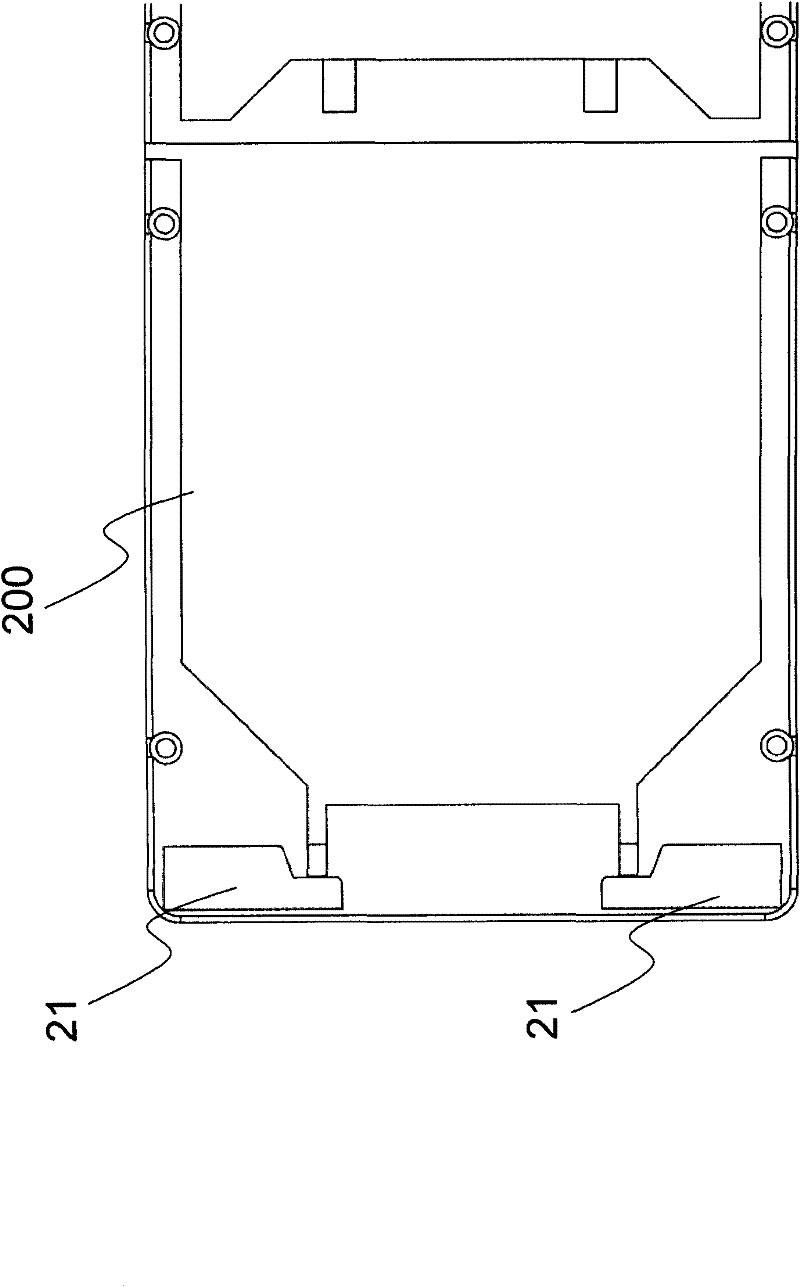

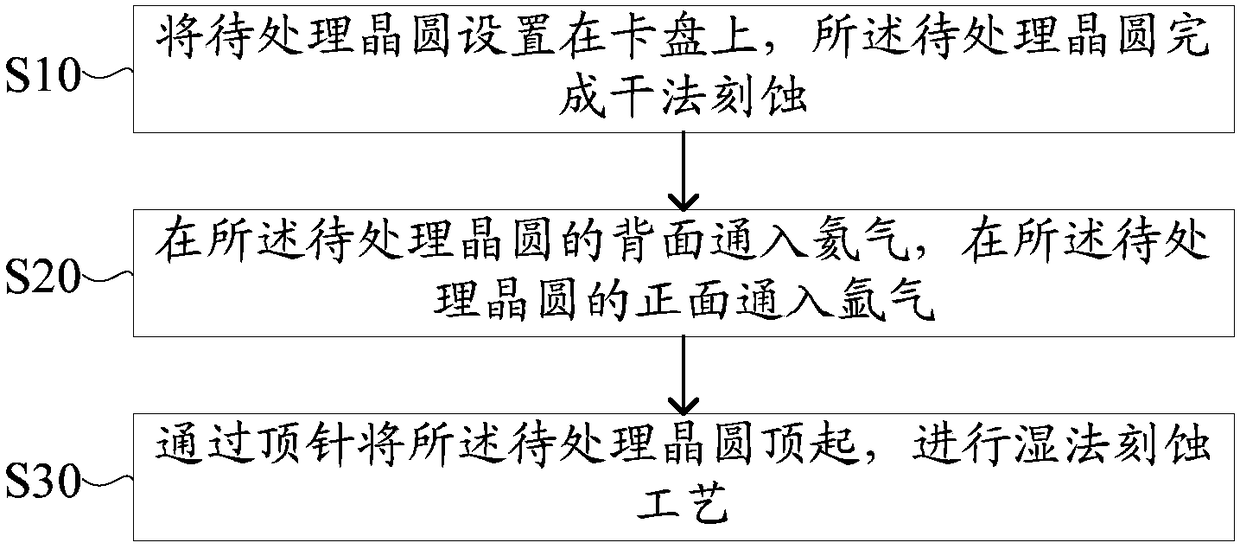

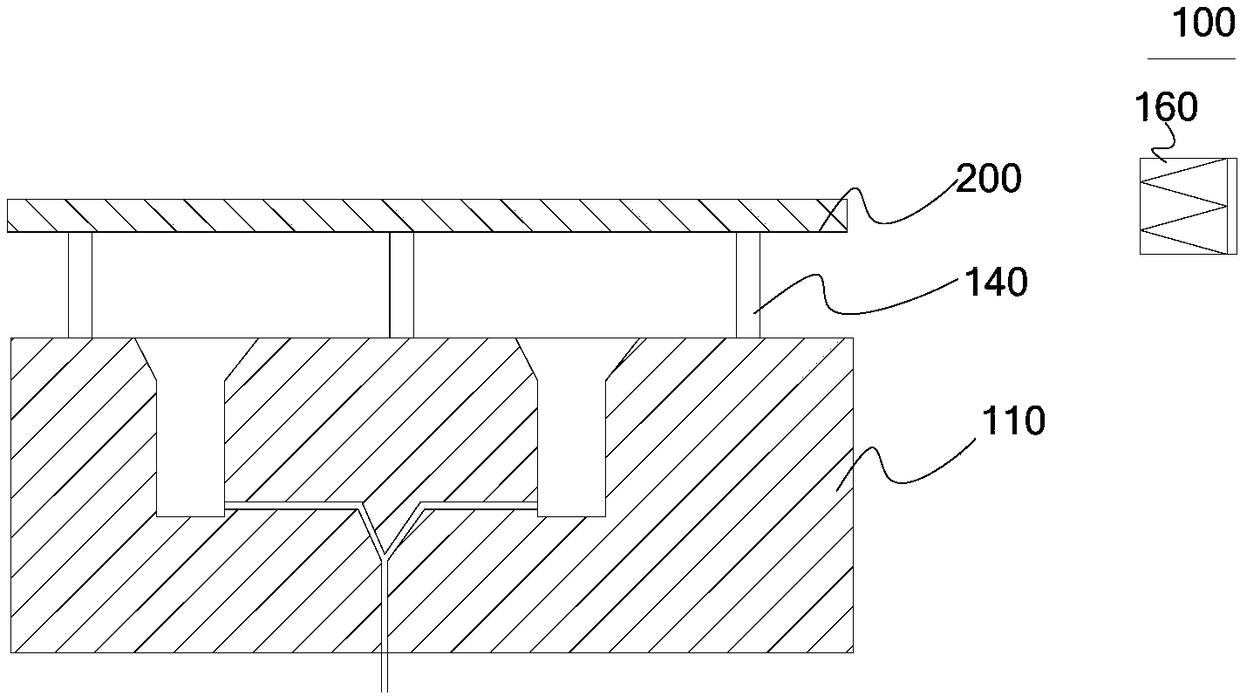

InactiveCN108493103AImproved Dynamic Alignment OffsetAvoid Fragmentation RiskSemiconductor/solid-state device manufacturingEngineeringHelium

The invention provides a wafer processing method. The wafer processing method comprises the steps of enabling a to-be-processed wafer to be placed on a chuck, and completing dry etching on the to-be-processed wafer; pumping helium to the back surface of the to-be-processed wafer, and pumping argon to the front surface of the to-be-processed wafer; enabling the to-be-processed wafer to be ejected by an ejector pin; and performing a wet etching process. According to the wafer processing method, after dry etching is completed on the to-be-processed wafer, helium is pumped to the back surface of the to-be-processed wafer; when the wafer is cooled, a carrier for transferring electrostatic charges removes electrostatic charges from the to-be-processed wafer; then the front surface of the to-be-processed wafer is pumped with argon to take away the electrostatic charges from the surface of the wafer; and next, the to-be-processed wafer is ejected by the ejector pin, so that dynamic alignment offset can be relieved, risk of wafer fragmenting caused by overhigh dynamic alignment offset can be prevented, and spherical defects formed in the wet etching can be avoided effectively, thereby improving product yield.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

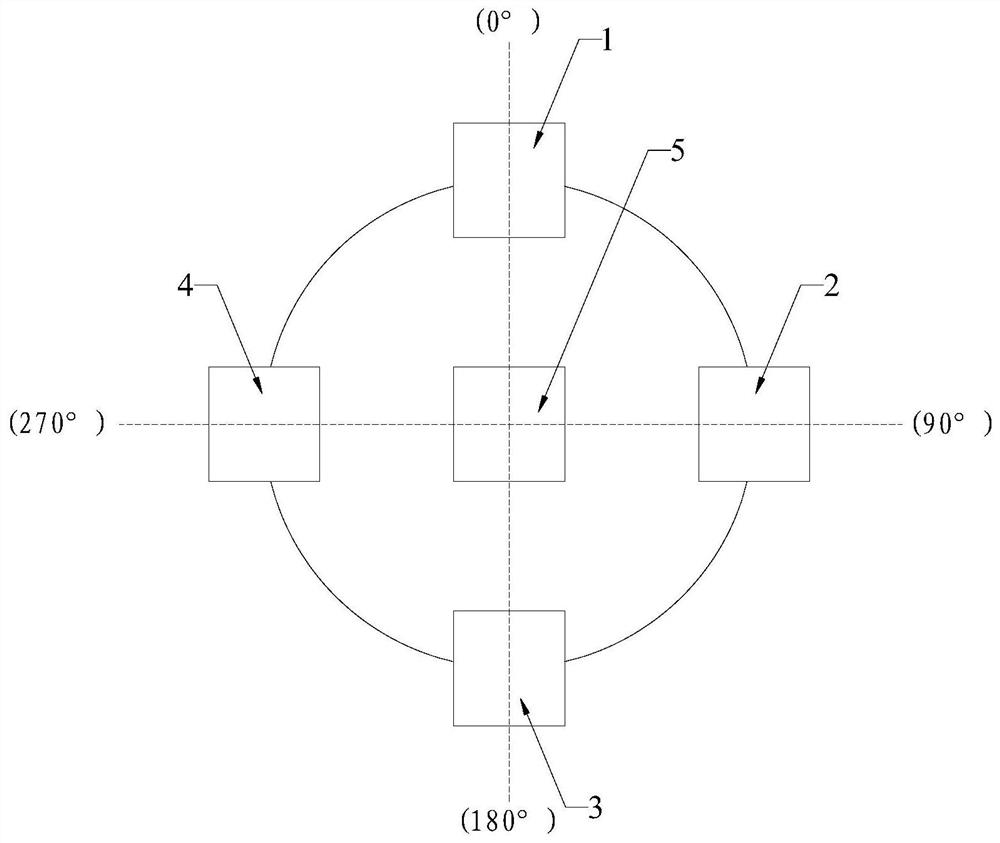

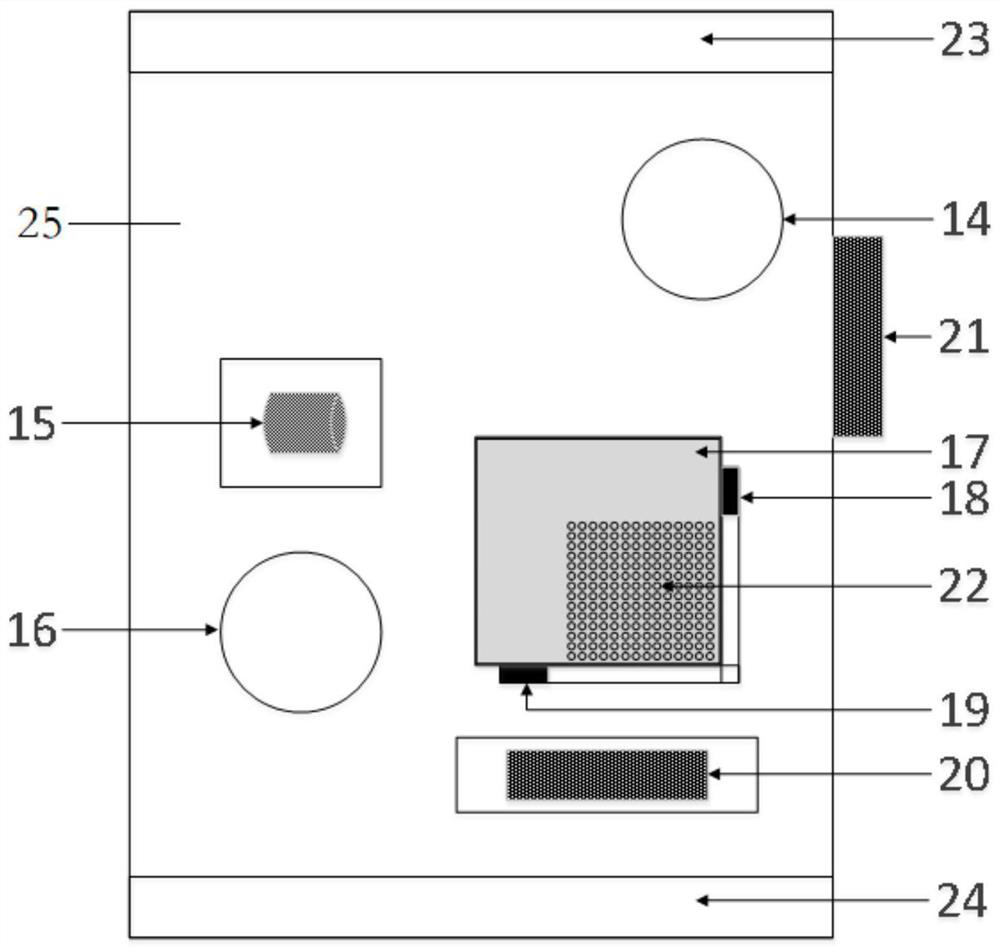

Substrate carrier platform and exposure machine

ActiveCN108279552AEffective protectionAvoid Fragmentation RiskPhotomechanical exposure apparatusMicrolithography exposure apparatusEngineeringStatic eliminators

The invention discloses a substrate carrier platform and an exposure machine. The substrate carrier platform comprises a body and at least one first electrostatic eliminator, wherein the body comprises a first surface and a second surface which are arranged opposite to each other; the first surface is used for carrying a substrate and is provided with at least one ion channel; each first electrostatic eliminator corresponds to at least one ion channel; the first electrostatic eliminators are respectively connected with the corresponding ion channels so as to provide electrostatic elimination ions for the ion channels. By means of the action of the ion channels and the first electrostatic eliminators corresponding to the ion channels, the static electricity generated by the surface, in contact with the substrate carrier platform, of the substrate can be eliminated, so that the electrostatic absorption force between the substrate and the substrate carrier platform can be eliminated, andthe substrate and the substrate carrier platform can be easily peeled off. Therefore, in a process of peeling off the substrate from the substrate carrier platform, the substrate can be effectively protected, the risk of breaking is effectively avoided when the substrate is peeled off, the production yield of the substrate is increased, and the manufacturing cost is reduced.

Owner:BOE TECH GRP CO LTD +1

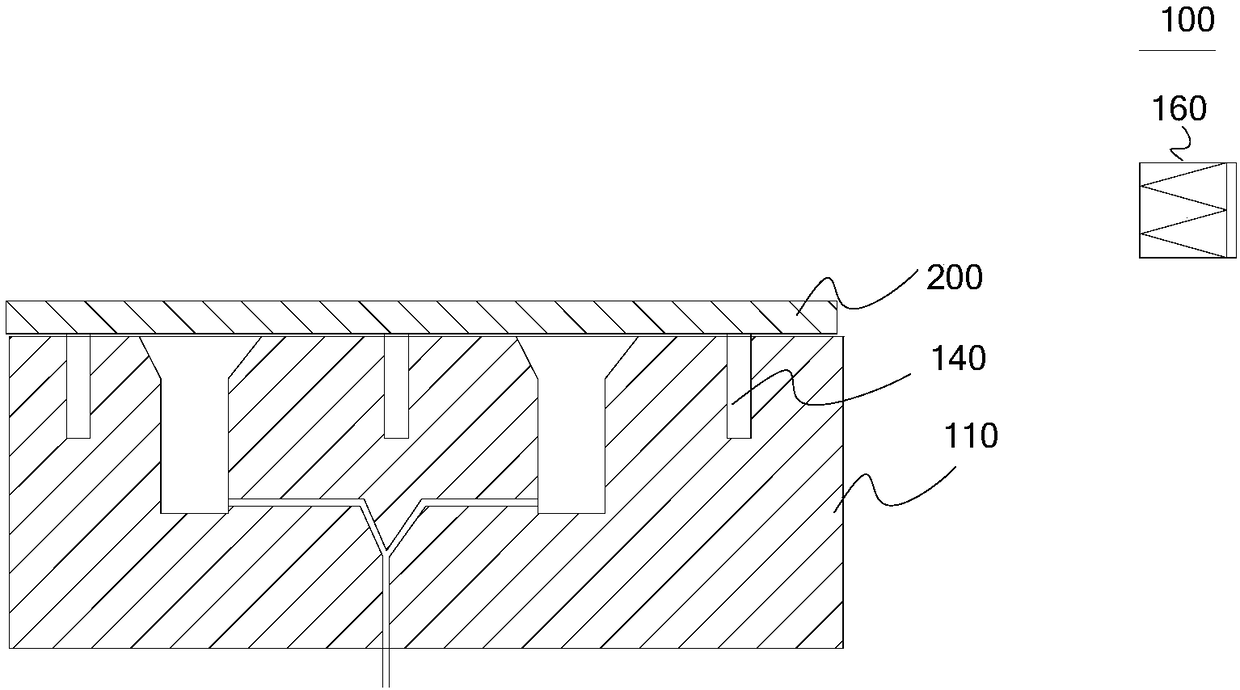

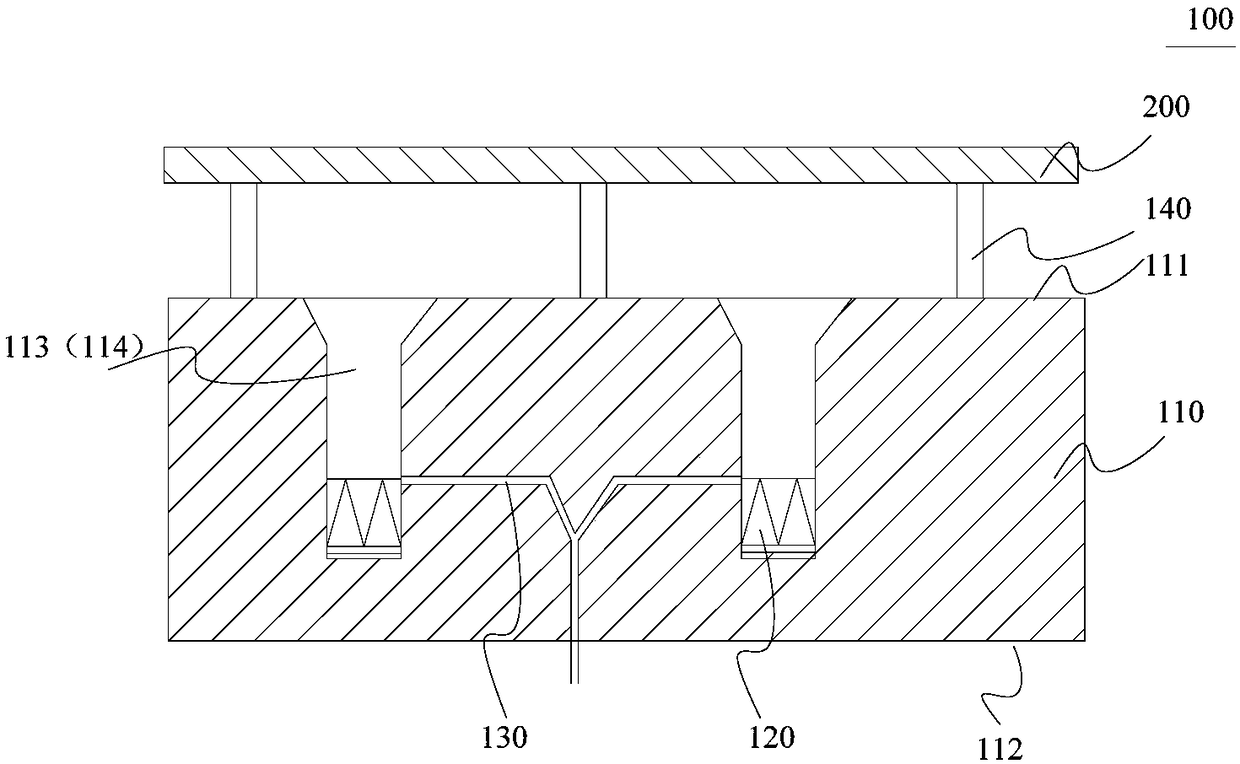

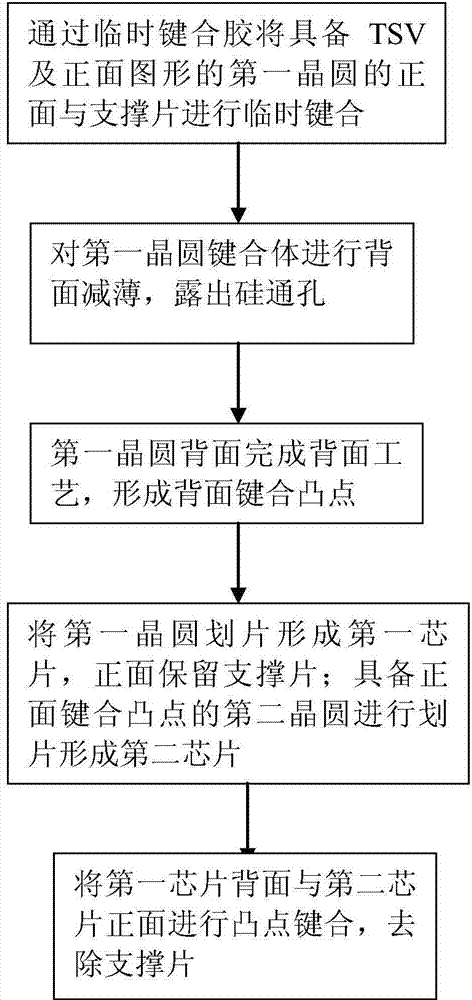

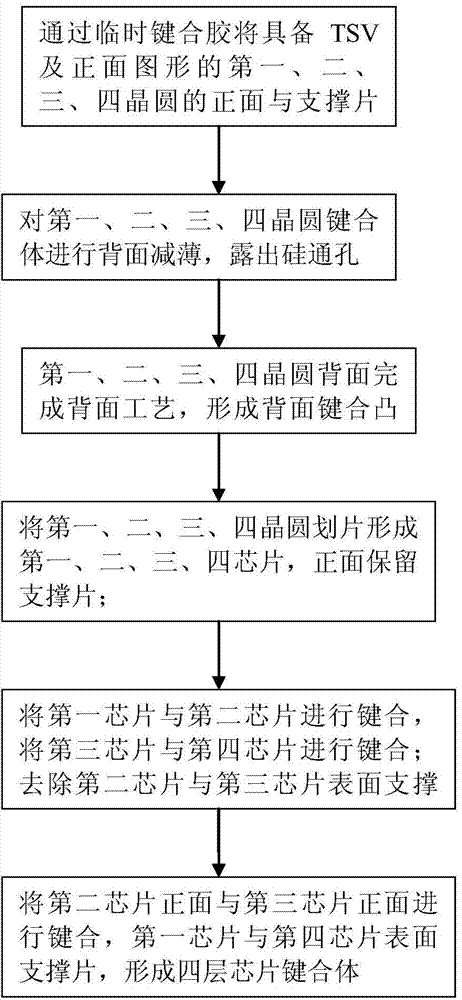

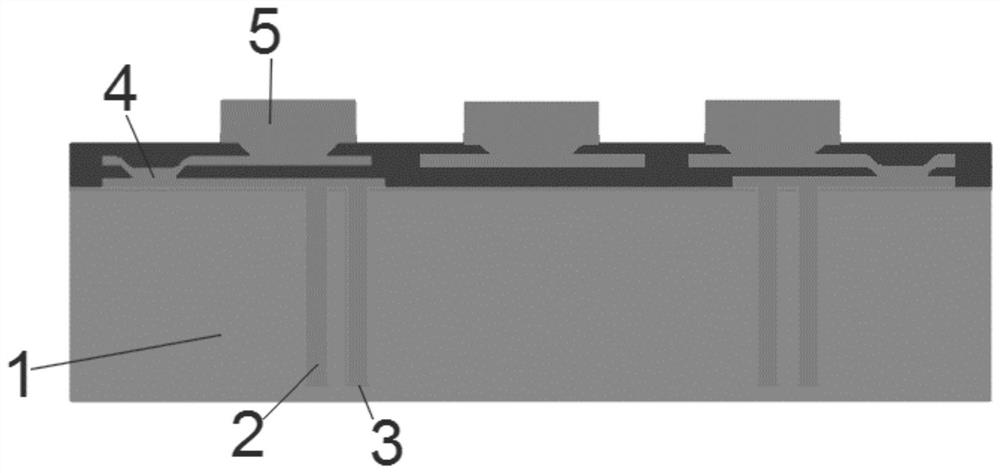

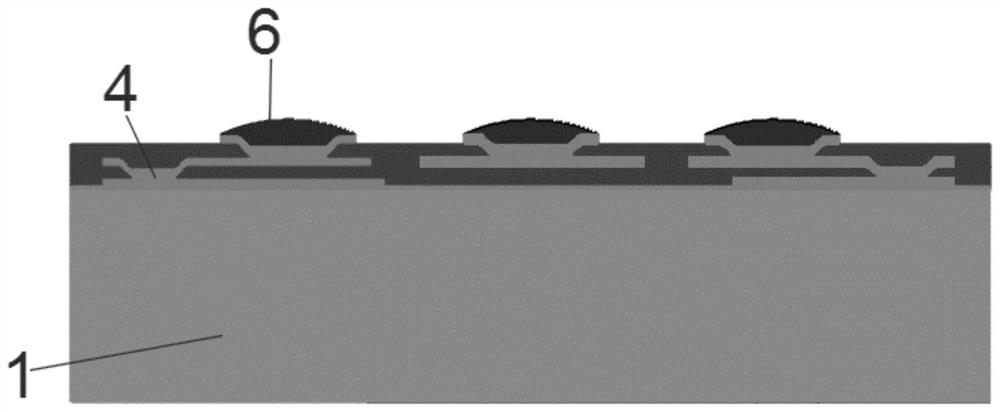

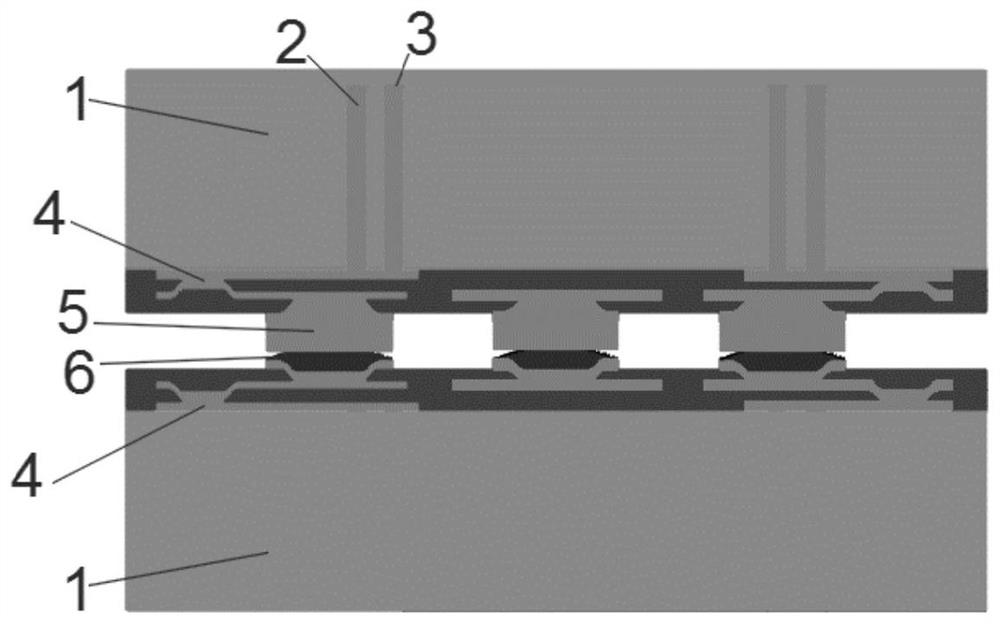

TSV multi-layer chip bonding method

InactiveCN104716060AAvoid damageAvoid destructionSemiconductor/solid-state device manufacturingWafer bondingDie bonding

The invention provides a TSV multi-layer chip bonding method including the steps that firstly, the front face of a first wafer with TSV and a front pattern is temporarily bonded to a supporting piece to form a first wafer bonding body; secondly, the back side of the first wafer bonding body is thinned, and a silicon through hole is exposed to form a back side bonding protrusion; thirdly, the bonding body is sliced, the supporting piece is reserved on the front side to form a first chip; fourthly, a second wafer provided with a front side bonding protrusion is sliced to form a second chip; fifth, protrusion bonding is carried out on the first chip and the second chip, and the supporting piece is removed to from a second-layer bonding body; sixthly, protrusion bonding is carried out on chips formed by repeating the first step to the third step according to the step five, sequential bonding and stacking of multiple layers of chips are achieved, and a TSV multi-layer chip is obtained. Or, protrusion bonding is carried out on the chips formed by repeating the first step to the third step in pairs, and a two-layer bonding body with supporting pieces on two sides is formed, and the TSV multi-layer chip is obtained by bonding the chips and / or the two-layer bonding body with the supporting piece on one side removed.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

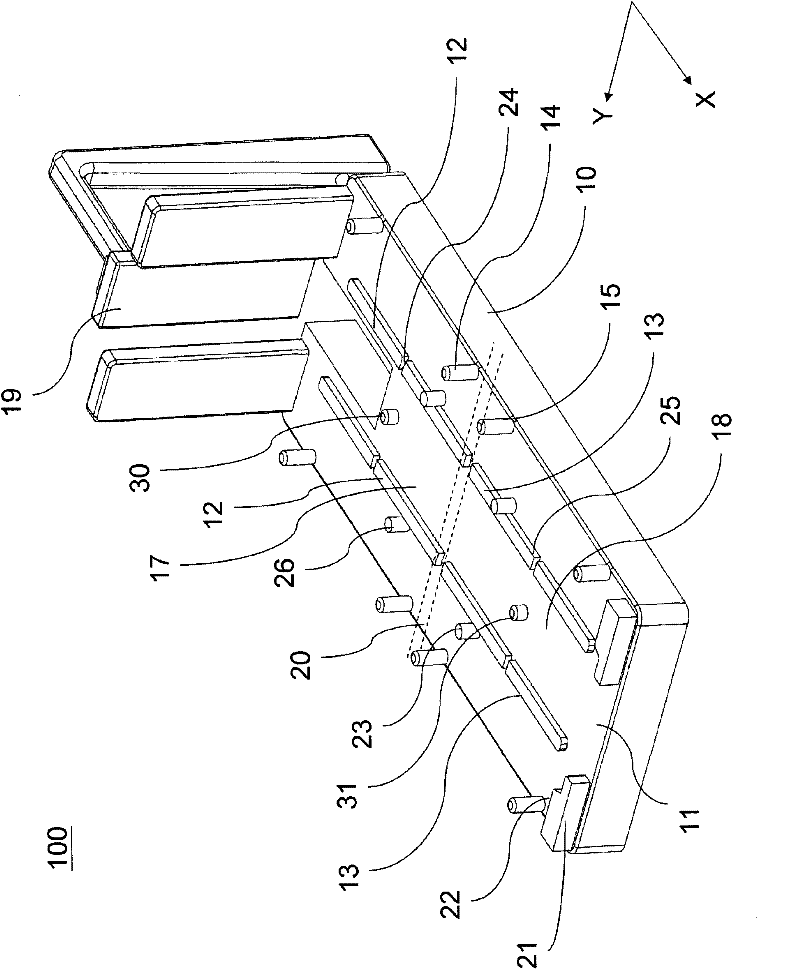

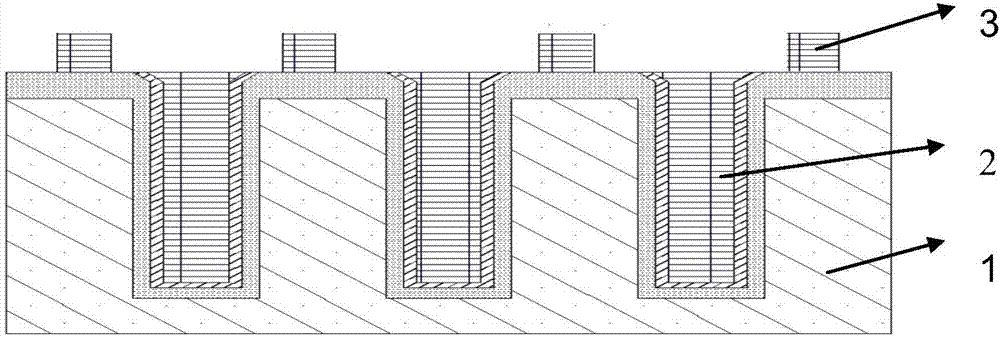

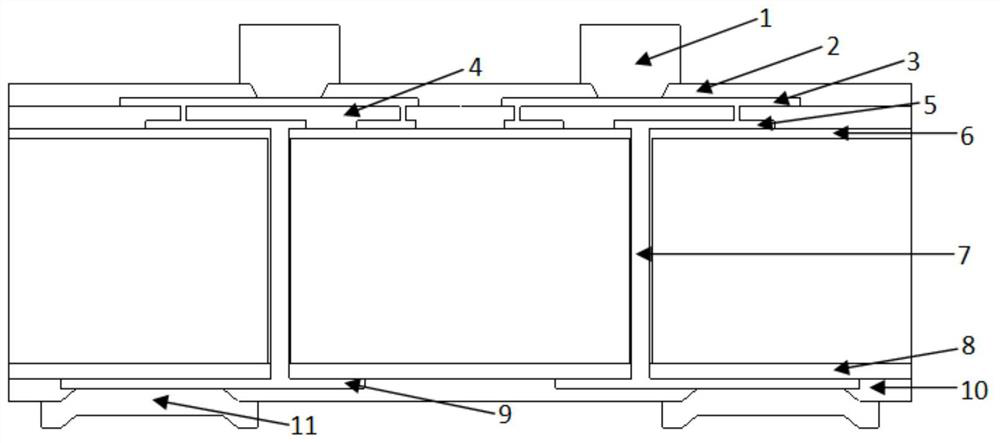

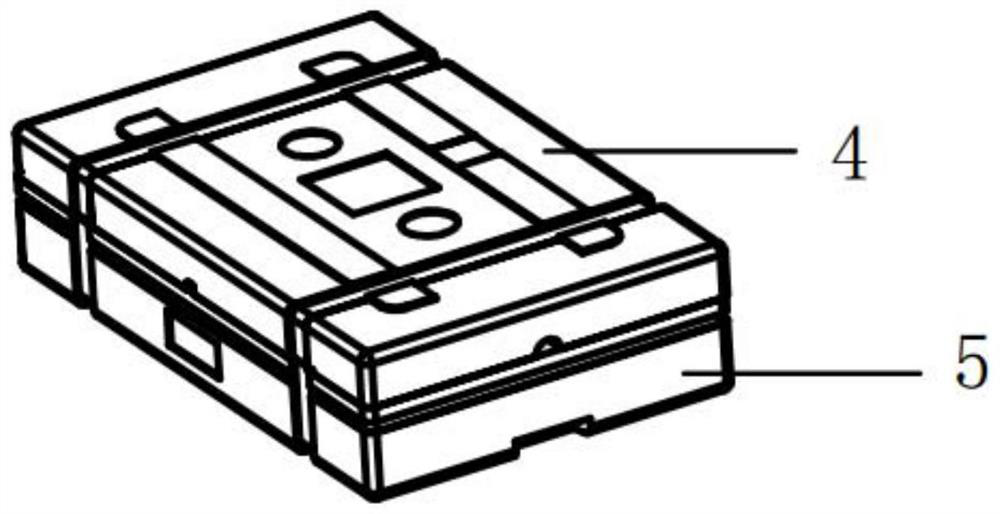

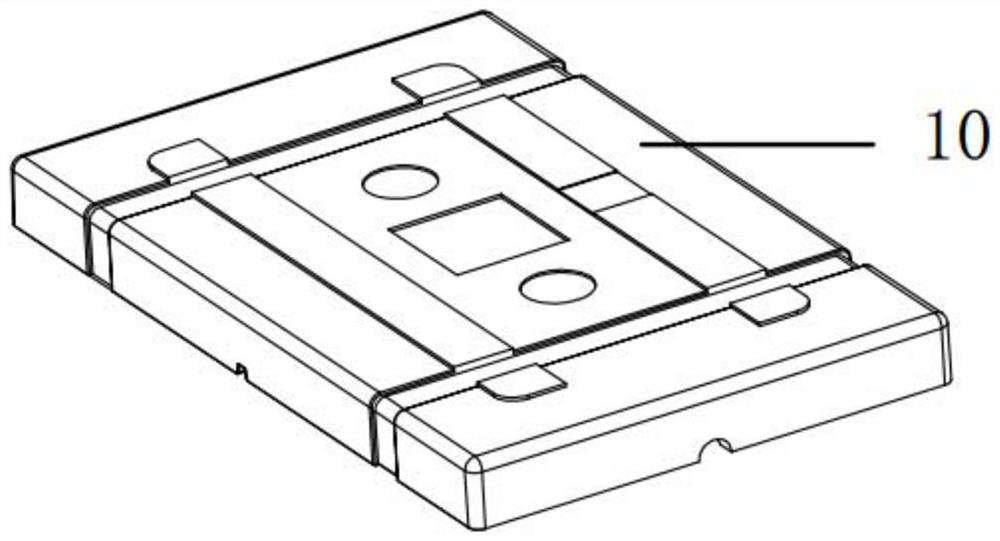

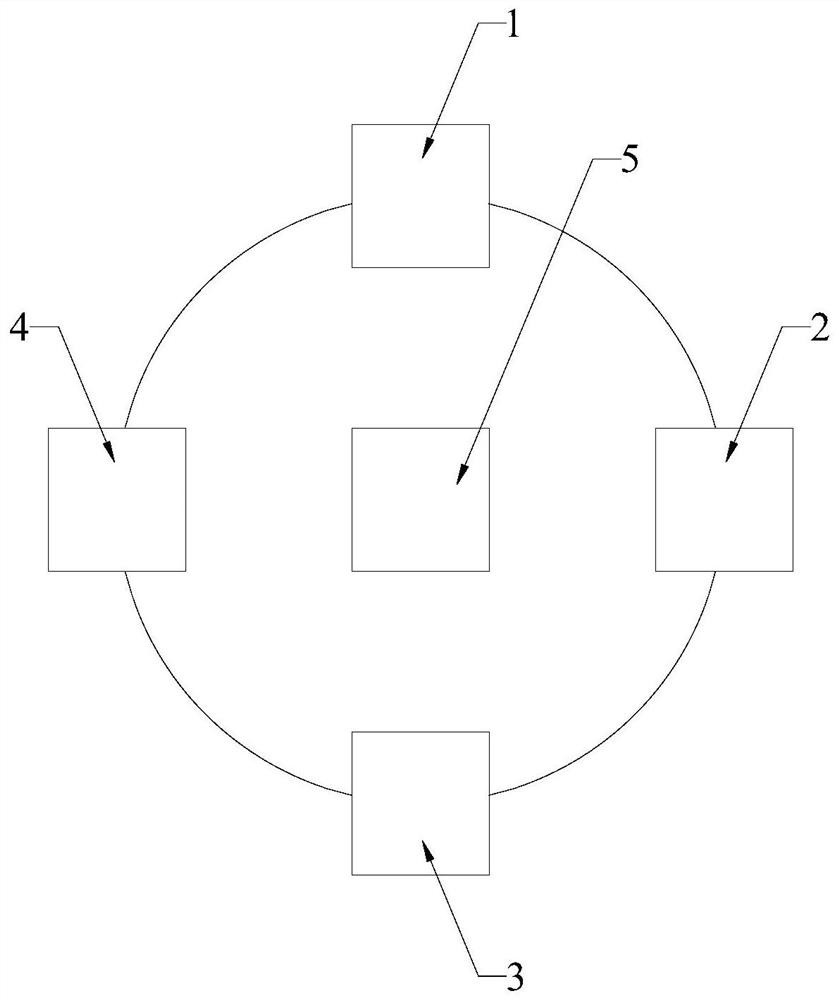

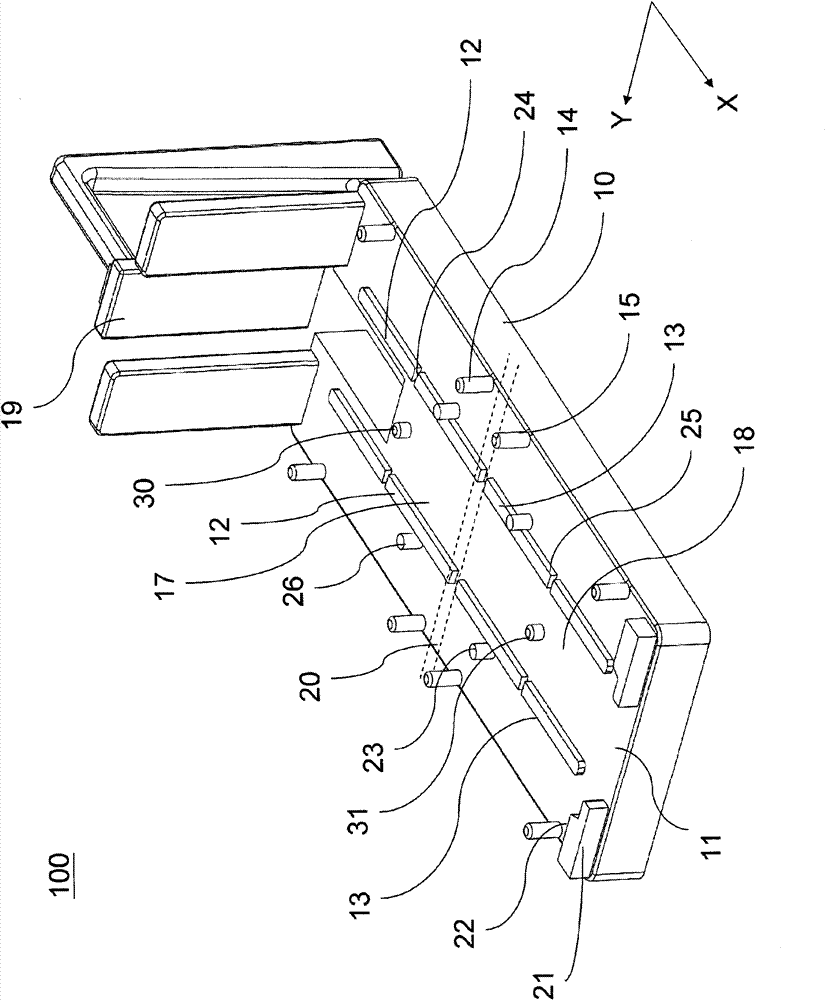

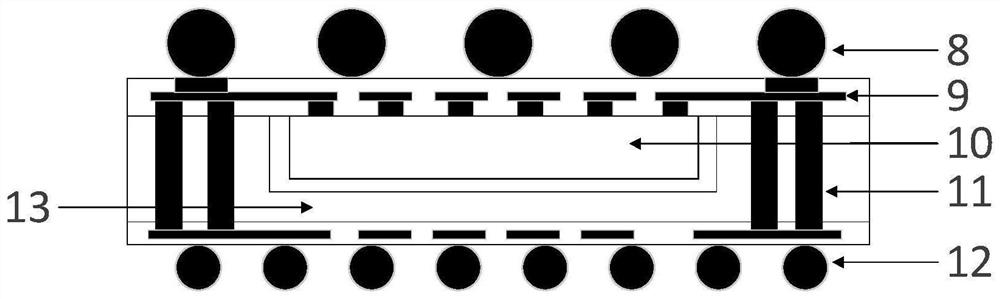

Interconnection test fixture and interconnection test method for silicon adapter plate

ActiveCN112394202AImprove securityHold steadyElectric connection testingShort-circuit testingShort-circuit testOpen-circuit test

The invention belongs to the technical field of advanced electronic packaging, and discloses an interconnection test fixture and an interconnection test method for a silicon adapter plate, the test fixture comprises a fixture body and a plurality of silica gel pads, the fixture body is provided with a through hole and a vacuum joint, the inner wall of the through hole is provided with a wafer placing ring, and the wafer placing ring is provided with a plurality of cavities; a vacuum adsorption groove and a plurality of mounting holes are formed in the cavity; a plurality of vacuum holes and aplurality of protrusions are arranged on the silica gel pad, the protrusions are connected with the installation holes respectively, and the vacuum holes are communicated with the vacuum adsorption groove. The test method comprises the following steps: acquiring test data on a to-be-tested silicon adapter plate; according to the test data on the to-be-tested silicon adapter plate, setting the placement position of the silicon adapter plate and loading the to-be-tested silicon adapter plate on the interconnection test fixture; and generating an open-circuit test scheme and a short-circuit testscheme of each test point network for testing. The risk of cracking is effectively avoided, direct testing is adopted, light and reliable contact is guaranteed, product damage is avoided, and subsequent technological machining is not affected.

Owner:珠海天成先进半导体科技有限公司

Monitoring method, attachment equipment and panel

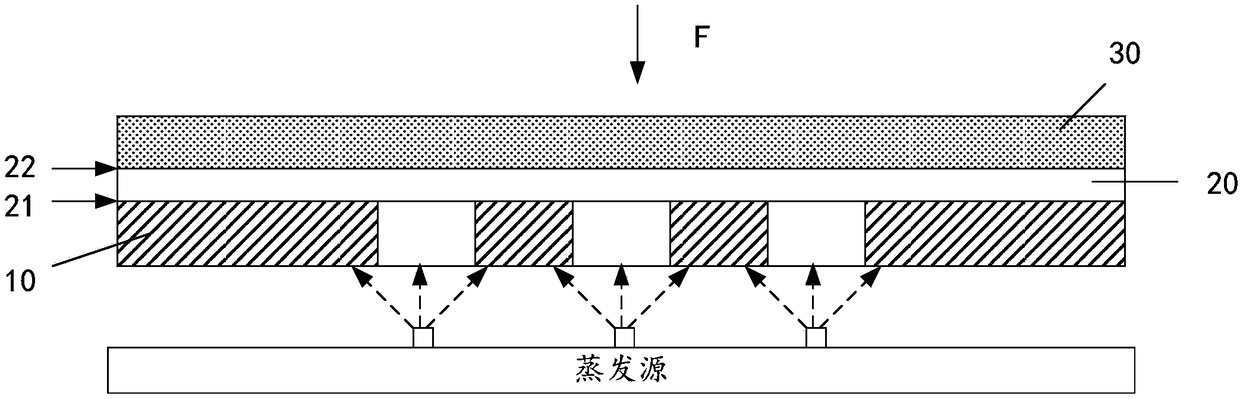

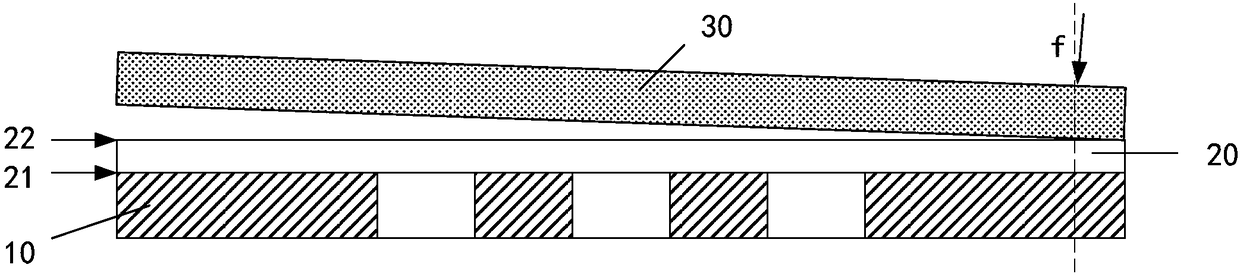

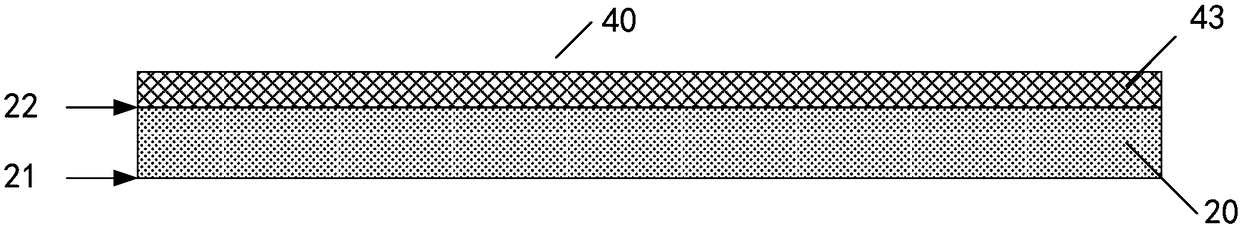

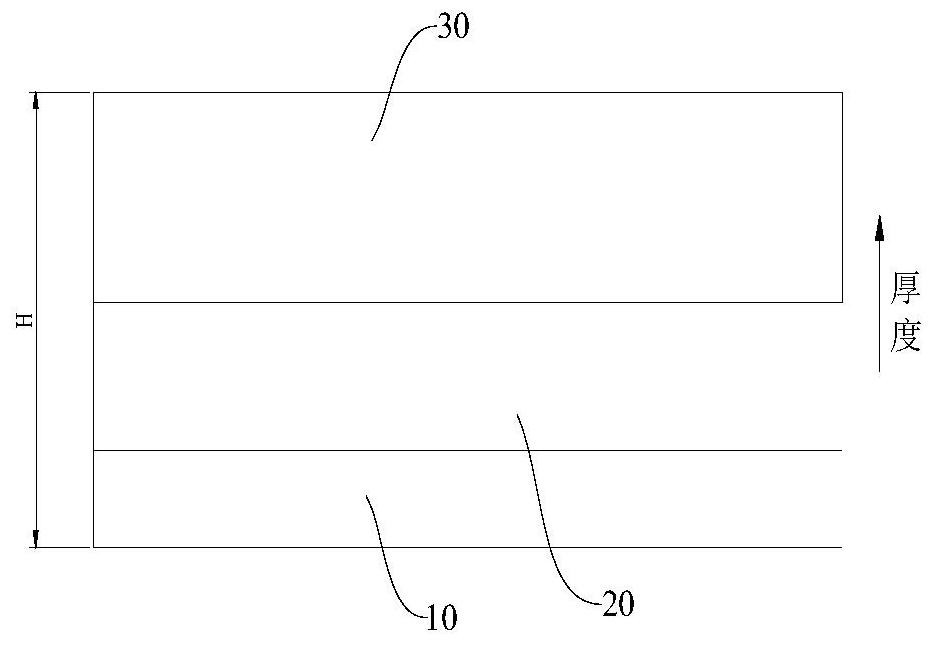

InactiveCN108461413AForce real-time monitoringAvoid Fragmentation RiskSemiconductor/solid-state device testing/measurementSolid-state devicesEngineeringSurface plate

The invention provides a monitoring method, attachment equipment and a panel. By the monitoring method, the attachment equipment and the panel, a breakage risk caused by that stress applied onto a glass substrate is not within an error-allowable range during the fabrication process of an OLED display panel is reduced. The monitoring method comprises the steps of detecting pressure values of a plurality of points by a piezoelectric sensing thin film arranged between a lamination plate and a substrate; determining whether the stress applied to the substrate by the lamination plate is within theerror-allowable range or not according to the pressure values of the plurality of points; and controlling running of the lamination plate according to the situation whether the pressure is within theerror-allowable range or not so that the substrate is uniformly pressed on a mask.

Owner:YUNGU GUAN TECH CO LTD

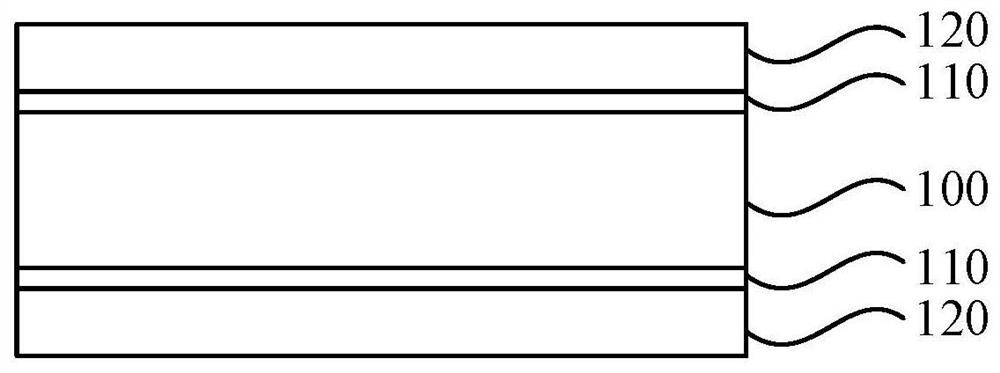

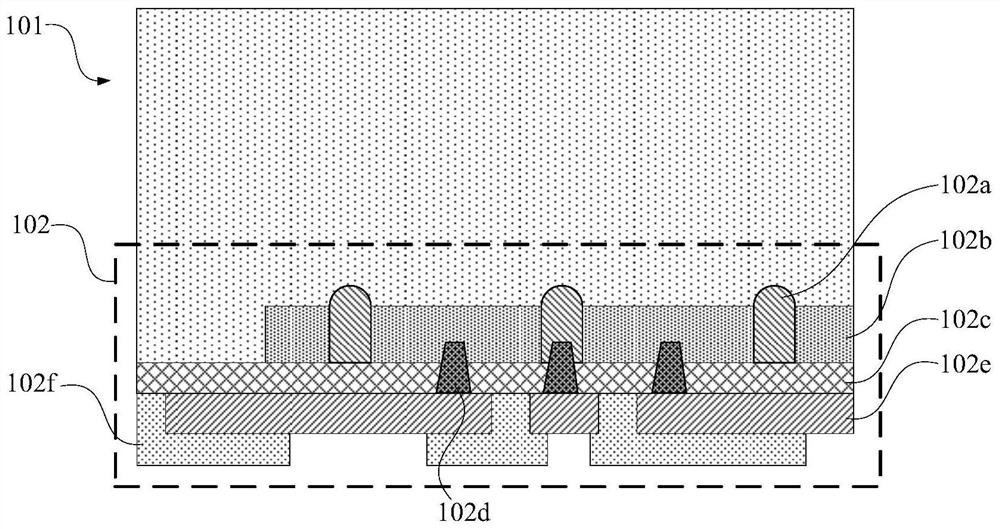

Substrate, semiconductor device and preparation method thereof

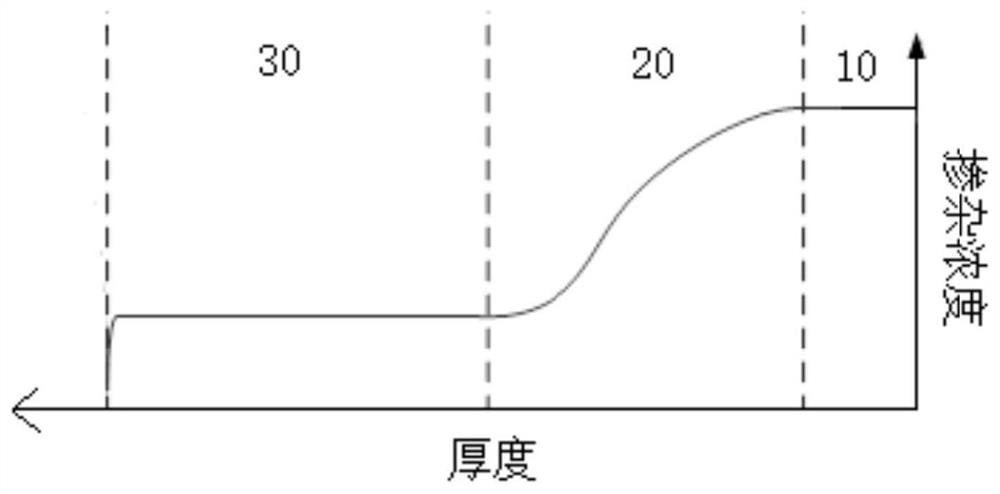

PendingCN112582469AAvoid Fragmentation RiskImprove processing efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesSoft switchingDevice material

The invention provides a substrate, a semiconductor device and a preparation method of the semiconductor device, and the substrate comprises a first cut-off layer, wherein the doping concentration ofthe first cut-off layer is uniformly distributed in the thickness direction; a second cut-off layer which is arranged on one surface of the first cut-off layer, wherein the doping concentration in thesecond cut-off layer is gradually reduced in the direction away from the first cut-off layer; a drift region which is arranged on the surface, away from the first cut-off layer, of the second cut-offlayer, wherein the doping concentration in the drift region is smaller than or equal to that in the second cut-off layer. A device comprising the substrate has a good soft switching characteristic inthe switching process, does not have too high peak current and voltage, and has better consistency and stability.

Owner:BYD SEMICON CO LTD

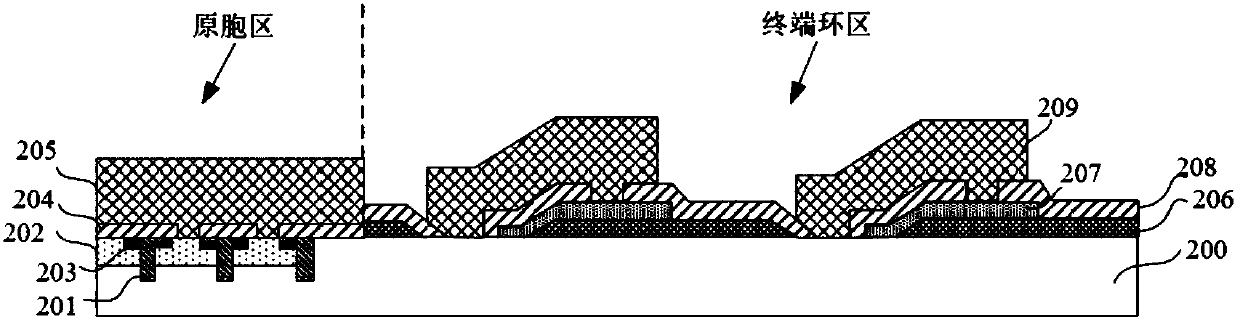

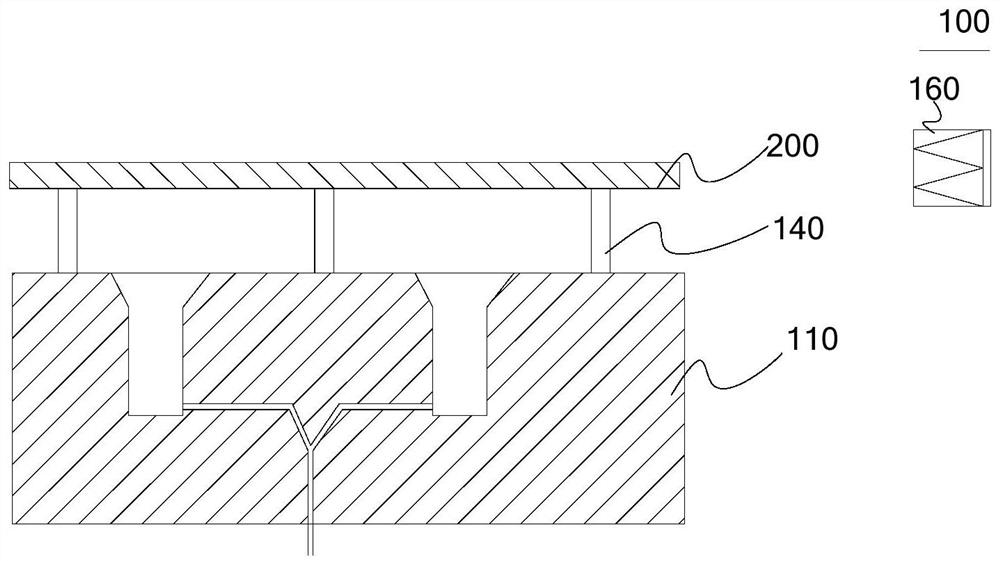

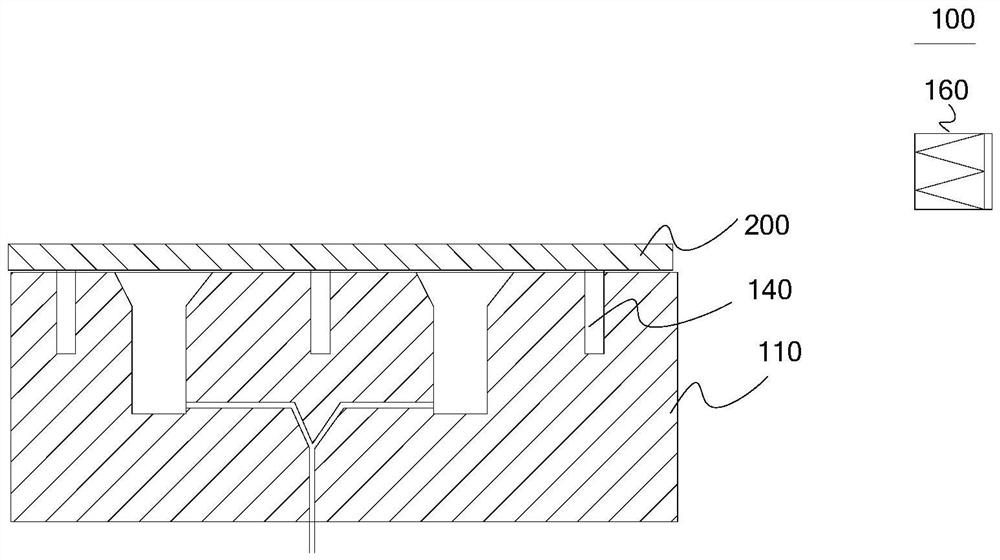

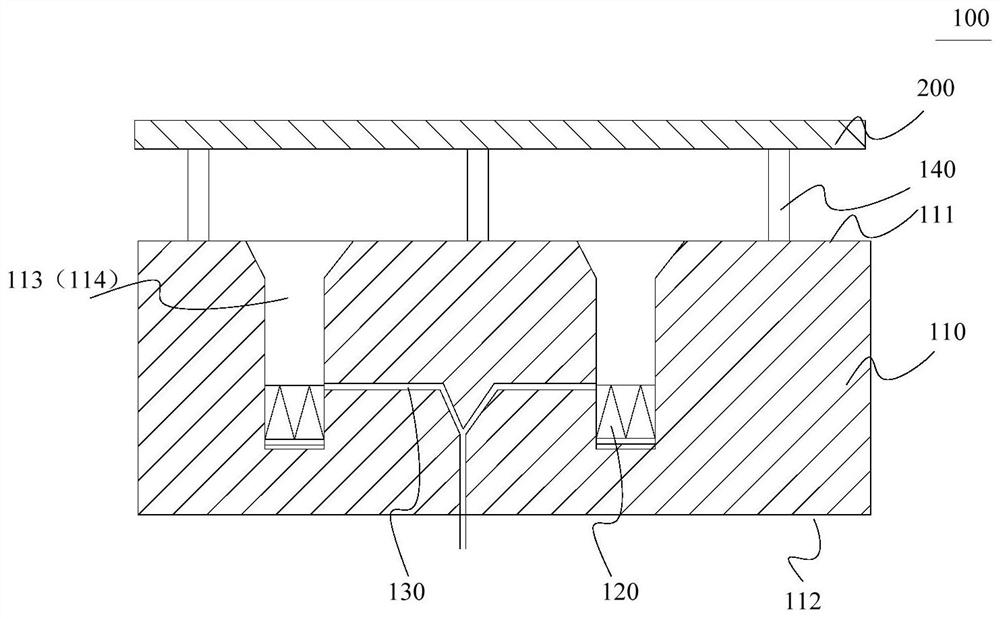

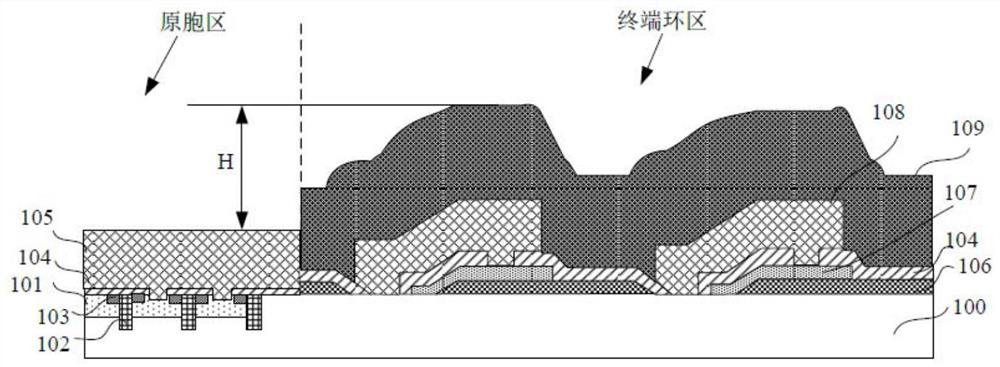

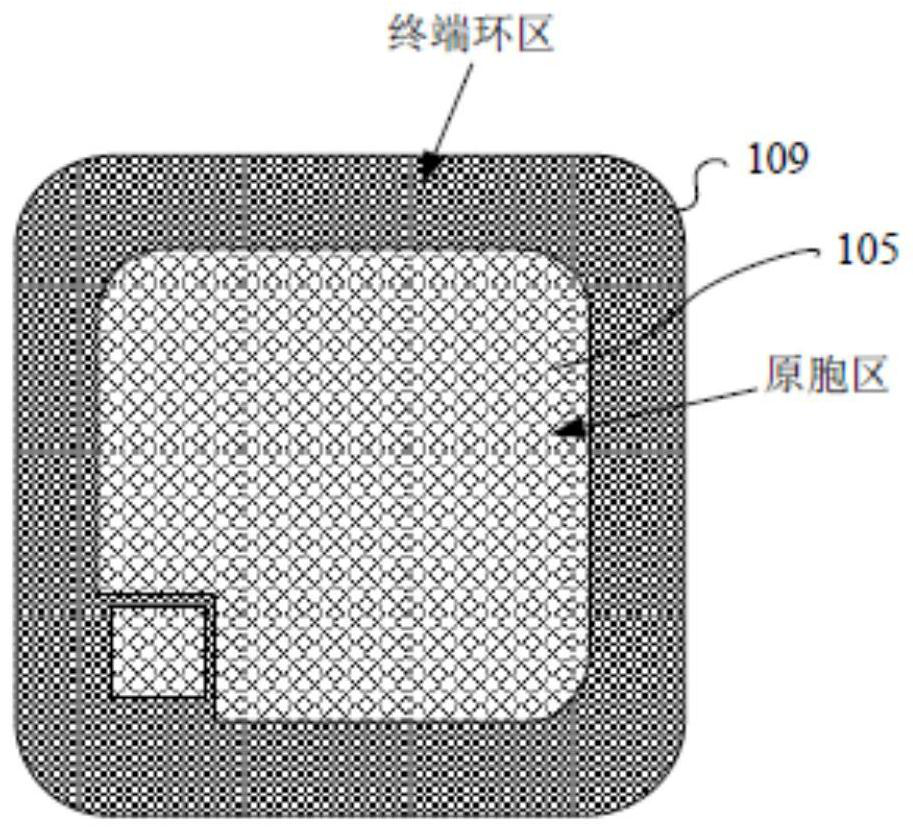

Semiconductor device manufacturing method, semiconductor device and electronic device

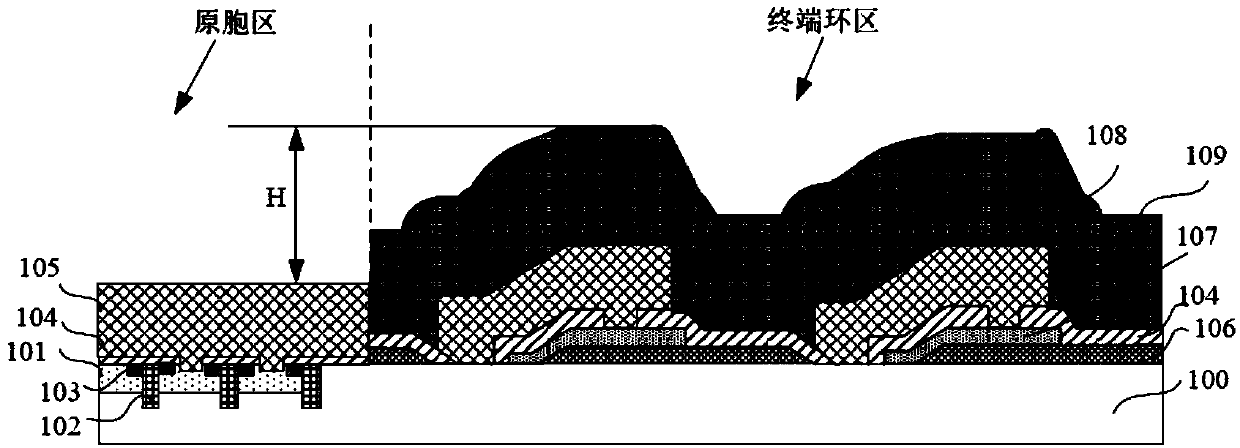

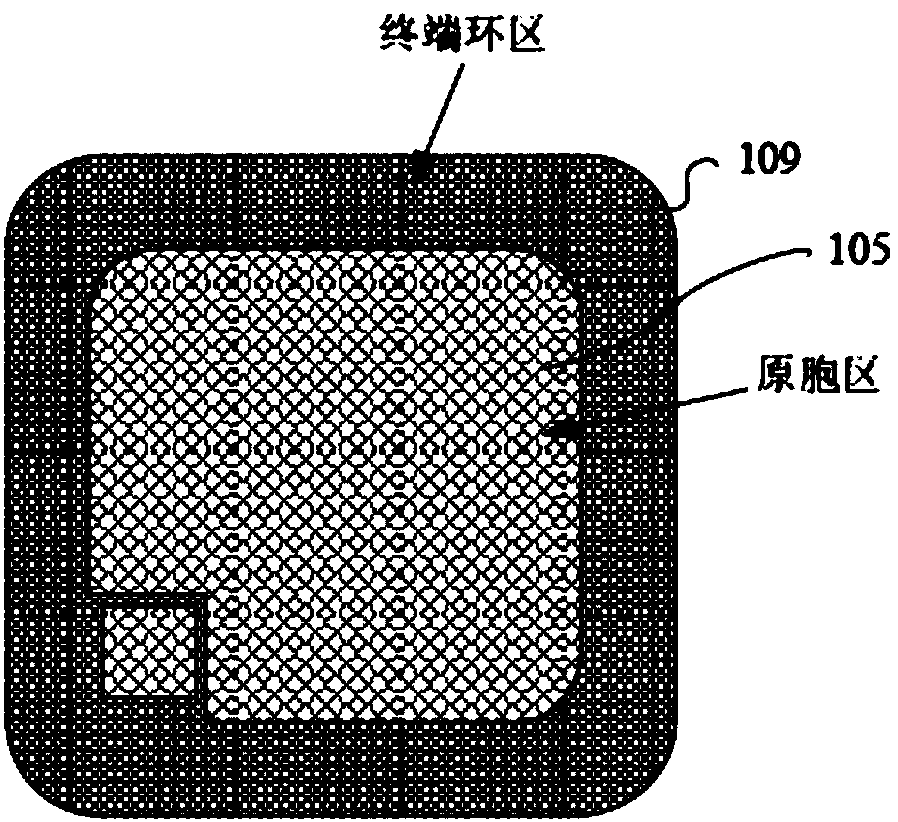

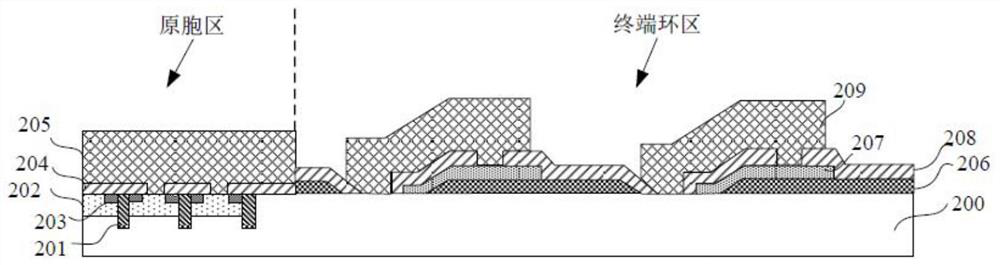

ActiveCN109994388AReduce failureReduce height differenceSemiconductor/solid-state device detailsSolid-state devicesCell regionEngineering

The invention provides a semiconductor device manufacturing method, a semiconductor device and an electronic device; the method comprises the following steps that a semiconductor substrate is provided, wherein a terminal ring region and a cell region are formed on the semiconductor substrate; and a protective layer for covering the terminal ring region and a supporting structure positioned on thecell region are formed on the semiconductor substrate, wherein the top of the supporting structure is lower than the top of the protective layer or is flush with the top of the protective layer. According to the manufacturing method of the semiconductor device, the semiconductor device and the electronic device, the supporting structure located in the cell region is formed on the semiconductor substrate, so that the height difference between the top of the cell region structure and the top of the structure of the terminal ring region is reduced before the back surface of a wafer is thinned, afilm stripping process and fragment risk due to the film stripping process caused by using an organic protective film as a buffer layer in the subsequent grinding thinning process can be avoided, theprocess flow is simplified, and meanwhile, the generation of fragments or micro-cracks is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

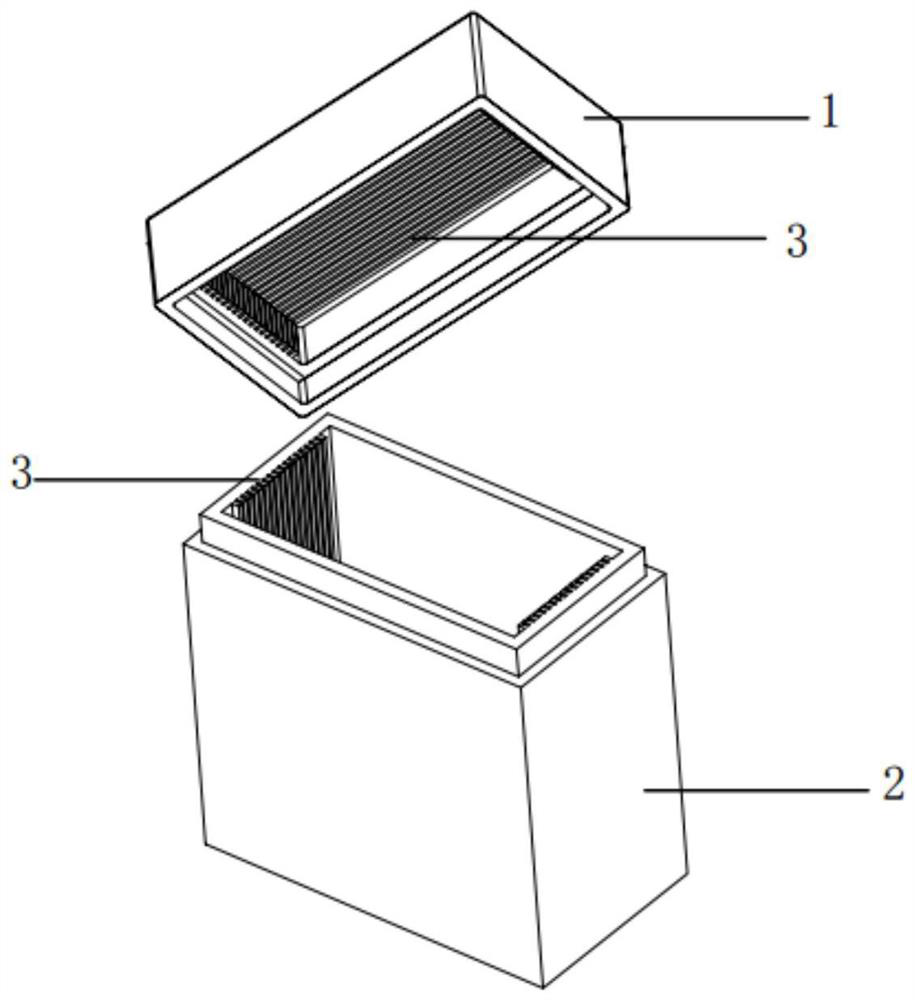

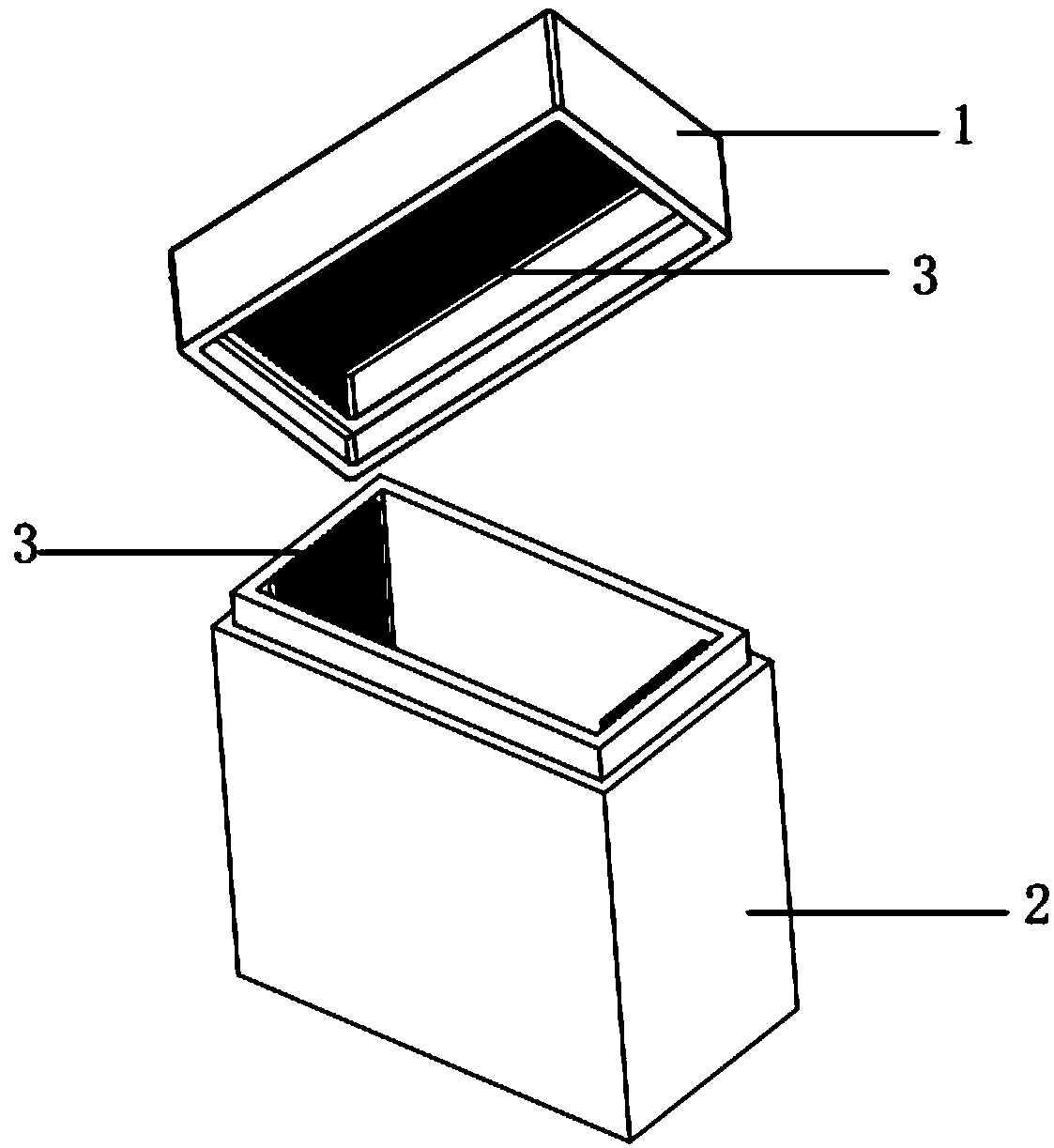

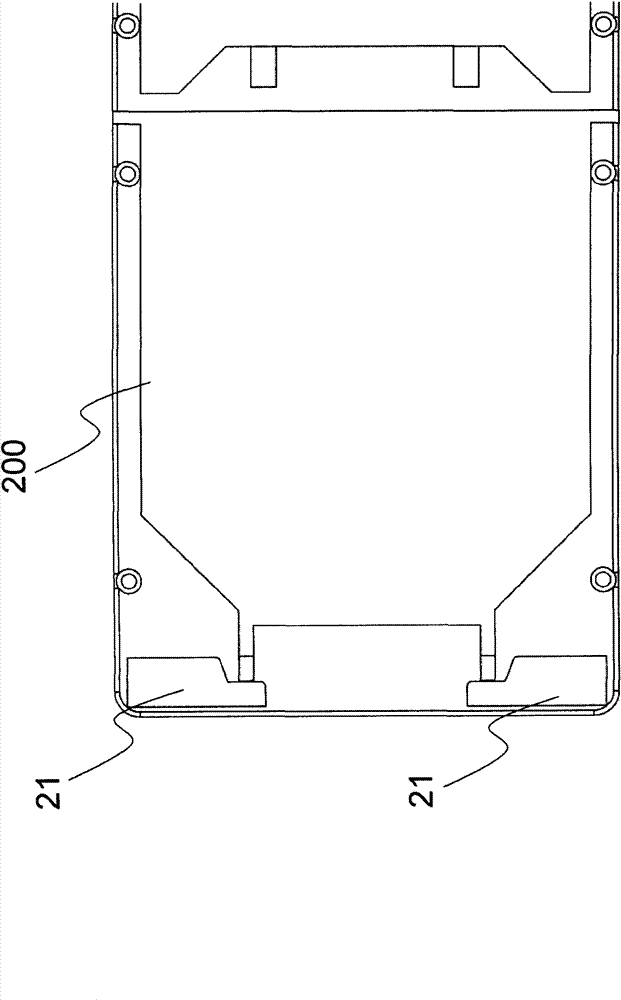

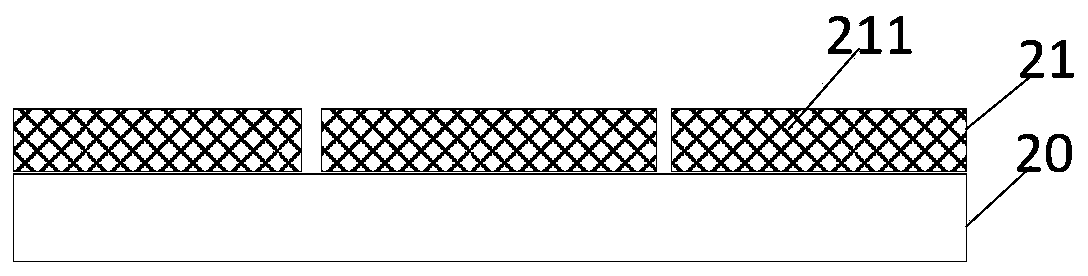

A packaging box for LCD panels

ActiveCN109335228BEasy to countEasy to fixDamagable goods packagingInternal fittingsEngineeringStructural engineering

The invention provides a liquid crystal panel packaging box, which includes a box cover and a box body, at least one counting insert and a plurality of quadrangular spacers are arranged inside the box body, and at least one groove is arranged on the inner wall of the box body , the counting insert is fixed in the groove; the four corners inside the box are rounded, and at least two corners of each spacer are provided with circular lugs, and the circular lugs are fixed within the corresponding rounded corners of the box. The present invention facilitates packing and counting of the liquid crystal panel by adding a number plug-in on the side wall of the box body; by setting a circular lug structure on the spacer and fixing it on the corner of the box body, it is convenient to fix the spacer when the liquid crystal panel is boxed , and thus effectively prevent the risk of fragmentation that may occur due to the failure of the limit during the packing and transportation of the LCD panel.

Owner:NANJING BOE DISPLAY TECH CO LTD

Liquid crystal panel packaging box

ActiveCN109335228AEasy to countEasy to fixDamagable goods packagingInternal fittingsLiquid-crystal displayEngineering

The invention provides a liquid crystal panel packaging box. The liquid crystal panel packaging box comprises a box cover and a box body. The box body is internally provided with at least one countinginserting piece and a plurality of quadrangular spacing pieces, at least one groove is formed in the inner wall of the box body, and the counting inserting pieces are fixed in the grooves. The four corners inside the box body are rounded corners, at least two corners of each spacing piece are provided with a circular hanging lug, and the circular hanging lugs are fixed in the corresponding rounded corners of the box body. According to the liquid crystal panel packaging box, the counting inserting pieces are additionally arranged on the side wall of the box body, so that boxing counting of liquid crystal panels is facilitated; and the circular hanging lug structures are arranged on the spacing pieces and fixed to the corners of the box body, the fixation of liquid crystal panel packaging time spacing pieces is facilitated, and thus the risk of piece breakage caused by limiting failure during the packing and transport process of the liquid crystal panels can be effectively prevented.

Owner:NANJING CEC PANDA FPD TECH CO LTD

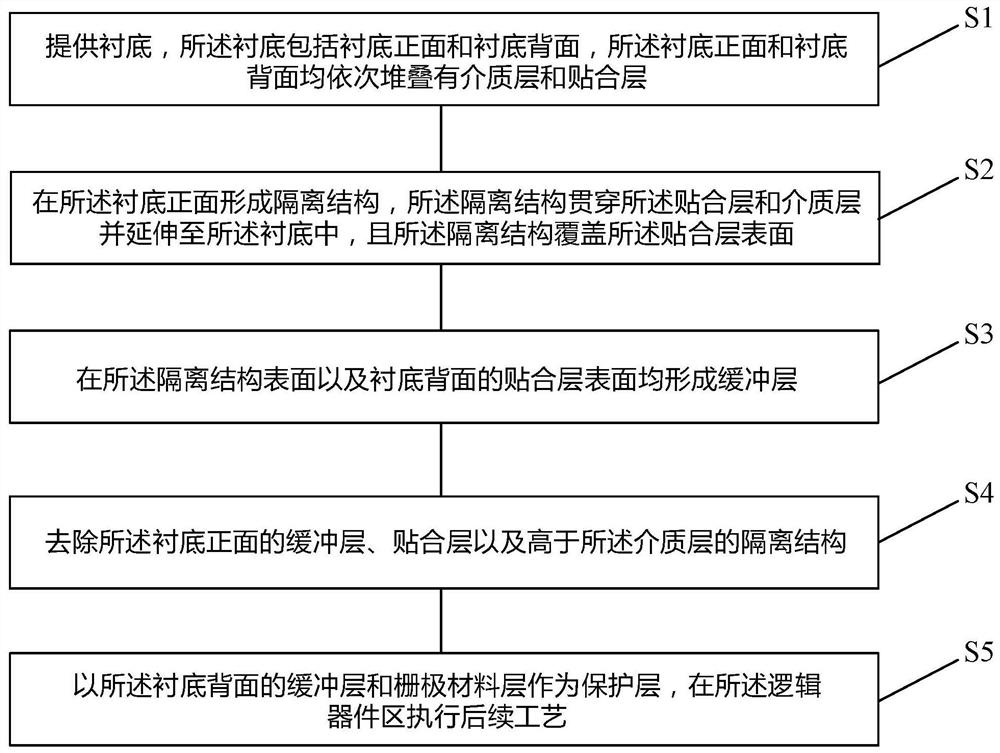

Semiconductor structure and forming method thereof

PendingCN114497088ASo as not to damageIntegrity guaranteedSolid-state devicesDiodeSemiconductor structureWafer

The invention provides a semiconductor structure and a forming method thereof, and the method comprises the steps: providing a substrate which comprises a substrate front surface and a substrate back surface, and the substrate front surface and the substrate back surface are each sequentially provided with a dielectric layer and a bonding layer in a stacked manner; an isolation structure is formed on the front face of the substrate, the isolation structure penetrates through the attaching layer and the dielectric layer and extends into the substrate, and the isolation structure covers the surface of the attaching layer; forming buffer layers on the surfaces of the isolation structures and the surfaces of the bonding layers on the back surface of the substrate; removing the buffer layer, the bonding layer and the isolation structure higher than the dielectric layer on the front surface of the substrate; forming gate material layers on the surfaces of the dielectric layer and the isolation structure on the front surface of the substrate and the surface of the buffer layer on the back surface of the substrate; and taking the buffer layer and the gate material layer on the back surface of the substrate as protective layers, and executing subsequent processes in the logic device region. According to the technical scheme, the bonding layer can be protected from being damaged, the integrity of the bonding layer is ensured, and the performance and the yield of the logic wafer are improved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

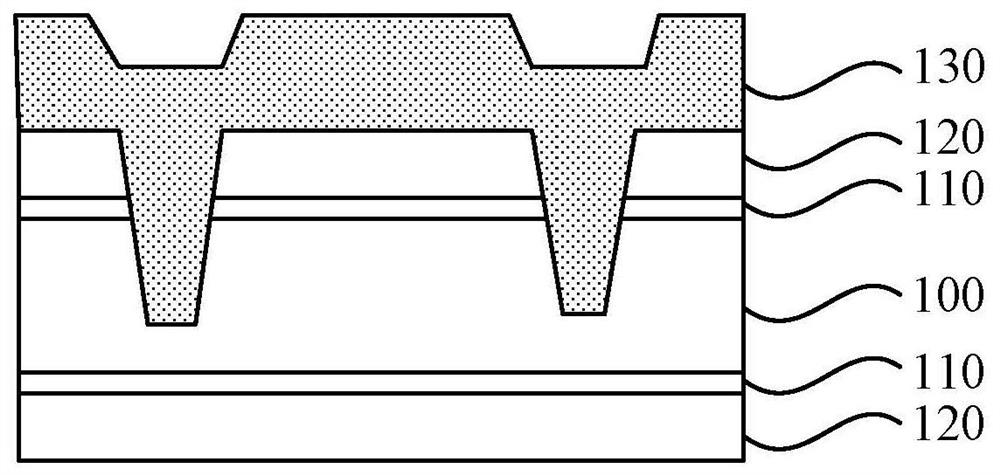

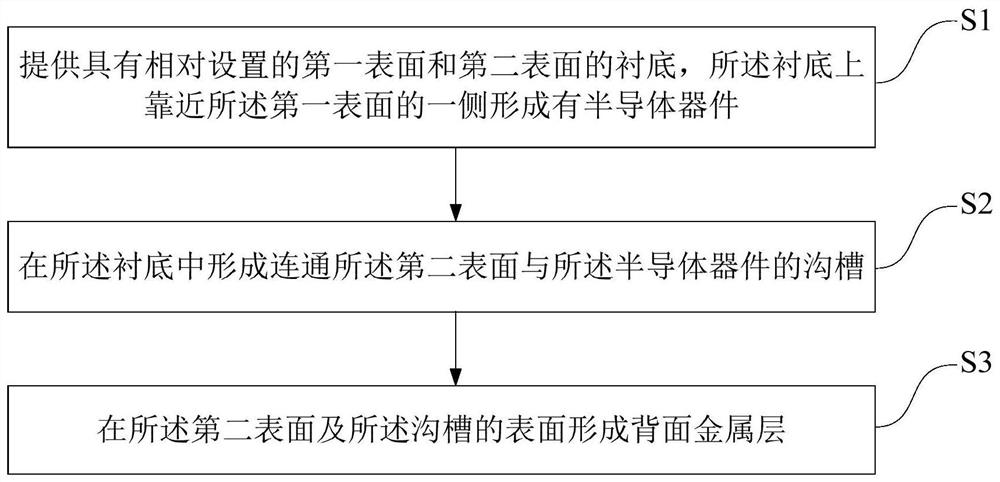

Back metallized semiconductor structure and preparation method thereof

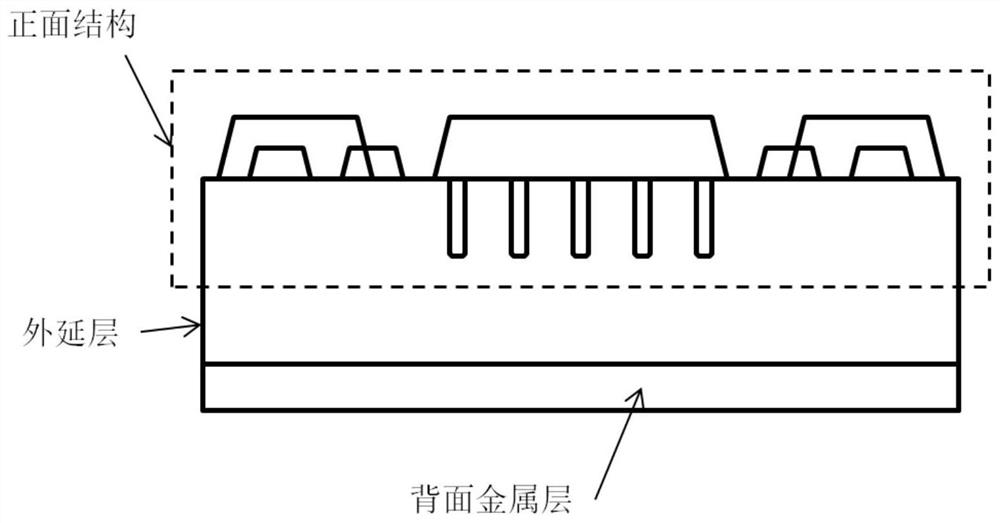

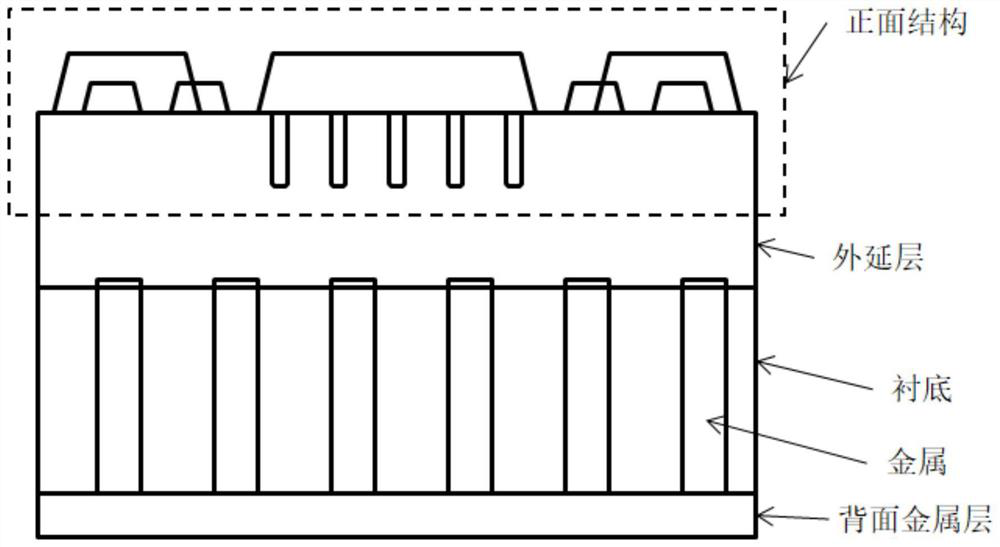

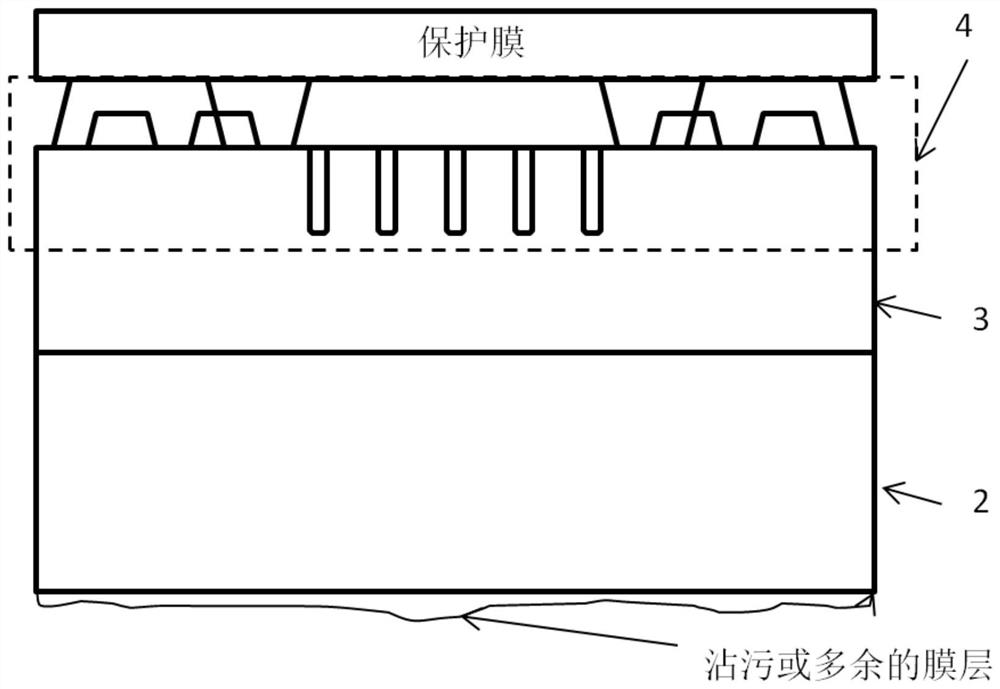

ActiveCN112017967AAvoid Fragmentation RiskImprove yieldSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureWafer

The invention provides a back metallized semiconductor structure and a preparation method thereof, and the preparation method of the back metallized semiconductor structure comprises the following steps: providing a substrate with a first surface and a second surface which are oppositely arranged, and forming a semiconductor device at one side, close to the first surface, of the substrate; forminga groove for communicating the second surface with the semiconductor device in the substrate; and forming a back metal layer on the second surface and the surface of the groove. According to the invention, the groove and the back metal layer are formed on the back surface of the wafer, so that the original back thinning and metallization process is replaced, the fragment risk caused by back thinning is avoided, the product yield is further improved, and the product production cost is reduced.

Owner:SIEN QINGDAO INTEGRATED CIRCUITS CO LTD

Substrate Stages and Exposure Machines

ActiveCN108279552BEffective protectionAvoid Fragmentation RiskPhotomechanical exposure apparatusMicrolithography exposure apparatusIonic ChannelsMechanical engineering

The invention discloses a substrate carrier and an exposure machine. The substrate carrier includes: a body, including a first surface and a second surface oppositely arranged, the first surface is used to carry the substrate, and the first surface is provided with at least one ion channel; at least one first static eliminator, each first The static eliminator corresponds to at least one ion channel, and the first static eliminator is connected to the corresponding ion channel to provide static elimination ions into the ion channel. Through the function of the set ion channel and the first static eliminator corresponding to the ion channel, the static electricity generated on the surface in contact with the substrate and the substrate carrier can be eliminated, thereby eliminating the electrostatic adsorption force between the substrate and the substrate carrier , so that the substrate and the substrate carrier can be easily peeled off. Therefore, in the process of peeling the substrate from the substrate carrier, the substrate can be effectively protected, the risk of debris during the peeling of the substrate can be effectively avoided, the production yield of the substrate can be improved, and the production cost can be reduced.

Owner:BOE TECH GRP CO LTD +1

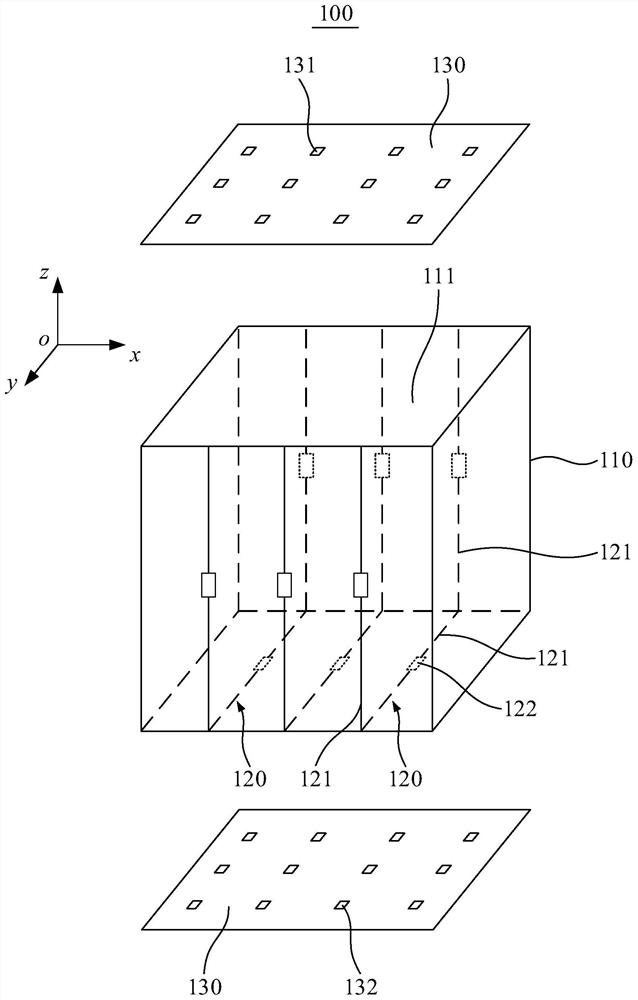

Wafer multilayer stacking bonding method

PendingCN114050110AAvoid the risk of fragmentationImprove assembly efficiencySolid-state devicesSemiconductor/solid-state device manufacturingHigh densityWafer thinning

The invention discloses a multilayer stacking bonding method for wafers, and belongs to the technical field of semiconductor integrated packaging. The bonding sequence is as follows: first layer, second layer wafer front process; first layer, second layer wafer bonding; one side wafer thinning and backside process; other side wafer thinning and backside process; third layer wafer front process and second and third layer wafer bonding ; and third layer wafer thinning and backside process, and a solution is provided for multilayer bonding of the thin wafer. According to the method, bonding of multiple layers of wafers can be carried out without additionally adding a slide glass, the number of layers of the bonded wafers is increased layer by layer according to the mutual bearing effect of the bonded wafers, and the risk that the wafers are cracked due to the fact that temporary bonding glue is denatured and difficult to unbond is avoided. Besides, compared with single-chip stacking, the method has the advantages that the assembling efficiency is remarkably improved, the method is an efficient multi-layer wafer level homogeneous or heterogeneous high-density integration method, the application prospect and market potential are very wide, and important strategic significance and social benefits are achieved.

Owner:XIAN MICROELECTRONICS TECH INST

A kind of substrate arrangement cache device

ActiveCN110534665BGuaranteed stabilityIncrease productivitySolid-state devicesSemiconductor/solid-state device manufacturingRobot handEngineering

The present invention relates to the technical field of OLED packaging, and in particular to a substrate arrangement and buffer device, which is used to store abnormal substrates by setting the arrangement and buffer device, and cooperates with the processor by setting the extraction device to detect the glue coating device and the pressing pair. When there is an abnormality in the substrate in the assembly device and the frame glue curing device, the horizontal turntable is controlled to rotate to the corresponding position, and the manipulator is driven to take out the abnormal substrate and put it into the buffering device, which avoids the risk of fragmentation during the OLED packaging process, thereby improving OLED. Panel production efficiency and ensure the continuity of production.

Owner:FUJIAN HUAJIACAI CO LTD

Crystal boat converter

InactiveCN102543794BAvoid Fragmentation RiskSemiconductor/solid-state device manufacturingConveyor partsEngineeringElectrical and Electronics engineering

Owner:CHIPMOS TECH INC

Power semiconductor device and manufacturing process thereof

PendingCN112397380AAvoid Fragmentation RiskLow costSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceDevice material

The invention relates to the technical field of power semiconductor devices, in particular to a power semiconductor device and a manufacturing process thereof. The manufacturing process of the power semiconductor device comprises the following steps of depositing an epitaxial layer on the front surface of a substrate and finishing the manufacturing of a front surface structure of the power semiconductor device; etching the back surface of the substrate to etch through the whole substrate until reaching the epitaxial layer to form a lead hole; and loading metal in the lead hole, forming a backmetal layer on the back surface of the substrate through cushion accumulation, annealing alloy, and leading the epitaxial layer to the back metal layer through a metal lead. According to the process,the substrate does not need to be thinned, and the back electrode is led out by adopting a lead hole technology. On the basis of not influencing the welding process and the electrical property of thepower semiconductor device, the thinning process is canceled, the substrate is reserved as a support, the fragmentation risk caused by the thinning process and the subsequent slice manufacturing process is avoided, and the cost is saved.

Owner:GREE ELECTRIC APPLIANCES INC

A semiconductor production process control system and analysis method

InactiveCN105470163BAvoid Fragmentation RiskGuaranteed yieldSemiconductor/solid-state device manufacturingOriginal dataControl system

The invention discloses a manufacturing process control system and an analysis method, which belong to the technical field of semiconductor manufacturing process management and control. The semiconductor manufacturing process control system comprises an acquisition unit, a first storage unit, a processing unit and an alarm unit, wherein the acquisition unit acquires wafer original data; the first storage unit stores the wafer original data; the processing unit extracts the wafer original data and processes the wafer original data to obtain multiple groups of grouped data, and analyzes and outputs a variation trend of the grouped data; and the alarm unit receives an analysis result and outputs an alarm signal. The analysis method comprises the steps of: acquiring the wafer original data and storing the wafer original data in the first storage unit; extracting the wafer original data from the first storage unit, and processing the wafer original data to obtain the corresponding grouped data and dividing the grouped data into groups; and analyzing the variation trend of the grouped data, and outputting the analysis result to the alarm unit for alarm. The semiconductor manufacturing process control system and the analysis method have the beneficial effects of reducing alarm time delay and omission, avoiding fragment risk of products, and ensuring product yield.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Manufacturing method of semiconductor device, semiconductor device and electronic device

ActiveCN109994388BReduce failureReduce height differenceSemiconductor/solid-state device detailsSolid-state devicesDevice materialCell region

The present invention provides a method for manufacturing a semiconductor device, a semiconductor device and an electronic device. The method includes: providing a semiconductor substrate on which a terminal ring region and a cell region are formed; A protective layer covering the terminal ring area and a support structure located on the cell area are formed on the top, wherein the top of the support structure is lower than the top of the protective layer or is flush with the top of the protective layer. According to the manufacturing method of the semiconductor device, the semiconductor device and the electronic device of the present invention, the support structure located in the cell region is formed on the semiconductor substrate, which reduces the gap between the top of the cell region structure and the top of the terminal ring region structure before the back of the wafer is thinned. The height difference avoids the risk of debris caused by the peeling process and the peeling process caused by using the organic protective film as a buffer layer in the subsequent grinding and thinning process, and reduces the occurrence of debris or microcracks while simplifying the process.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method for laser polishing glass and polishing method for glass hole and glass sheet

ActiveCN112404736BAvoid Fragmentation RiskImprove mechanical propertiesGlass severing apparatusLaser beam welding apparatusGlass chipCw laser

The invention provides a method of laser polishing glass and the polishing method of glass holes and glass sheets.Including the following steps: After the first laser is used to expose the cutting contour set on the glass plate, the glass is disconnected along the cut contour line; the second laser edge near the cut contour line of 0.3‑1.2mm to illuminate,Make the glass on both sides of the polishing contour evaporation and get polished glass products; the second laser is CO 2 Continuous laser.The present invention can solve the slight cracks and defects caused by the cut surface caused by conventional cutting methods; 2 Continuous laser directly illuminate the polishing contour line, so that the vitreous body evaporation and removal of the polishing contour lines on both sides of the outline, obtain a smooth glass side broken surface to improve the performance of glass mechanics;The quality of the plane solves the potential risk of subsequent processes.

Owner:KORNERSTONE MATERIALS TECH

A wafer debonding method

ActiveCN111755377BSolve the problem that the debonding cannot be carried out smoothlyAvoid Fragmentation RiskSolid-state devicesSemiconductor/solid-state device manufacturingPhysical chemistryEngineering

A method for unbonding thin wafers, comprising the following steps: Step 1, etching and removing the silicon where the outer ring of the silicon wafer undergoes glue denaturation or glue overflow; and Step 2, unbonding the silicon wafer and the carrier. The etching removal method described in step 1 includes preparing a mask layer on the side of the wafer. The material of the mask layer is positive or negative photoresist, and the photoresist at the edge of the silicon wafer is removed through the exposure and development process. ; and then directly etch the outer ring of the silicon wafer through a dry etching process. Aiming at the problems of temporary bonding glue degeneration and "glue extrusion" of thin wafers, the present invention adopts a pre-treatment method for de-bonding, through pre-treatment processes such as mask preparation, etching and edge removal, etc. The silicon etching and removal of the glue overflow, and then the debonding process, solves the problem that the debonding cannot be carried out smoothly due to the denaturation of the temporary bonding glue, and avoids the risk of debris.

Owner:珠海天成先进半导体科技有限公司

Silicon-based liquid crystal cleaning device and cleaning method

ActiveCN114713545APrevent fallingAvoid Fragmentation RiskFinal product manufactureDrying gas arrangementsCrystallographyPhysical chemistry

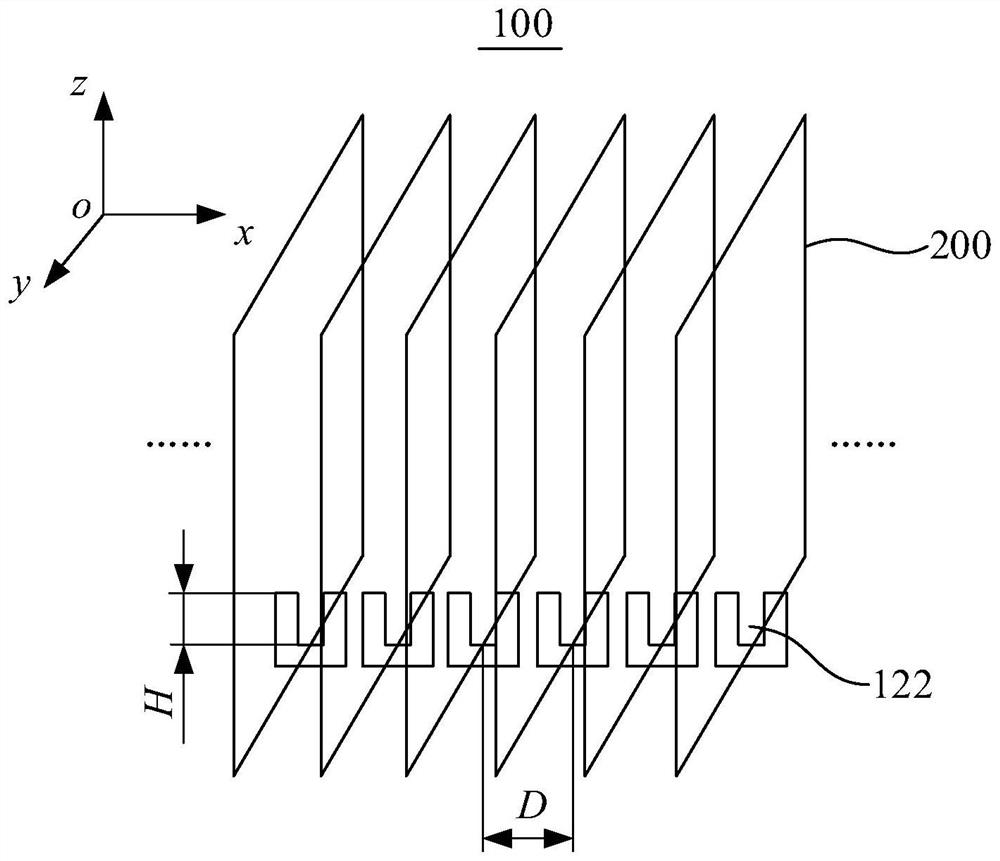

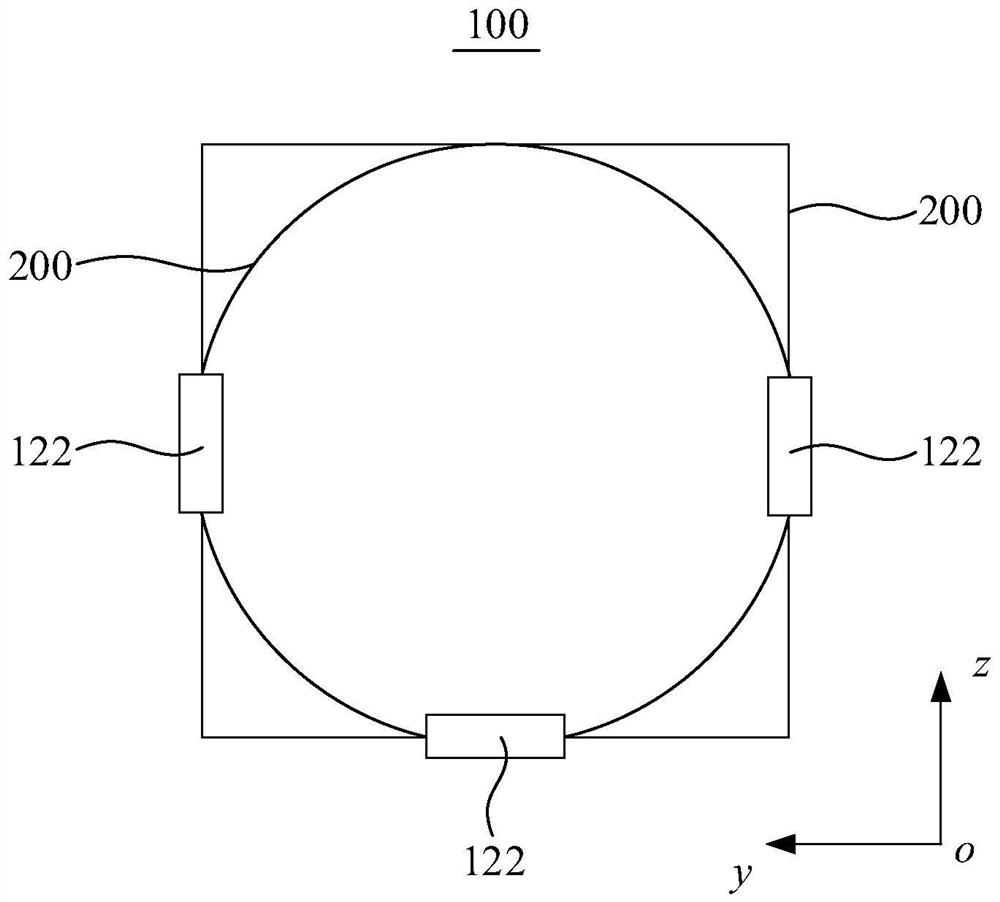

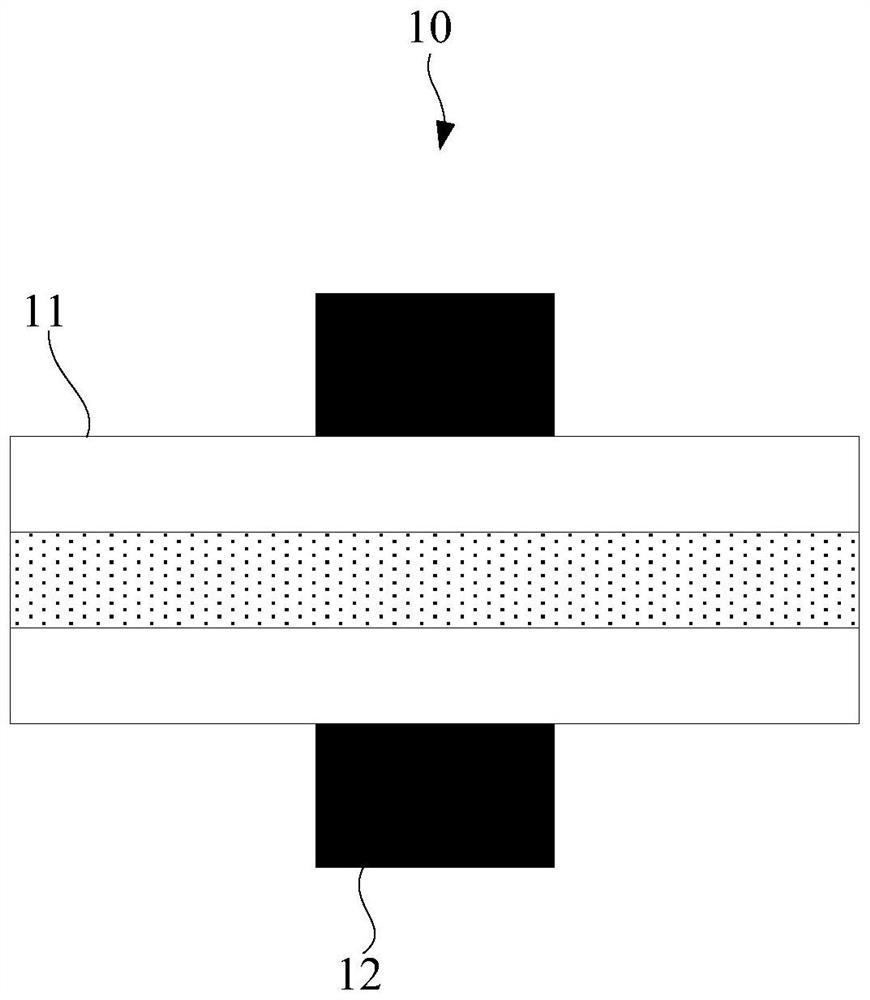

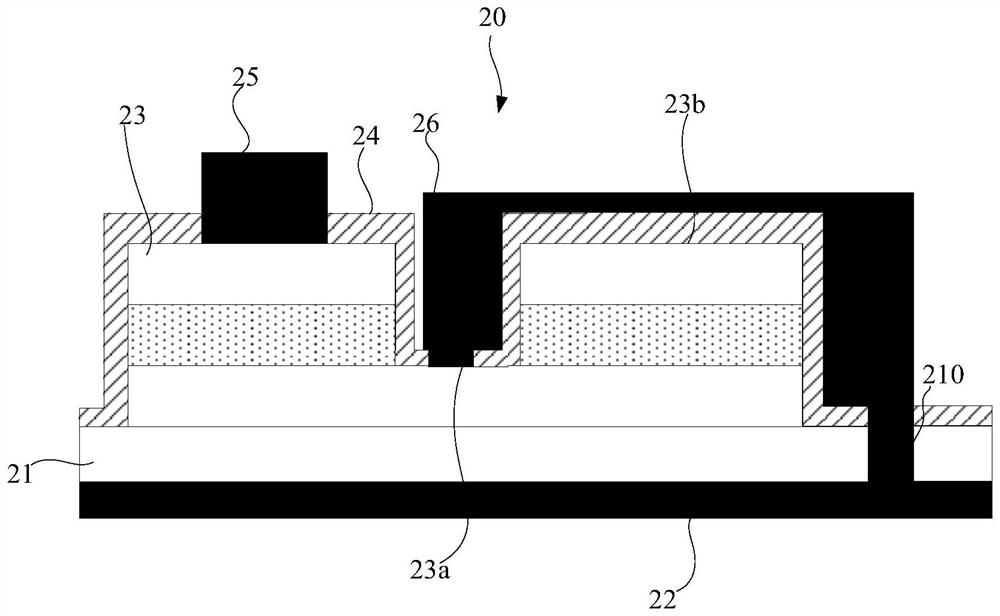

The invention discloses a silicon-based liquid crystal cleaning device and a cleaning method, and relates to the technical field of silicon-based liquid crystal product.The silicon-based liquid crystal cleaning device comprises a rectangular frame with a containing space and a plurality of U-shaped fixing frames which are arranged on the rectangular frame around the containing space and arranged at intervals in the first direction; the plane where the fixing frame is located is perpendicular to the first direction, the fixing frame comprises three sub-supports which are sequentially connected, clamping grooves are formed in the three sub-supports correspondingly, and groove openings of the clamping grooves face the containing space correspondingly; the cleaning assembly and the rectangular frame are sequentially distributed in the second direction perpendicular to the first direction. According to the silicon-based liquid crystal cleaning device provided by the invention, scratches and scratches on the surface of the silicon-based liquid crystal in the cleaning process can be avoided, the risk of fragment is reduced, and the cleaning yield and the cleaning efficiency are improved.

Owner:南京芯视元电子有限公司

Vertical LED chip and preparation method thereof, LED array and display panel

PendingCN114188453ASimple processImprove production yieldSemiconductor devicesLed arrayElectrical connection

The invention relates to a vertical LED chip and a preparation method thereof, an LED array and a display panel. In the vertical LED chip, a conductive layer is arranged on one side, opposite to an epitaxial layer, of a substrate, a through hole is formed in the substrate, and a connecting band can penetrate through a P-type table top and penetrate through the through hole to realize electric connection between an N-type semiconductor layer and the conductive layer, so that the conductive layer is used as an actual N electrode of the vertical LED chip. Under the condition, the N electrode is arranged without stripping the epitaxial layer from the substrate or bonding the epitaxial layer to other substrates, so that the production process of the vertical LED chip is simplified, the production efficiency is improved, the fragment risk caused by the transfer of the epitaxial layer can be avoided, and the production yield of the LED chip is improved.

Owner:CHONGQING KONKA PHOTOELECTRIC TECH RES INST CO LTD

Display panel and manufacturing method thereof

InactiveCN111081735AReduce warpageAvoid Fragmentation RiskFinal product manufactureSolid-state devicesThin membraneComposite material

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

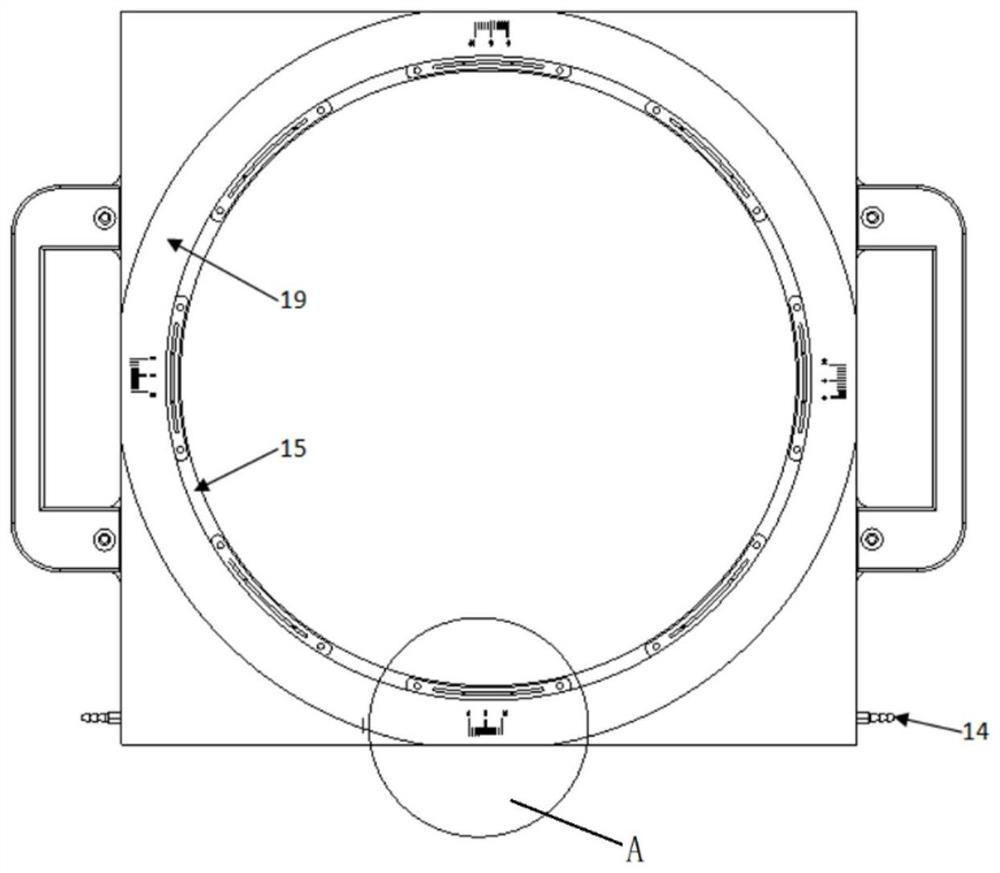

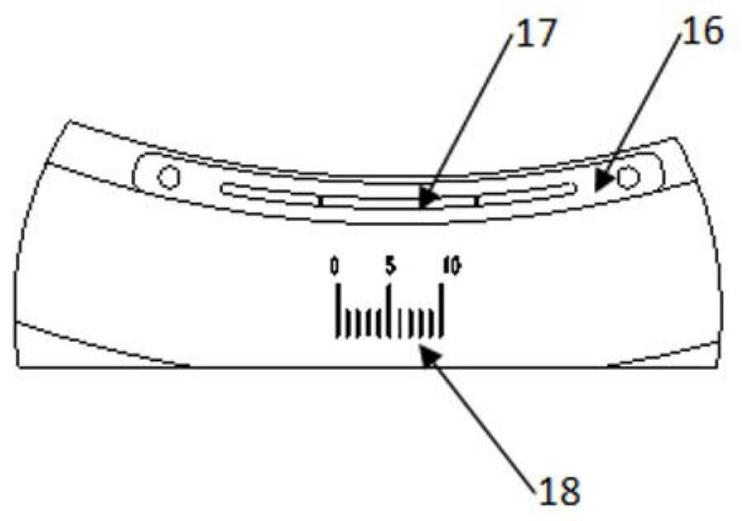

Interconnection test fixture and interconnection test method for silicon-based component

PendingCN114414978AAchieve universalEasy to useMeasurement instrument housingIndividual semiconductor device testingTest fixtureElectronic packaging

The invention discloses an interconnection test fixture and an interconnection test method for a silicon-based component, and belongs to the technical field of advanced electronic packaging, the interconnection test fixture for the silicon-based component comprises a vacuum adsorption hole, an X-axis limiting baffle block, a Y-axis limiting baffle block and a test area Z plane regulator, and realizes three-dimensional regulation of a tested piece. The problems of clamping and compatibility of different silicon-based assemblies are solved, the fragment risk is avoided, and the purposes that the test fixture is universal and convenient to use are achieved; according to the interconnection test method, direct current and alternating current characteristic tests are carried out by using an isolation technology, and test errors are reduced by reducing generated current branches, so that the accuracy of a measured value is ensured; according to the invention, the testing of the microsystem component level is realized, most of the fault components can be detected before the function performance test, the final function performance test first pass yield is improved, the subsequent potential quality hazard and resource waste are avoided, and the test coverage rate of the network is effectively improved.

Owner:珠海天成先进半导体科技有限公司