Patents

Literature

1305 results about "Glass chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

High-stability optical fiber Fabry-Perot pressure sensor packaged without glue and manufacturing method

ActiveCN102384809AEliminate the effects ofEasy to achieve airtightFluid pressure measurement by electric/magnetic elementsOptical light guidesEngineeringCo2 laser

The invention provides a high-stability optical fiber Fabry-Perot pressure sensor packaged without glue and a manufacturing method. The sensor comprises a sensor head, a sensor body with a through-hole in middle, and an optical fiber, wherein a four-layer structure (comprising a first monocrystalline silicon piece, a first Pyrex sheet glass, a second monocrystalline silicon piece and a second Pyrex sheet glass) is adopted by the sensor head; a first reflecting surface of a Fabry-Perot cavity is formed by the back surface of the first monocrystalline silicon piece; the second monocrystalline silicon piece is used for providing a second reflecting surface of the Fabry-Perot cavity; the second Pyrex sheet glass is in butt fusion with the sensor body; and the optical fiber is fixedly arrangedin the sensor body by adopting a CO2 laser, and thereby non-glue packaging is realized. When the first layer of monocrystalline silicon piece is deformed by external pressure changes, the length of the optical fiber Fabry-Perot cavity is changed; and after a broadband light source is accessed to the sensor, the change of the cavity length can be extracted through collecting a reflection spectrum of the sensor or extracting low-coherence interference fringes of the sensor, and thereby pressure information is obtained. By adopting the structure, the influences of environmental changes such as the temperature, the humidity, and the like can be effectively eliminated, and the measurement accuracy can be greatly improved.

Owner:TIANJIN UNIV

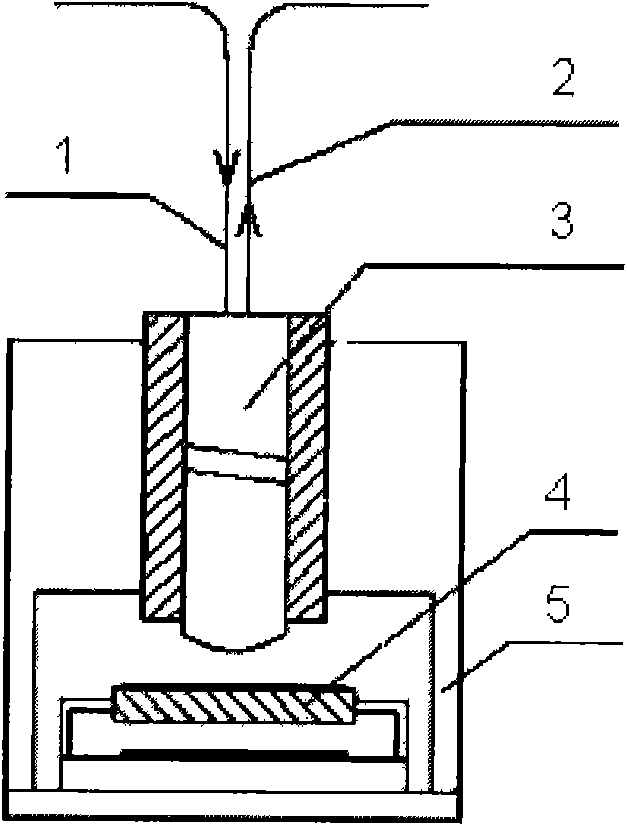

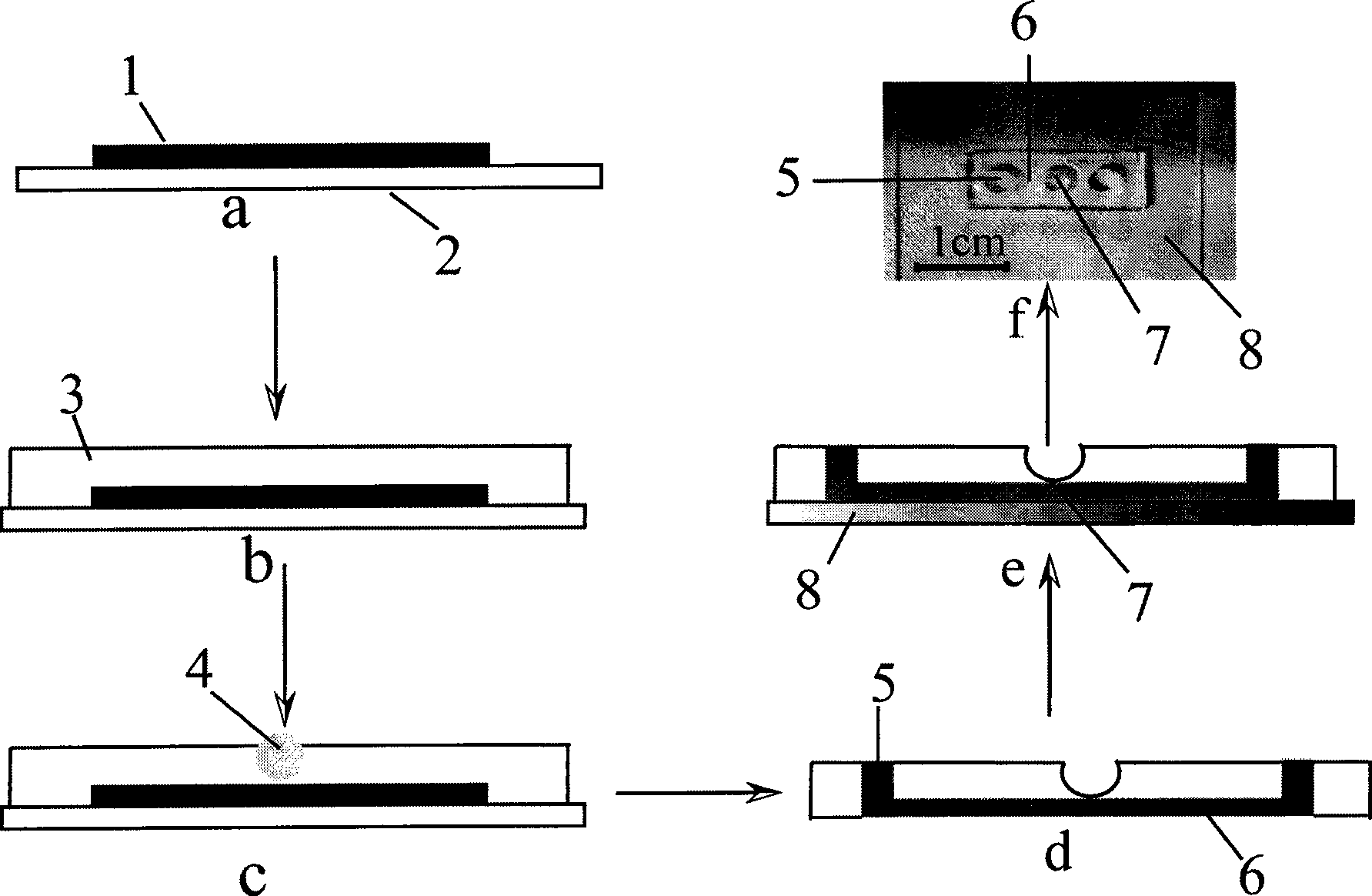

A kind of preparation method of mems atomic vapor chamber and atomic vapor chamber

ActiveCN102259825AEasy to makeIncrease contrastPrecision positioning equipmentDecorative surface effectsWater vaporRubidium

The invention relates to a preparation method for a micro-electro-mechanical system (MEMS) atomic vapor chamber and the atomic vapor chamber. The chamber is prepared by bonding a Pyrex glass sheet, a silicon wafer and a Pyrex glass sheet by an anodic bonding technology; the Pyrex glass sheet is taken as a window of the chamber; a chamber space is formed by etching or corroding the silicon wafer; paraffin packaged alkali metal such as rubidium (Rb) or cesium (Cs) is put into the chamber, and buffer gas with appropriate pressure is introduced simultaneously; paraffin is taken as a packaging material of the alkali metal, so that active alkali metal is isolated from oxidants such as oxygen, water vapor and the like in an environment; the paraffin is also used as a plating material of the chamber, so that collision between Rb or Cs atoms and a chamber wall is slowed down; and a CO2 laser is used for melting the paraffin to release the alkali metal, so that a uniform paraffin plating is formed on the chamber wall. The problem of long-term drift caused by reaction residues generated by a field preparation mode is solved, the collision between the Rb or Cs atoms and the chamber wall is slowed down, and the contrast of atomic resonance line width of the alkali metal is improved.

Owner:江苏智能微系统工业技术股份有限公司

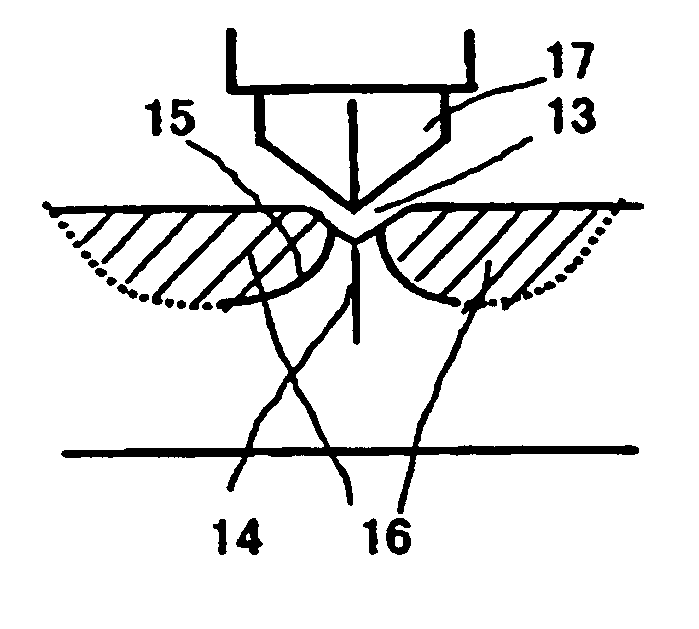

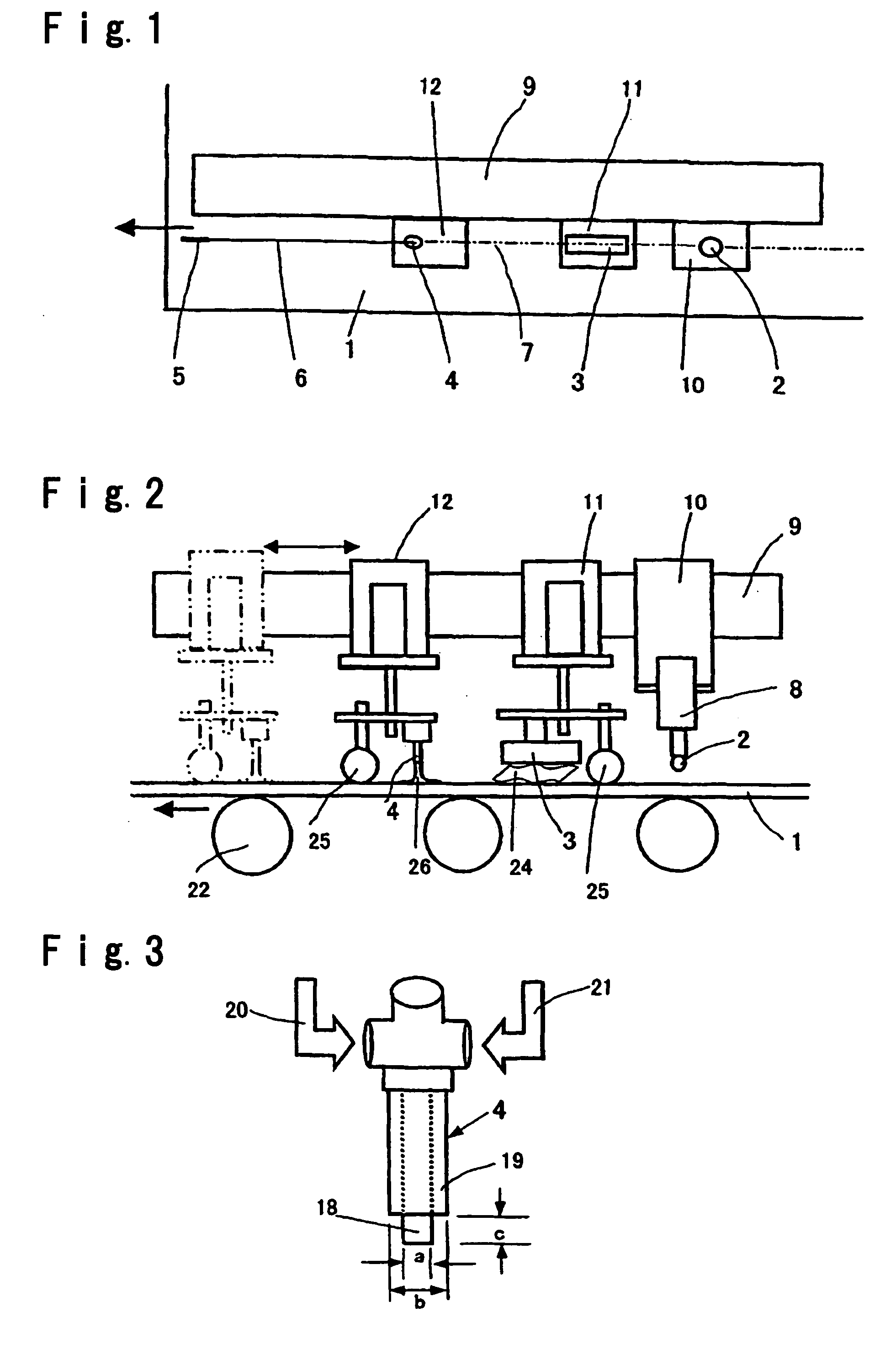

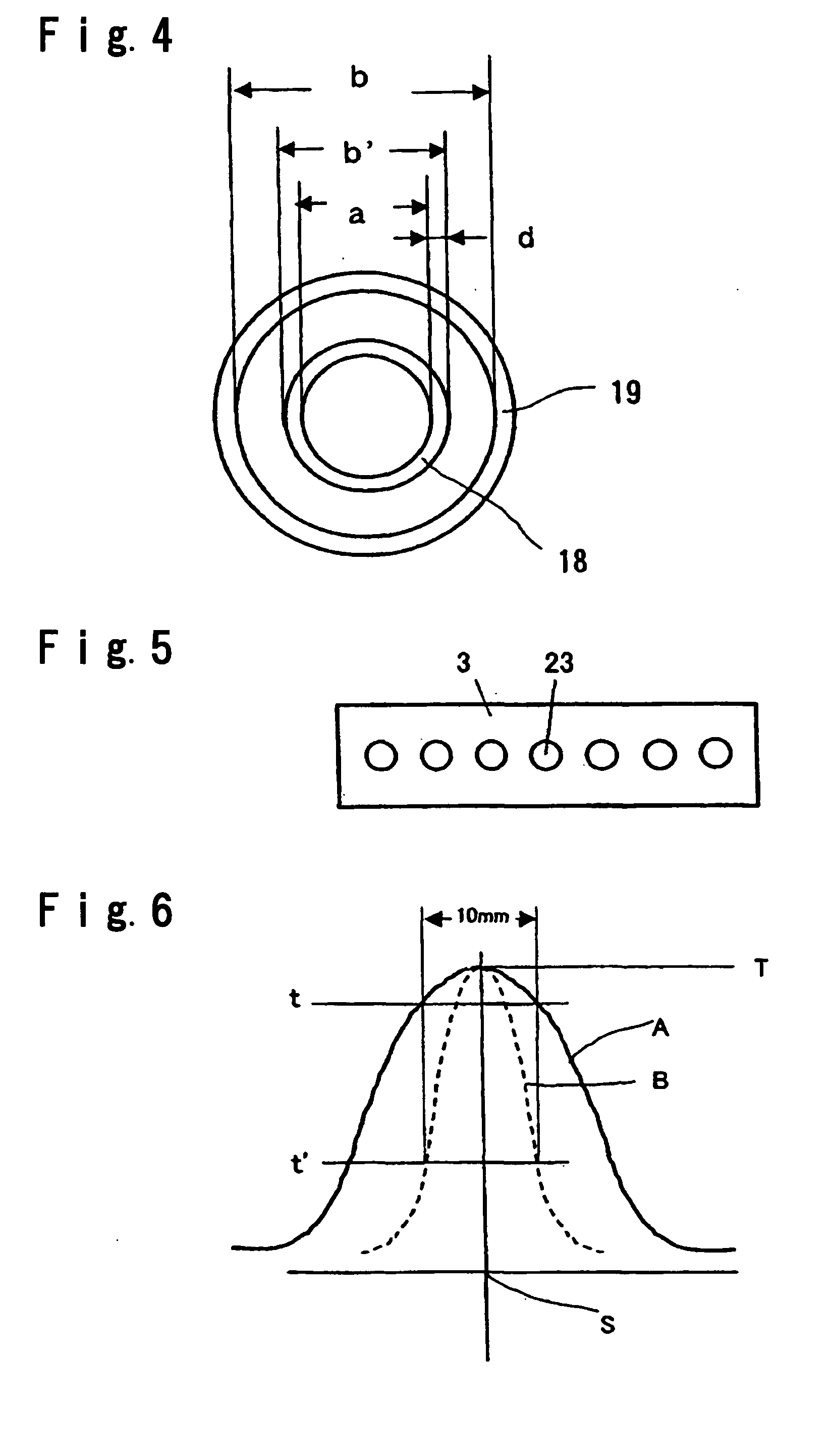

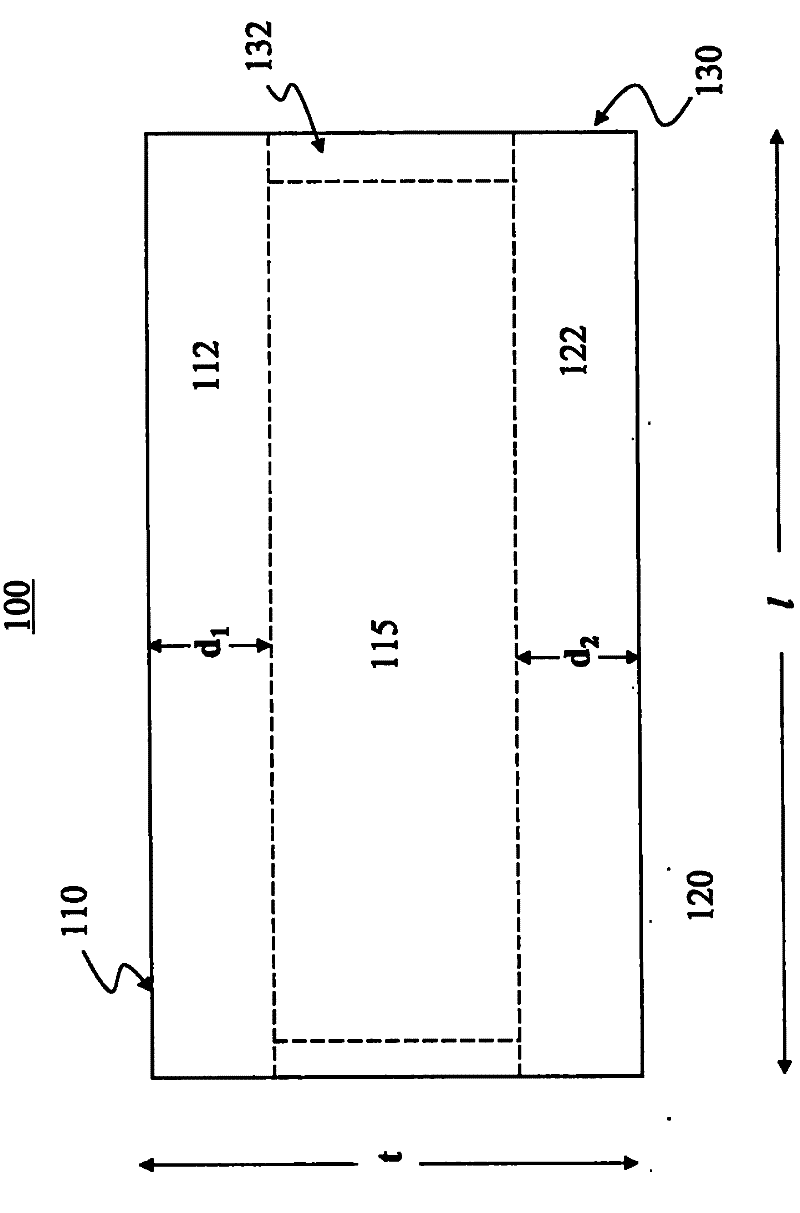

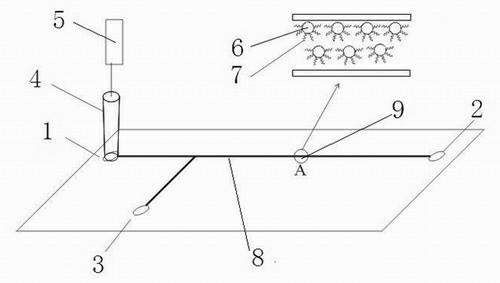

Method and apparatus for separating sheet glass

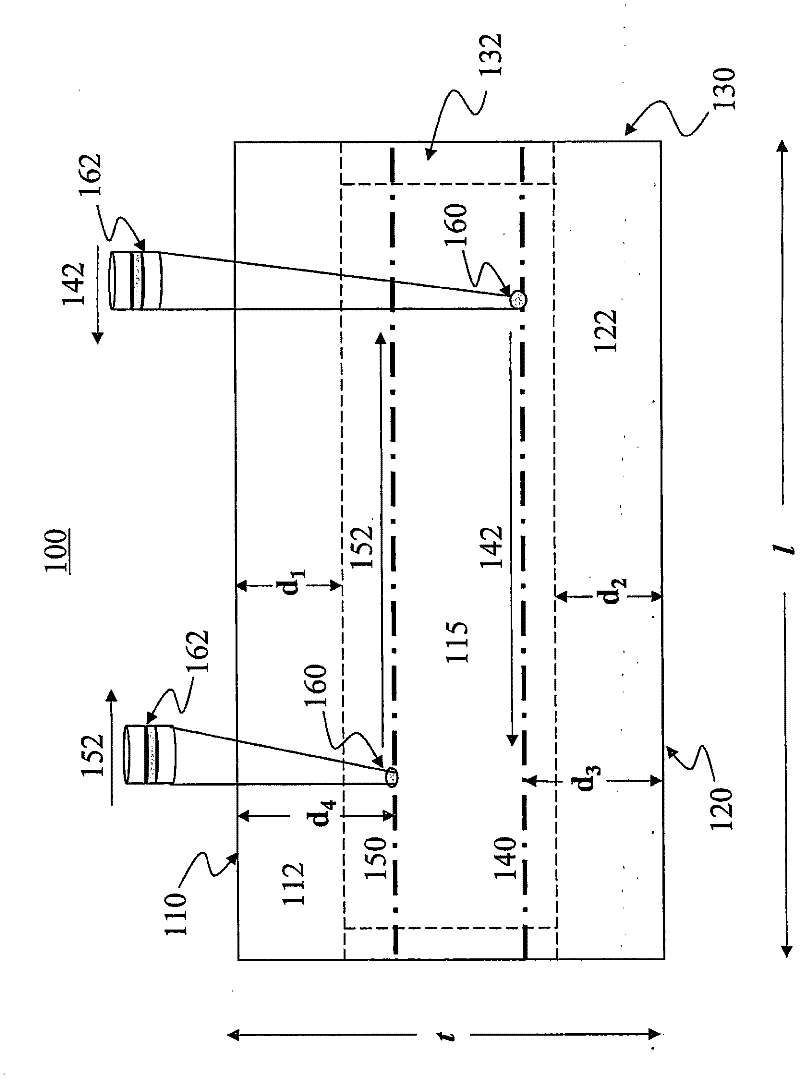

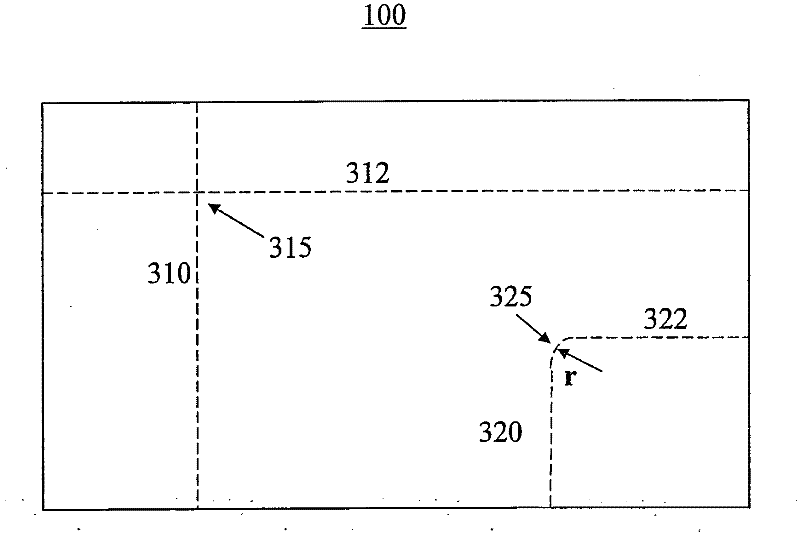

InactiveUS20060191970A1Heating evenlyQuality improvementWood compressionGlass severing apparatusFlat glassInitiation point

In separation of sheet glass by making use of thermal strain, separated surfaces can be obtained to avoid the occurrence of glass chips and to have excellent linearity even in relatively thick sheet glass. After a score, which serves as a crack initiation point is engraved at a separation initiation point in sheet glass, the sheet glass is heated along an imaginary line of by a heating burner; the heated portion of the sheet glass with the imaginary line of separation set therein is locally cooled by a mist, which is produced by a cooling nozzle comprising a liquid-ejecting port disposed at a central portion thereof and a gas-ejecting port disposed around an outer periphery of the liquid-ejecting port, the liquid-ejecting port projecting farther than the gas-ejecting port; and a minute crack of the score is caused to propagate along the imaginary line of separation to form a crack required for separation of the sheet glass.

Owner:ASAHI GLASS CO LTD

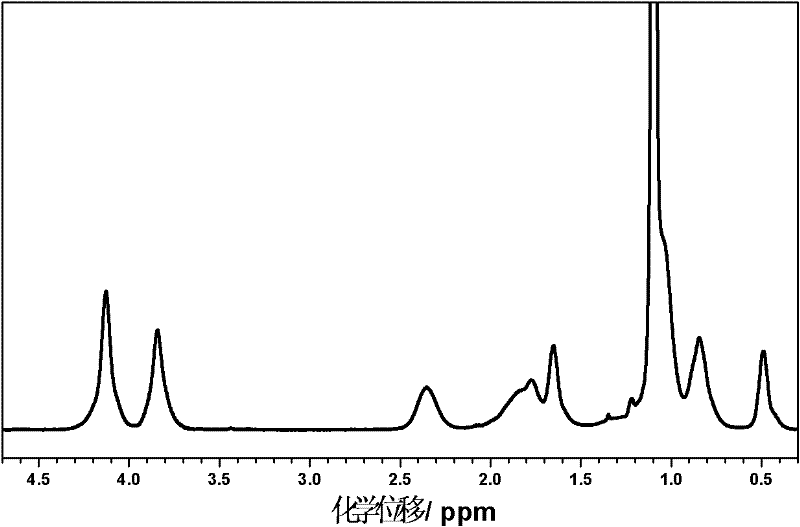

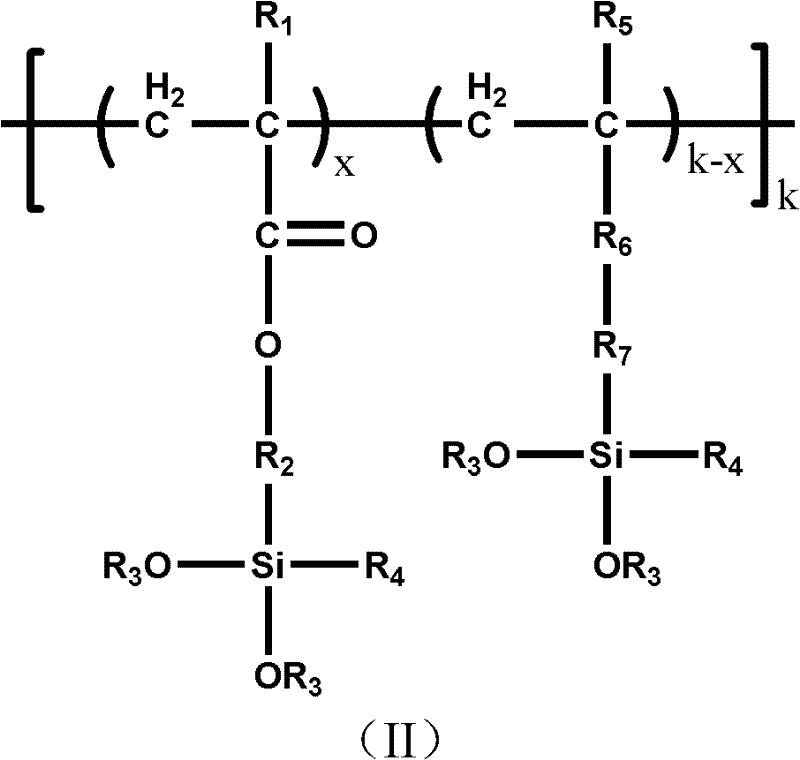

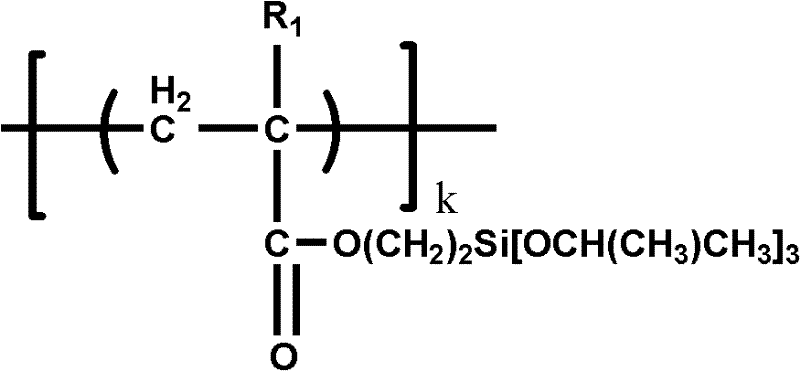

Amphiphobic fluoro-containing crosslinkable block copolymer and preparation method and application thereof

InactiveCN102199263AGood superhydrophobic and oleophobic propertiesPrecise structurePaper coatingCoatingsNano siliconPolymer science

The invention discloses amphiphobic fluoro-containing crosslinkable block copolymer and a preparation method and application thereof. The block copolymer can be used for preparing a super-amphiphobic coating on the surface of glass or printing paper, and the super-amphiphobic coating is prepared by the following steps of: (1) putting silica nano spheres into benzotrifluoride to obtain solution ofsilica nano spheres; (2) adding solution of amphiphobic fluoro-containing crosslinkable block copolymer, tetrahydrofuran, hydochloric acid solution and water into the solution of silica nano spheres,and reacting for 7 to 12 hours to obtain a crude product of modified silica nano spheres; (3) washing the crude product of modified silica nano spheres to obtain modified silica nano spheres; and (4)dispersing the modified silica nano spheres into the benzotrifluoride to obtain solution, dripping the solution onto a glass sheet, and after the solvent is volatilized, forming the super-amphiphobiccoating on the surface of the glass sheet, or soaking the printing paper in the solution, taking the paper out, and drying the paper to obtain the super-amphiphobic coating on the surface of the paper. The amphiphobic fluoro-containing crosslinkable block copolymer can endow a material with good superhydrophobic and oleophobic properties; and the coating has high stability and hardly falls off and denatures.

Owner:GUANGZHOU CHEM CO LTD CHINESE ACADEMY OF SCI

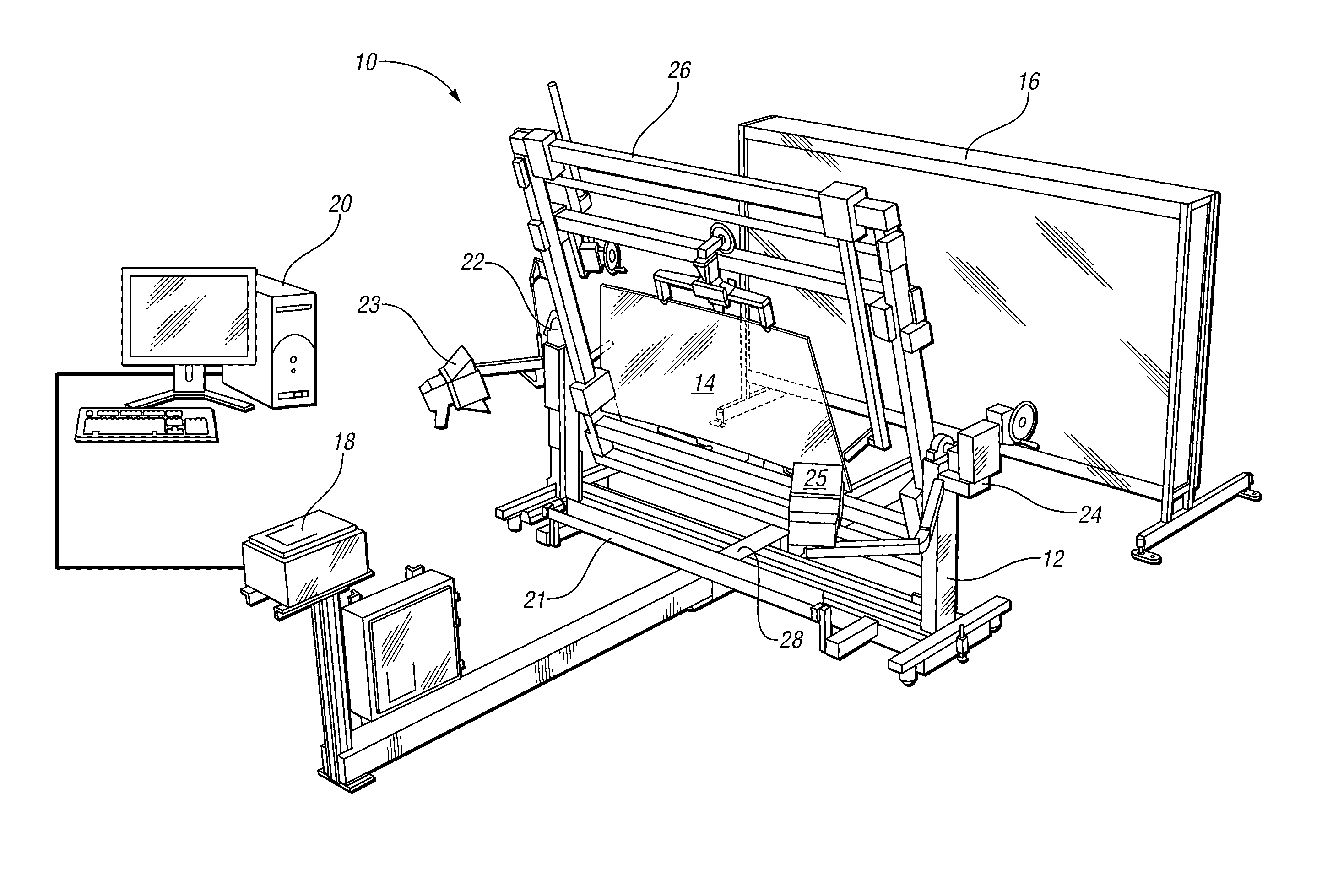

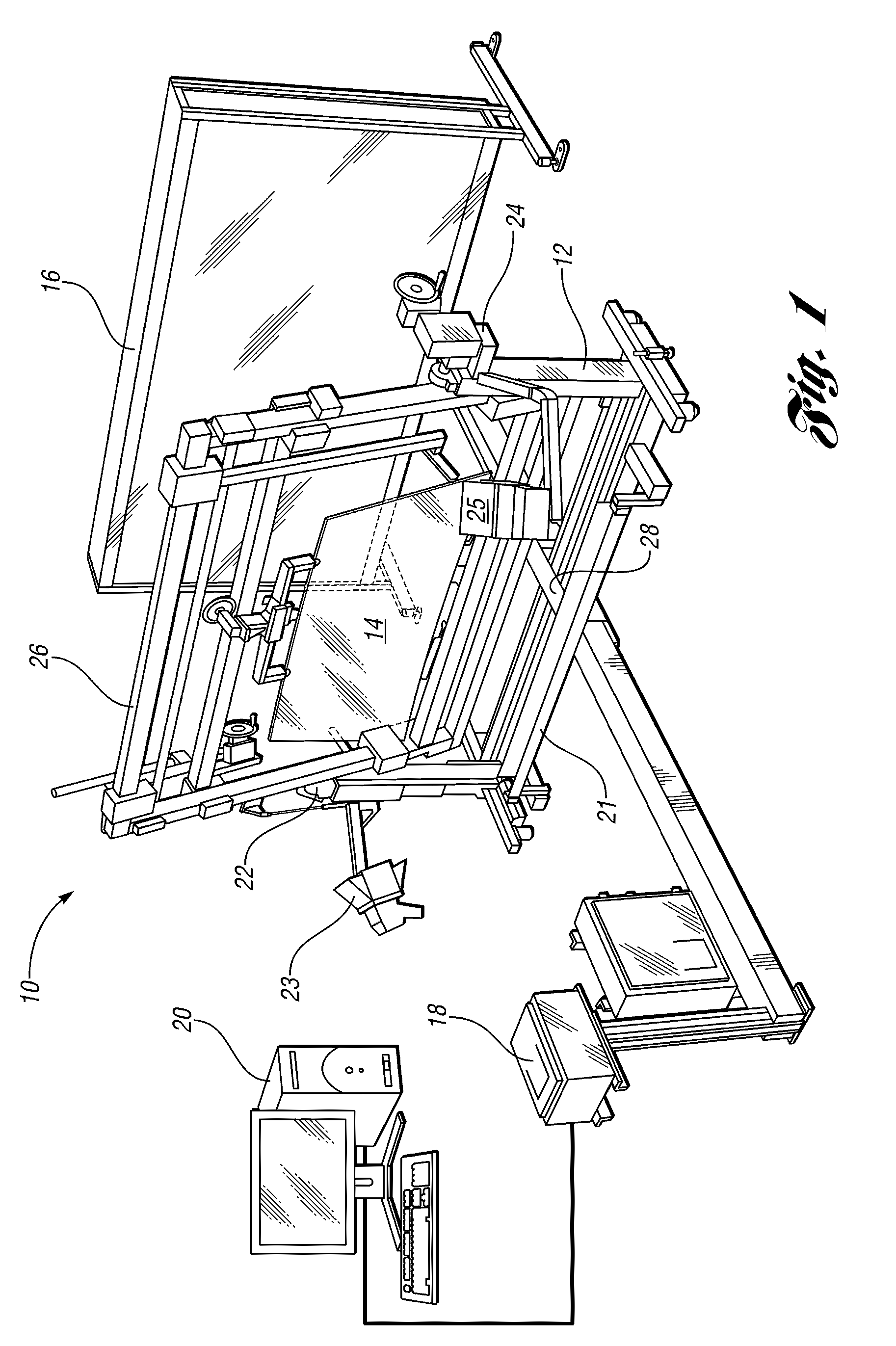

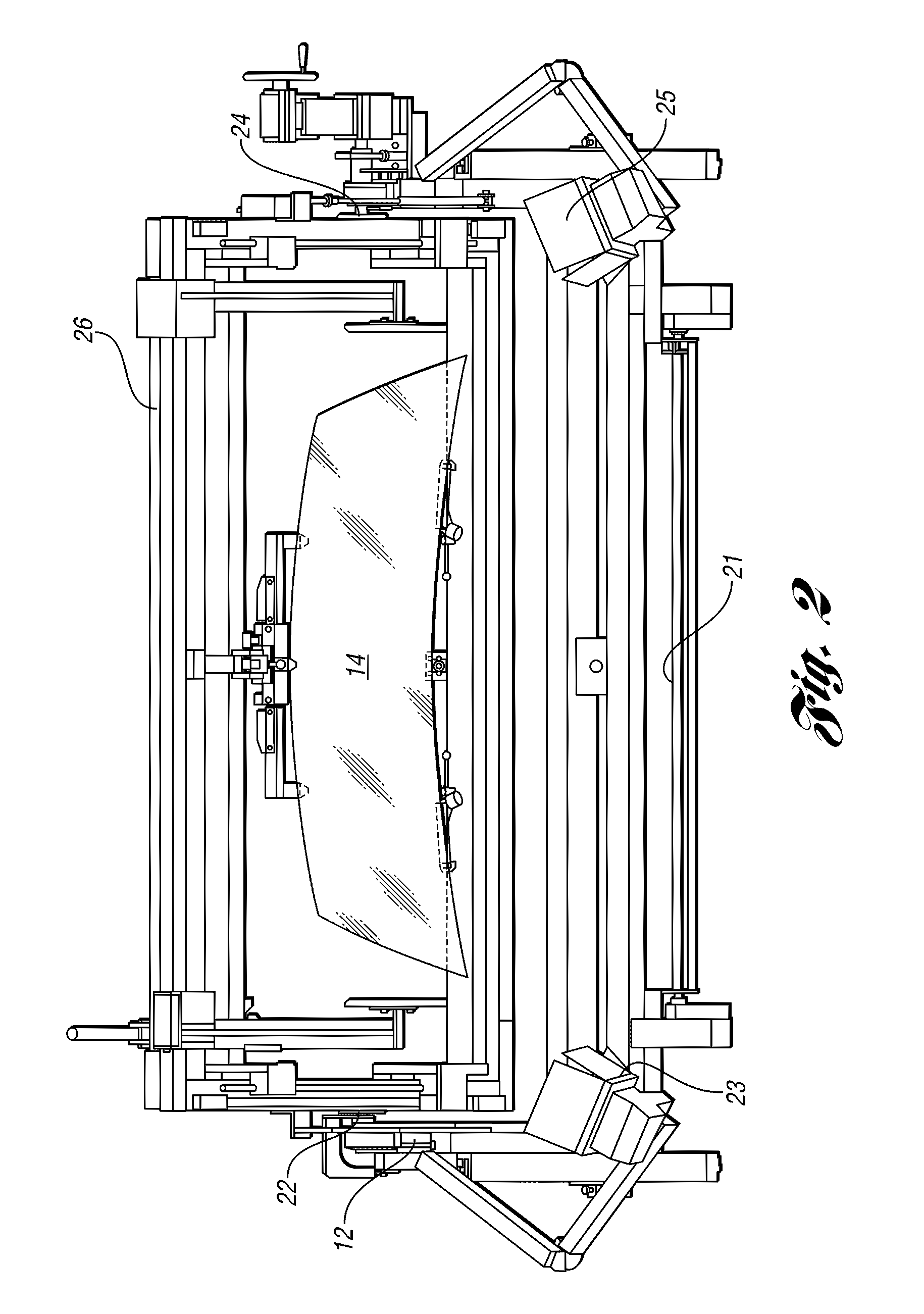

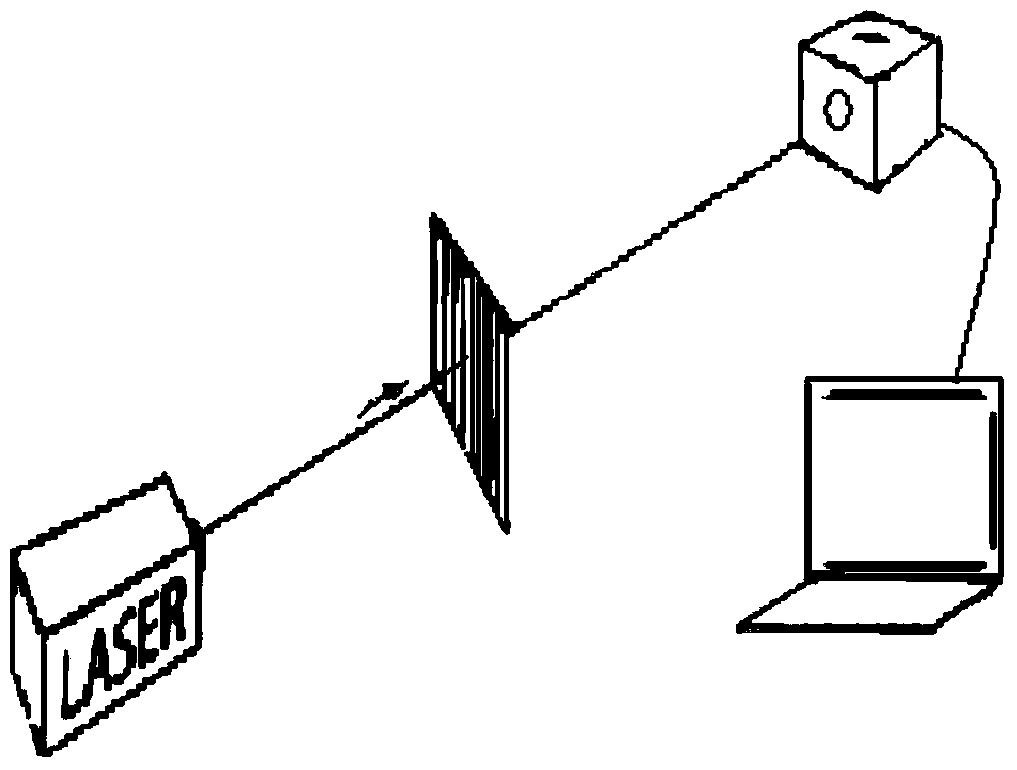

Method and apparatus for measuring transmitted optical distortion in glass sheets

ActiveUS20090282871A1Blowing machine gearingsMaterial analysis by optical meansSurface markerDot matrix

An apparatus and associated method for measuring transmitted optical distortion in a glass sheet includes a glass stand which receives a glass sheet for mounting between a background screen which includes a matrix of spaced apart dots, and a digital camera which captures (1) an image of the glass sheet surface, and (2) an image of the dot matrix transmitted through the glass sheet. The captured images are downloaded to a computer that is suitably programmed to analyze the image data to (1) determine the presence of any markings or elements on the surface of the glass sheet that should be isolated from the dot matrix image, (2) modify the background image to eliminate the image data corresponding to any such surface markings or elements from the image, and (3) determine characteristics indicative of optical distortion in the modified image of the dot matrix background transmitted through the glass sheet.

Owner:GLASSTECH

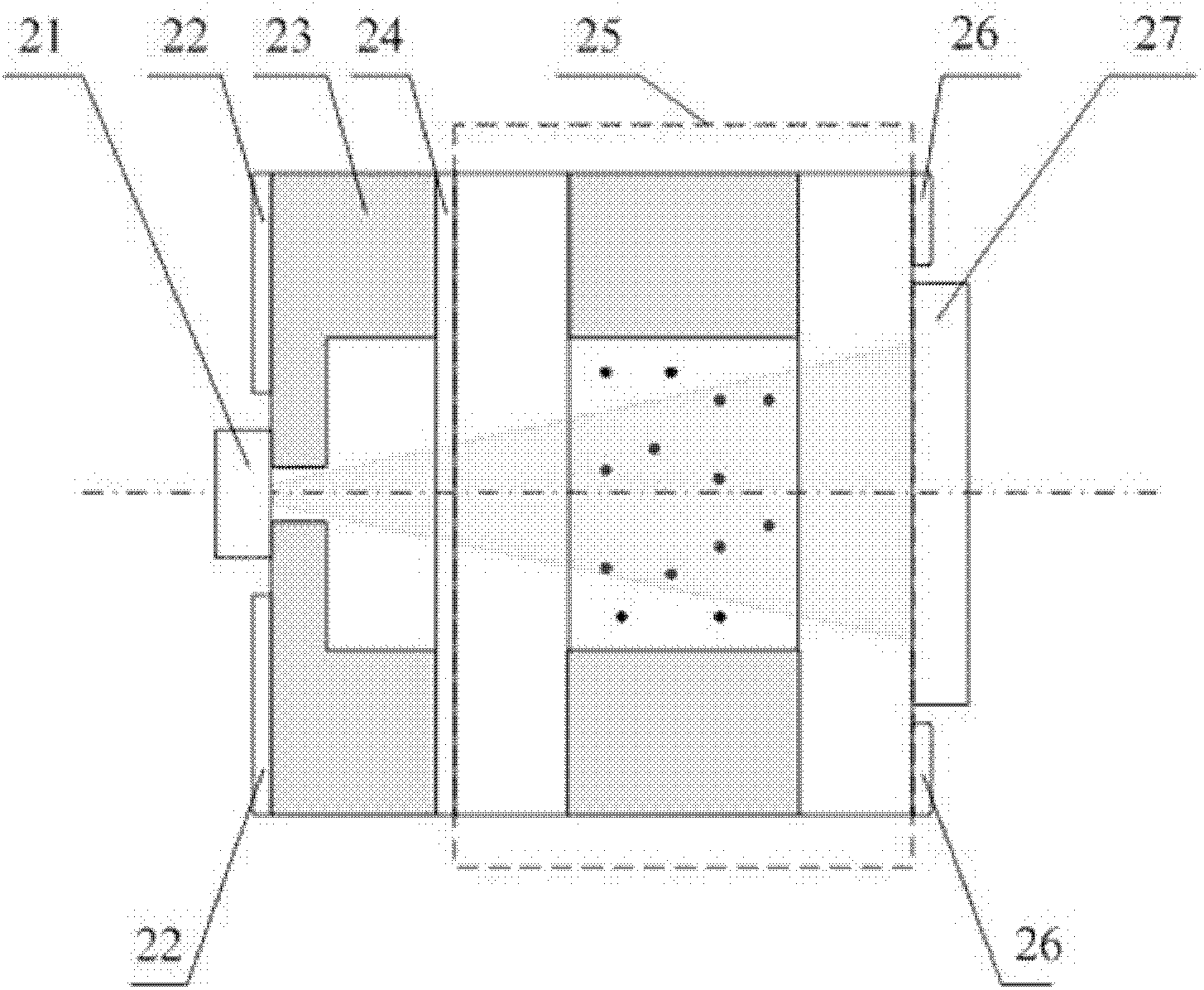

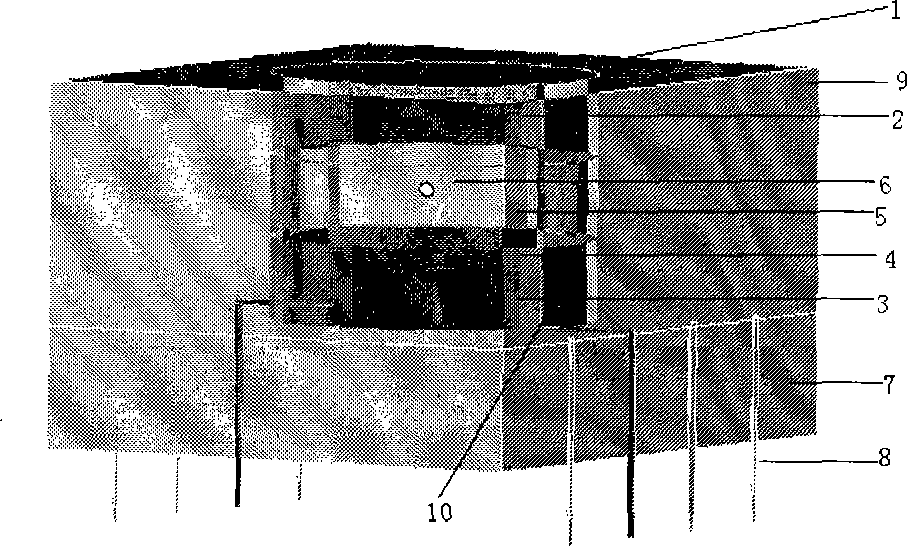

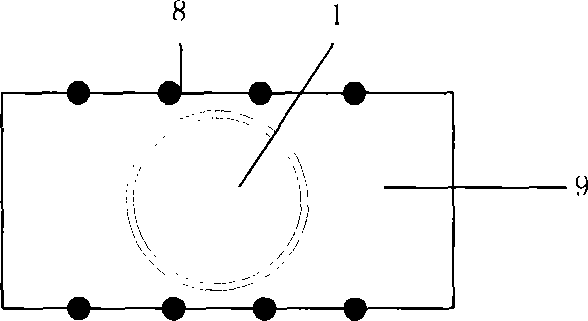

Groove type atomic gas cavity and atomic clock physical system formed by same

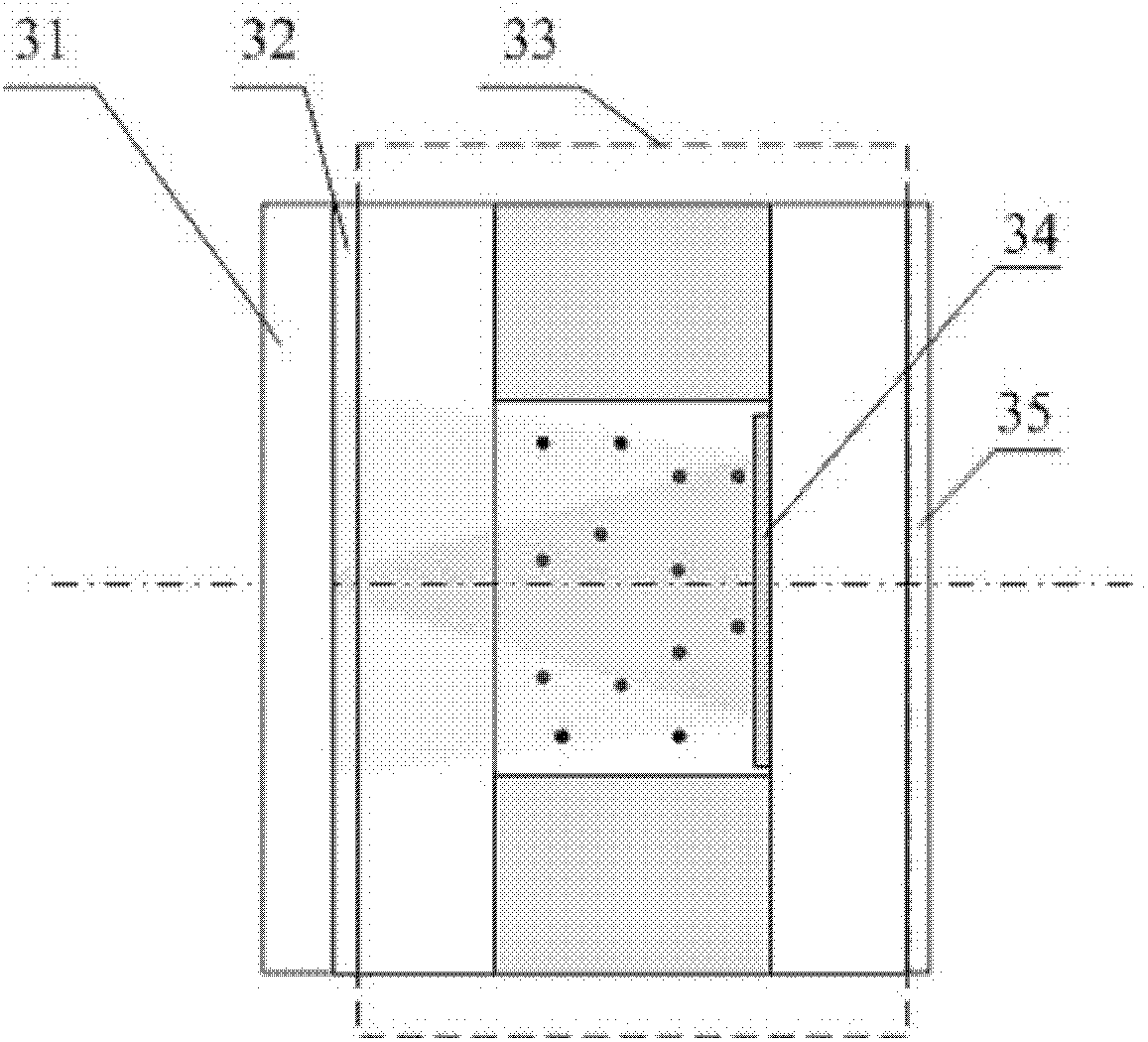

ActiveCN102323738ALower working temperatureUnlimited thicknessApparatus using atomic clocksCrystal planeParticle physics

The invention relates to a groove type atomic gas cavity produced by applying MEMS technology and an atomic clock physical system formed by the same. The cavity is characterized in that the cavity is formed in such a manner that a silicon wafer with a groove and Pyrex glass sheets define a cavity structure through bonding; the cavity structure is used for alkali metal atom vapor and buffer gases to fill in; the cross section of the groove is in a shape of inverted trapezoid; and the groove comprises a bottom surface and side walls forming included angles with the bottom surface. The cavity is manufactured based on MEMS (micro-electro-mechanical system) technology. The silicon groove is formed through anisotropic etching of the (100) monocrystalline wafer. The groove type cavity is manufactured through silicon-glass anode bonding. The side walls of the cavity are {111} crystal planes of the silicon wafer. The cavity and the system have the following beneficial effects: by utilizing the cavity, the distance between two reflectors in the cavity is easy to enlarge through atomic cavity dimension design, thus increasing the length of the interaction space between laser and atomic gas, enhancing the signal to noise ratio of the CPT (coherent population trapping) signal and being beneficial to improvement of the frequency stability of the micro CPT atomic clock.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Three-dimensional high-flux medicaments sifting chip and manufacture method thereof

InactiveCN101245311ALow costShort cycleBioreactor/fermenter combinationsBiological substance pretreatmentsEngineeringPolydimethyl siloxane

The invention discloses a three-dimensional high-flux drug screening PDMS-glass chip and the preparation method thereof, which makes uses of micro-electro processing and micro-plastic film technologies to produce the three-dimensional PDMS-glass chip with a two-layer micro-channel structure. A cell injection and waste liquid output channel of a first layer of PDMS chip is bonded with another layer of polydimethyl siloxane chip together, a drug concentration gradient channel and a quantitative cell culture chamber are arranged on the other layer of PDMS chip, the quantitative cell culture chamber is connected with an outlet channel of the drug concentration gradient channel, the quantitative cell culture chamber is respectively connected with a cell sample injection hole drilling position and a waste liquid outlet hole drilling position by the channel; the three-dimensional high-throughput drug screening PDMS-glass chip can overcome the shortcomings of heavy workload, great reagent and drug consumption, long screening period and high development cost of the traditional drug screening technology. The three-dimensional high-flux drug screening PDMS-glass chip can realize miniaturization of the chip, high flux, low cost, small reagent consumption, accurate and reliable test data and the simple design requirements of the operational process in the drug screening application on cell level.

Owner:WUHAN UNIV +1

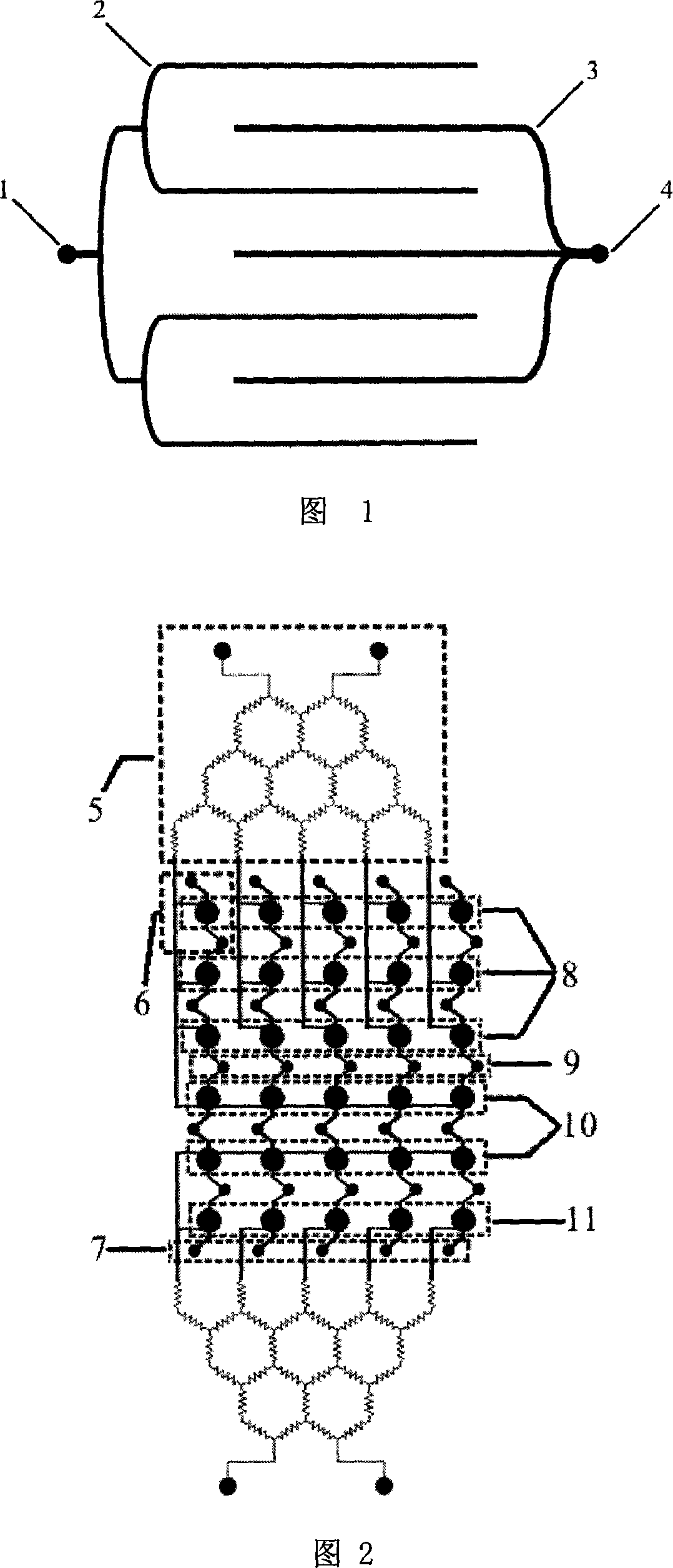

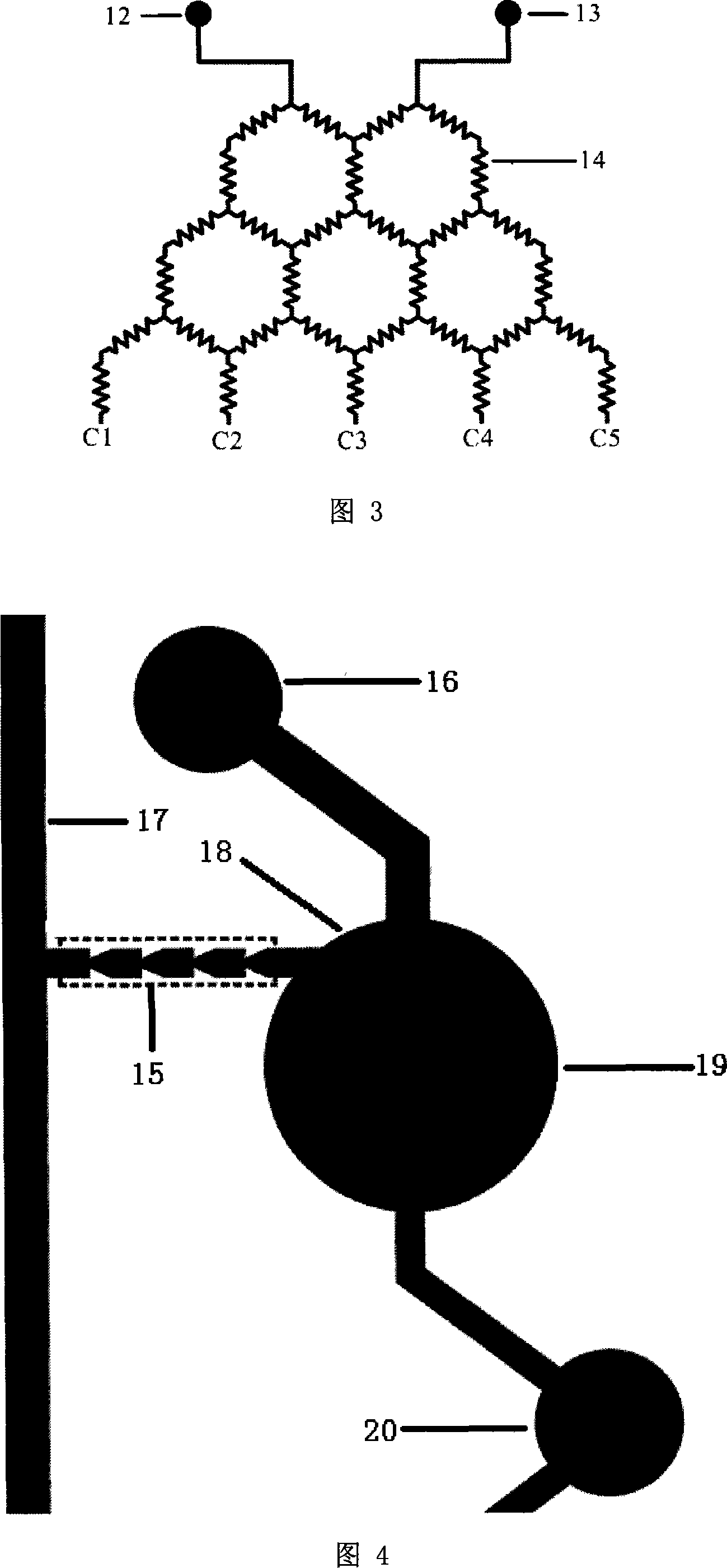

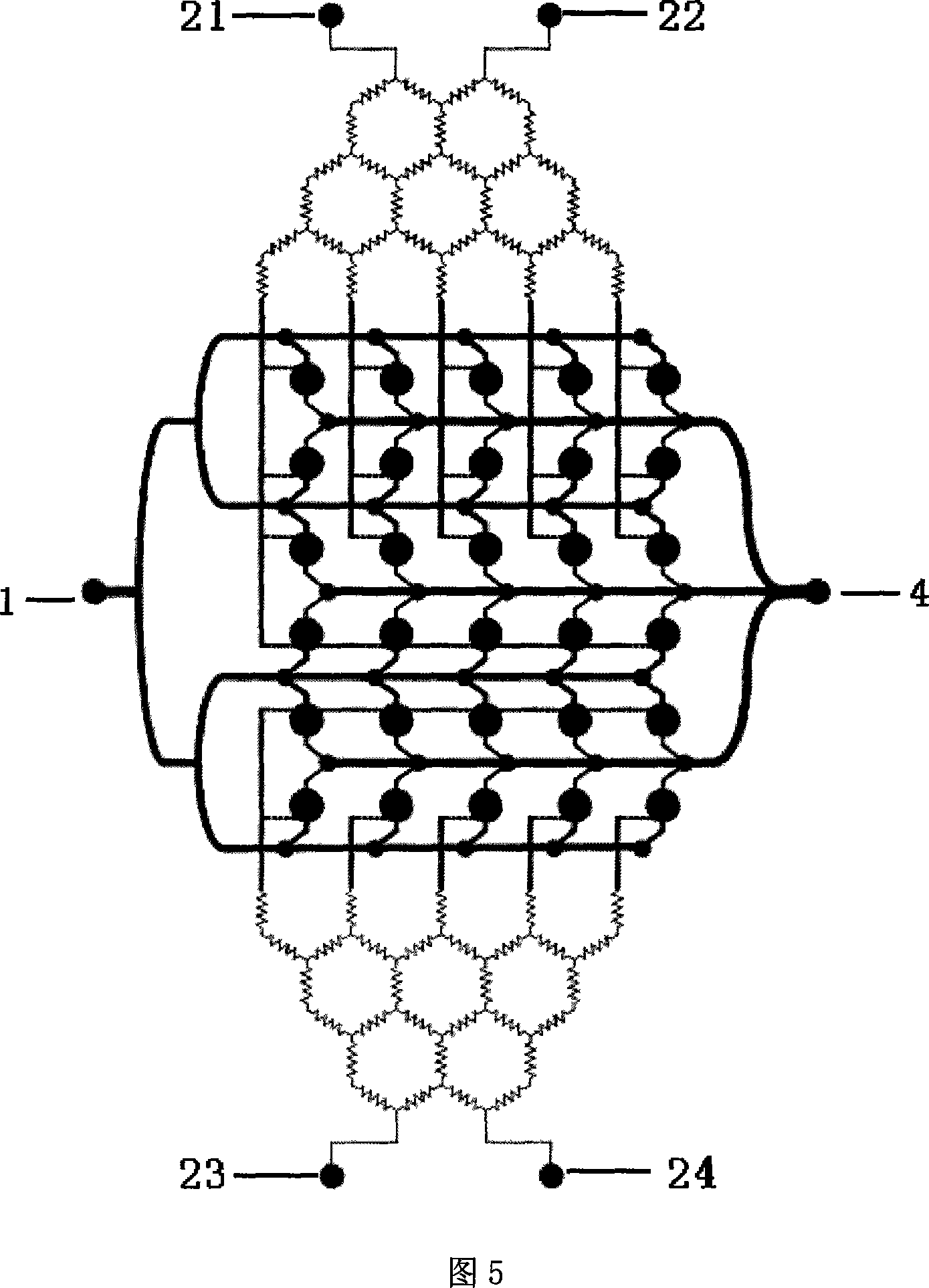

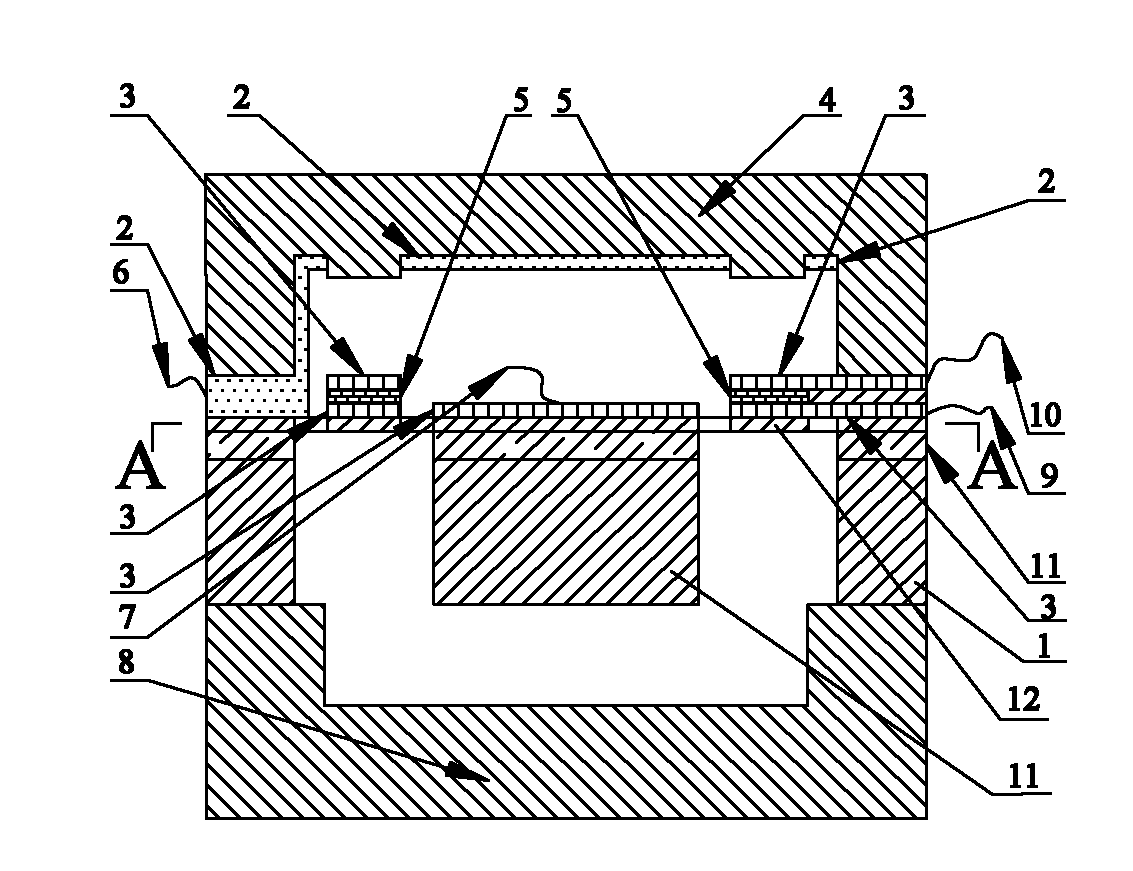

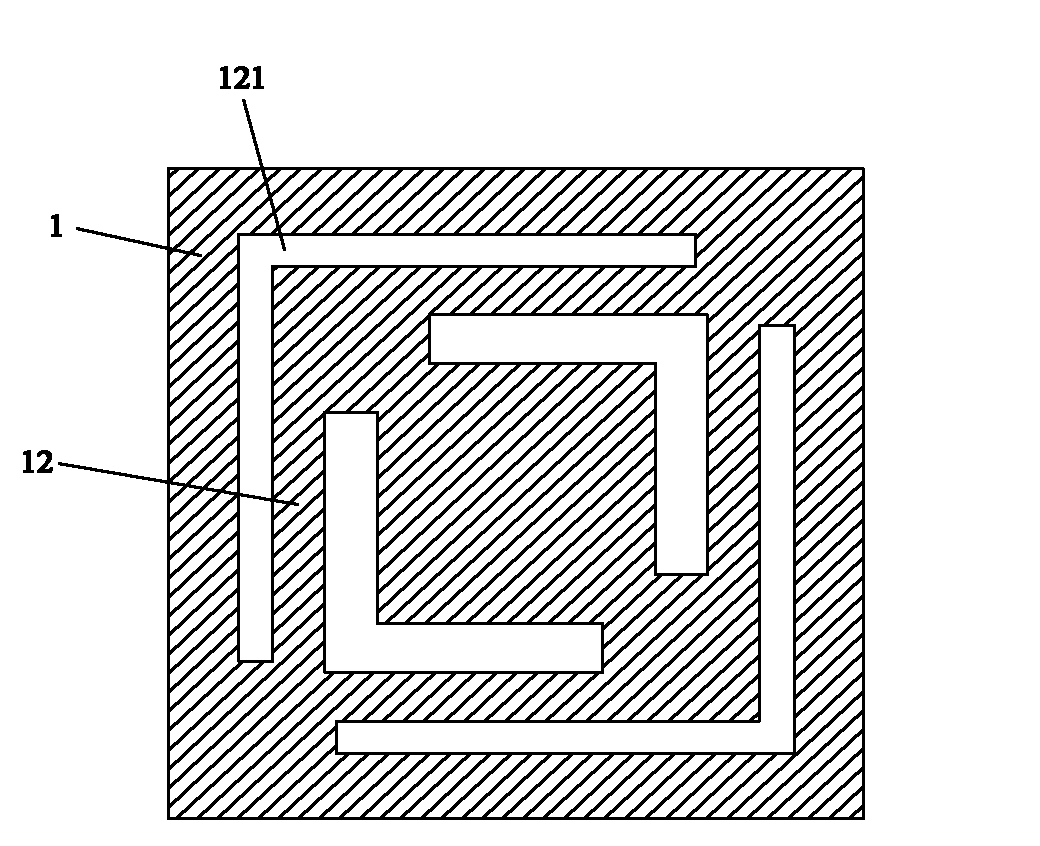

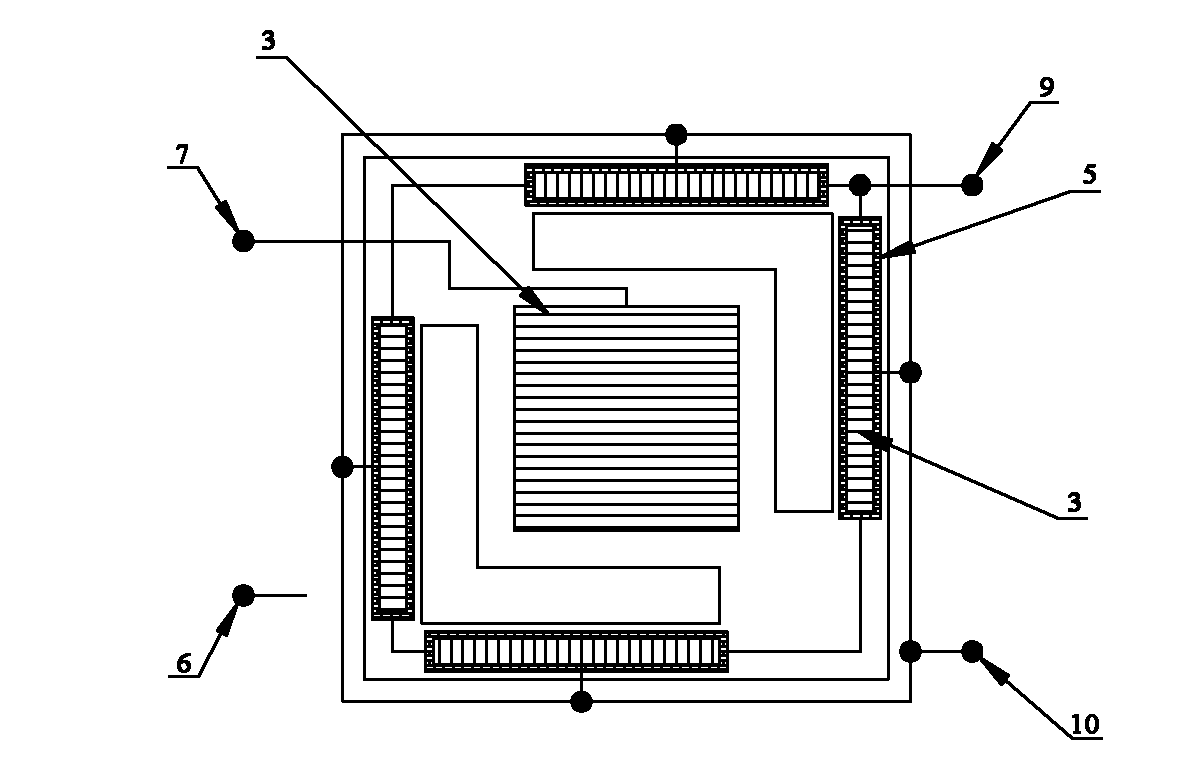

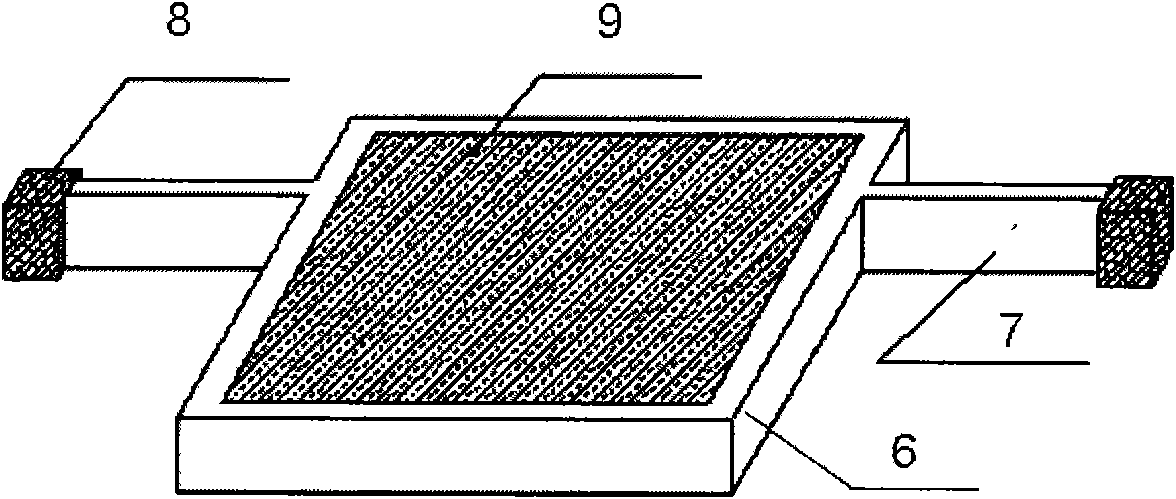

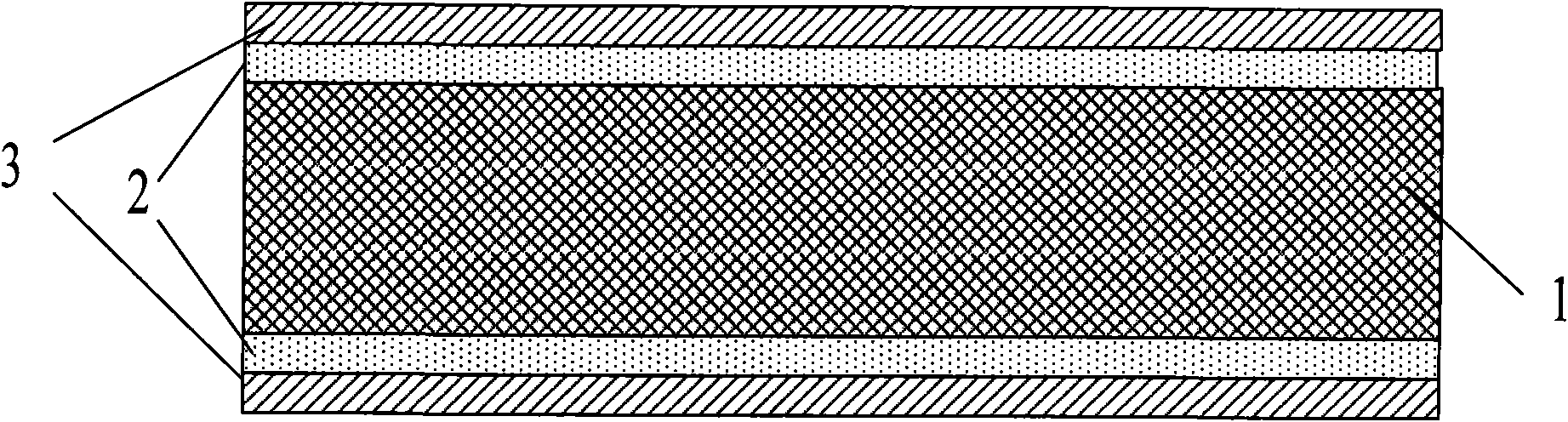

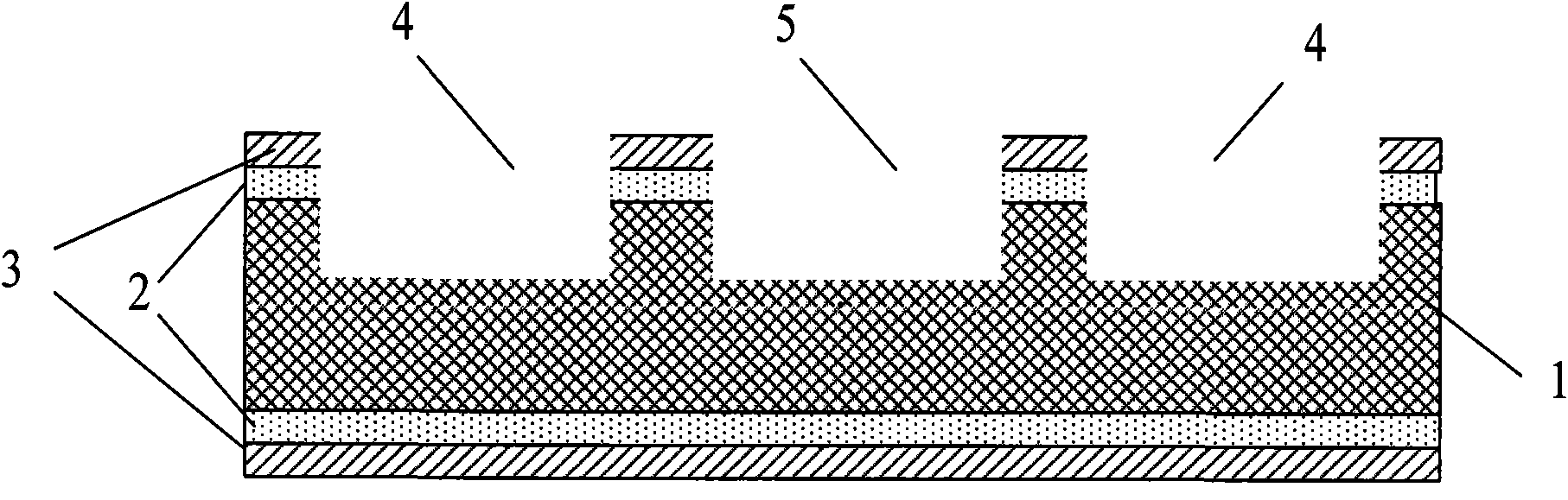

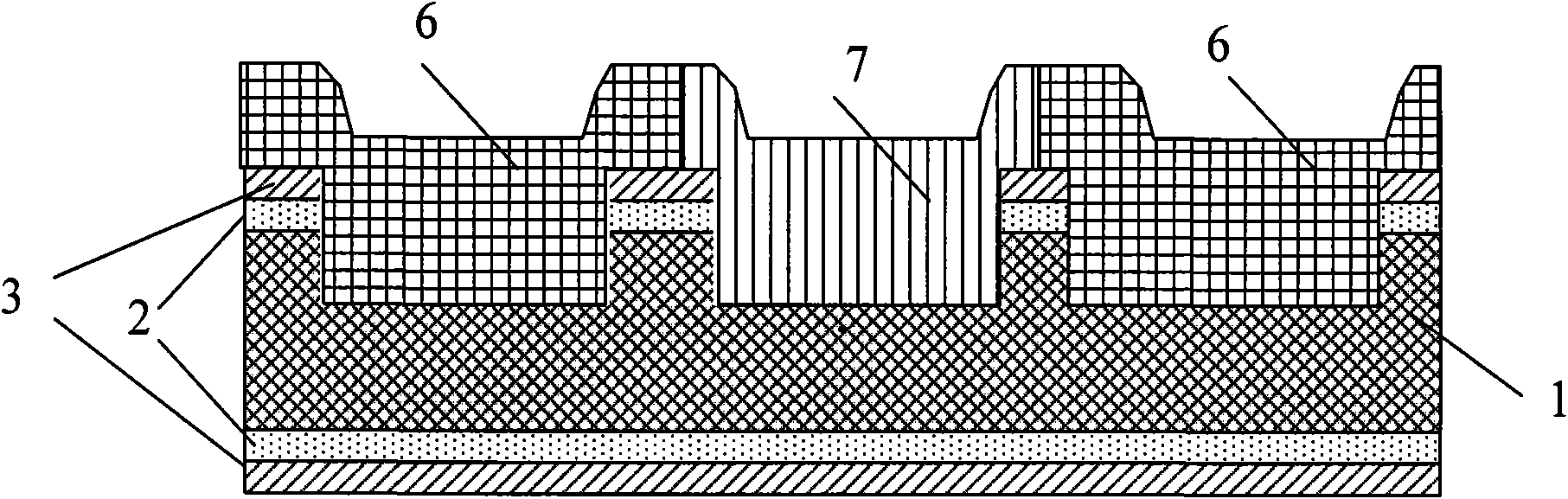

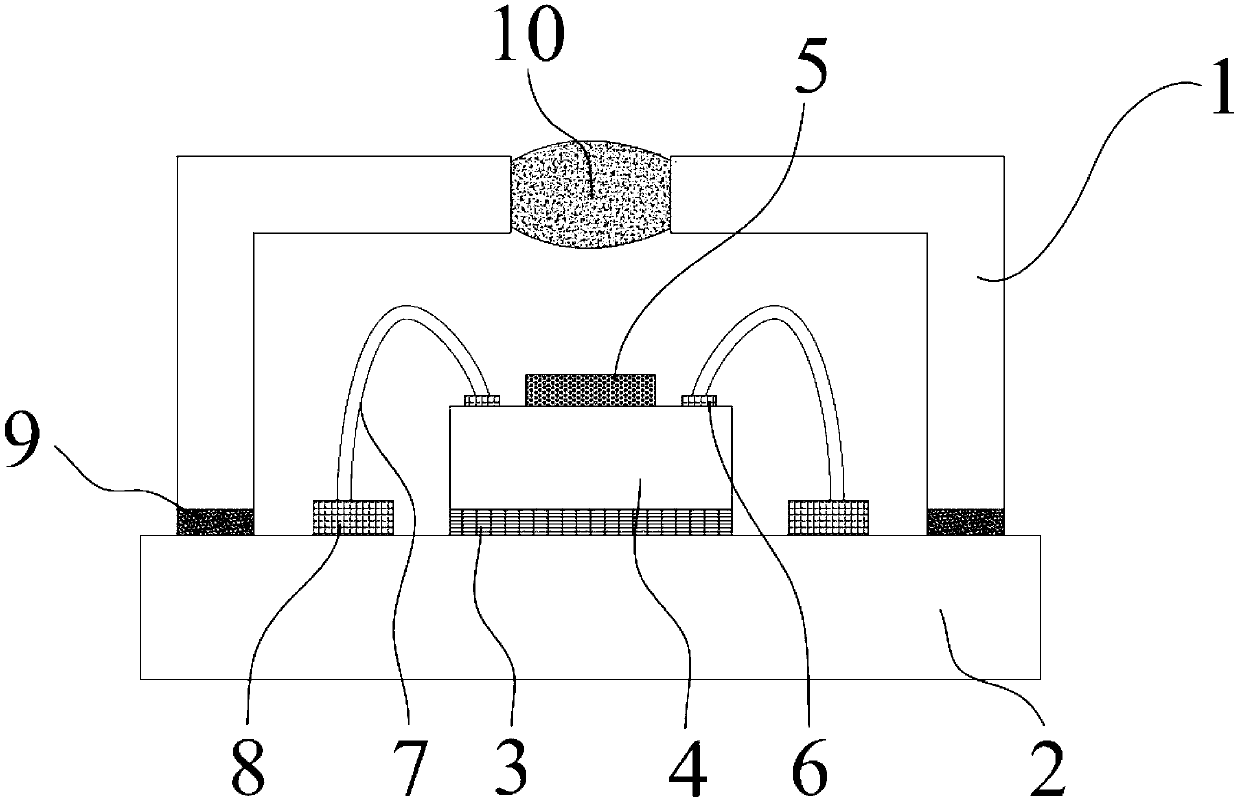

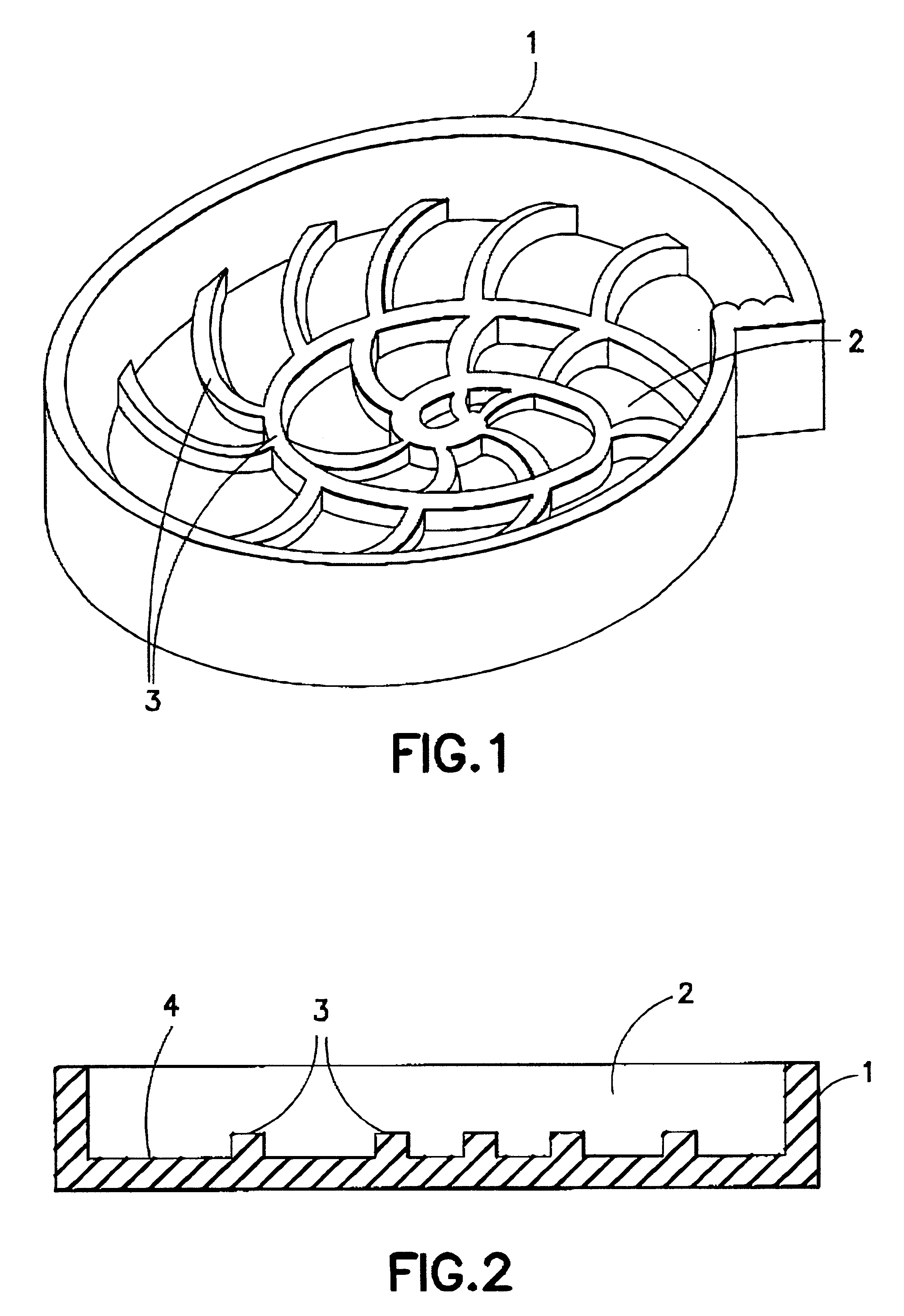

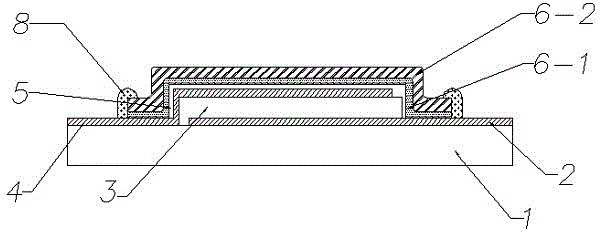

Piezoelectric-static compound micro machine vibration energy collector and manufacture method thereof

InactiveCN102570902AAvoid instabilityAchieve self-supplyPiezoelectric/electrostriction/magnetostriction machinesDecorative surface effectsCapacitanceMachining vibrations

The invention relates to a piezoelectric-static composite micro machine vibration energy collector and a manufacture method of the collector, and relates to an energy collecting device. The piezoelectric-static composite micro machine vibration energy collector comprises a chip main body and a chip external circuit, wherein the chip main body is of a three-layer laminated structure, and the chip main body comprises an upper glass piece device, an SOI (Silicon On Insulator) piece device, a lower glass piece device, a piezoelectric ceramic wafer device, a piezoelectric ceramic wafer electrode and a variable capacitance plate electrode. The chip external circuit is provided with a rectification circuit, a filter capacitor, a first switch, a second switch and an energy storage capacitor, or is provided with a rectification circuit, a filter capacitor, a first switch, a second switch and an energy storage capacitor and a variable capacitance plate starting power supply. The manufacture method comprises the following steps of: manufacturing the lower glass piece device; manufacturing the SOI piece device; manufacturing the upper glass piece device; assembling; and connecting the chip external circuit. According to the collector and the manufacture method, the process is simple, the defects of poorer device stability and performance and the like caused by,manufacturing a PZT (Piezoelectric Transducer) by using the traditional sol gel can be overcome, and wide band and high efficiency collection of energy can be realized.

Owner:XIAMEN UNIV +1

Method of separating strengthened glass

Owner:CORNING INC

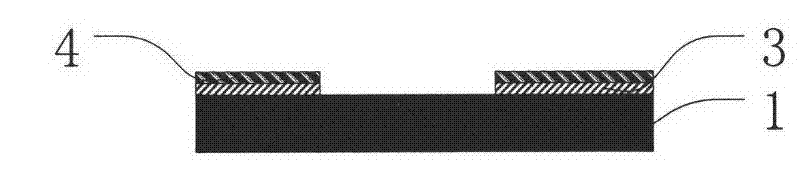

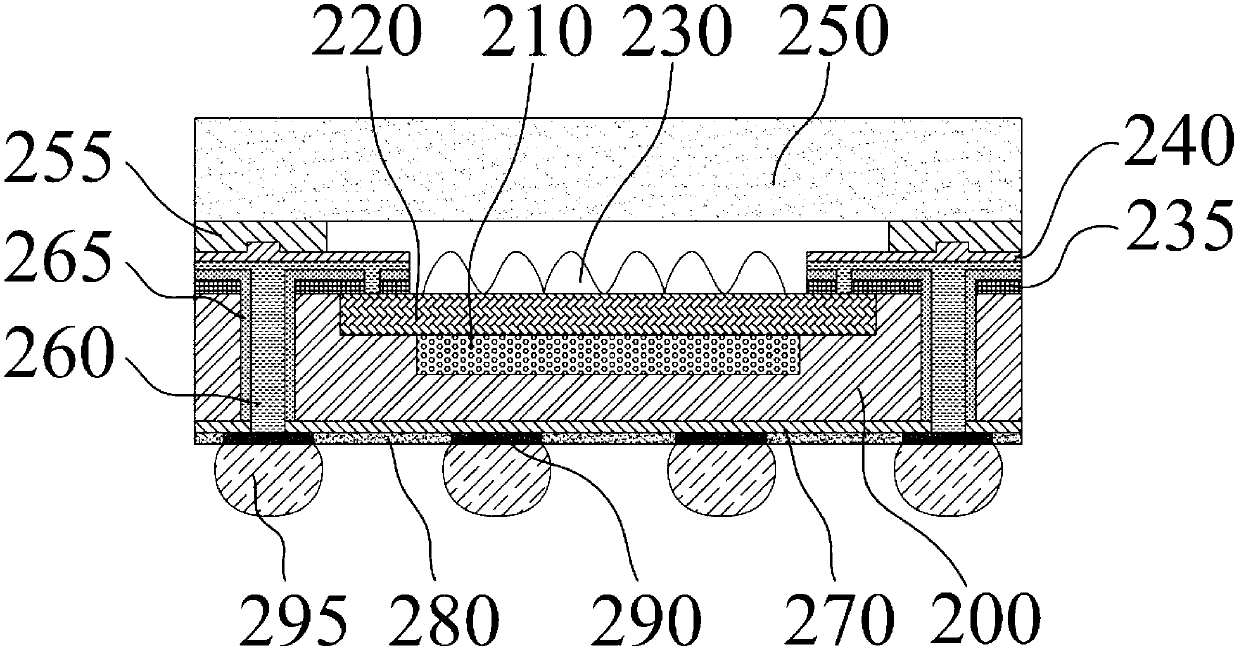

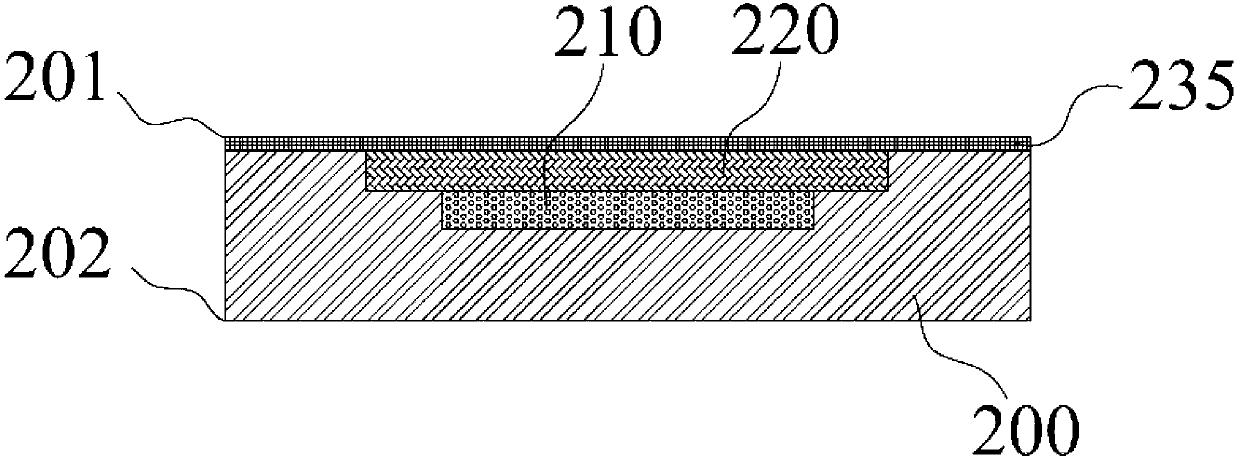

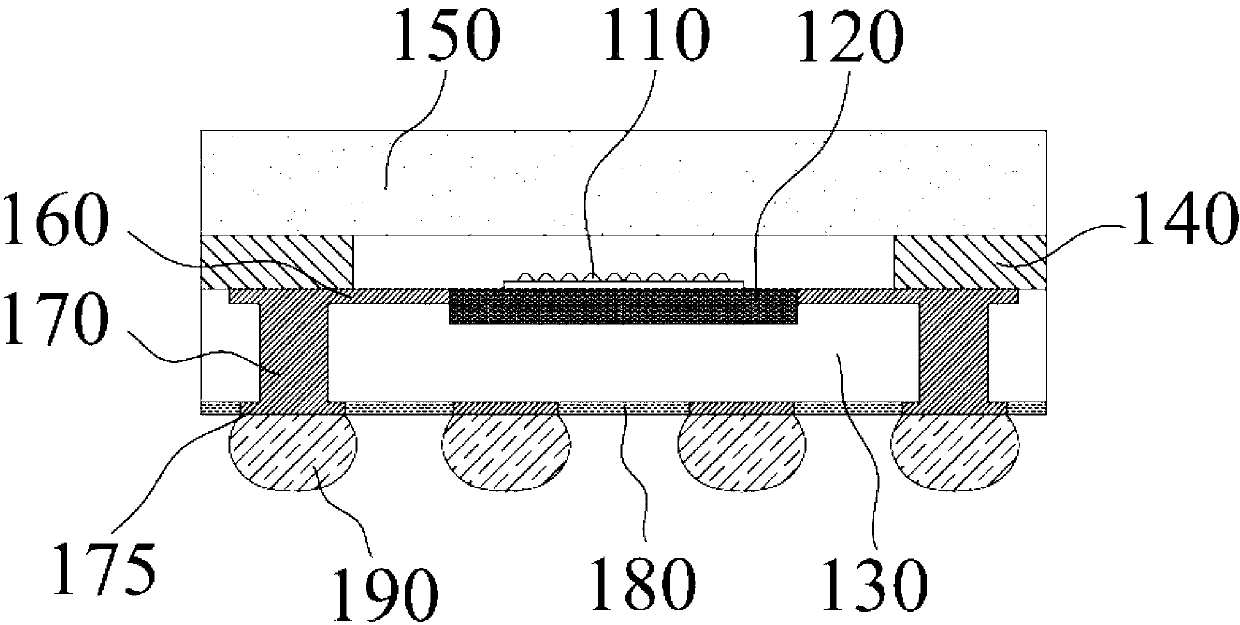

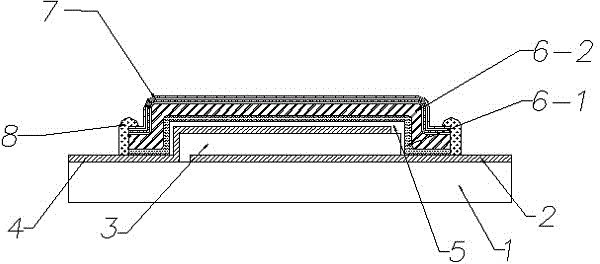

Packaging structure and manufacture method for complementary metal-oxide-semiconductor transistor (CMOS) image sensors

InactiveCN103000649AHigh bonding strengthImprove warpageRadiation controlled devicesMetal interconnectRedistribution layer

The invention discloses a packaging structure and a manufacture method for CMOS image sensors, and belongs to the sensor field. An optical interaction area is placed at a center on a first surface on the front surface of a silicon substrate, a metal interconnection layer is formed on the optical interaction area, a micro lens array is placed on the metal interconnection layer, and a first protection layer is arranged on the outer side of the metal interconnection layer; silicon through holes not penetrating through the silicon substrate and a redistribution layer are manufactured on the first surface, and an input / output (I / N) around the optical interaction area is connected with the silicon through holes through the redistribution layer; passivation layers are manufactured on the silicon through hole walls, and the silicon through holes are filled; a second protection layer is arranged on the redistribution layer; the silicon substrate is bonded with a glass sheet, and a cavity is arranged between the glass sheet and the silicon substrate; the second surface of the silicon substrate is thinned to expose the silicon through holes; a line layer is manufactured on the second surface of the silicon substrate to connect the silicon through holes to pads, and a solder mask layer is manufactured on the line layer and exposes the pads; and solder balls are arranged on the pads. According to the packaging structure and the manufacture method for CMOS image sensors, the layering problem between the glass and the silicon substrate in the packaging structure is solved, the reliability is improved, and the packaging structure is suitable for chips with large sizes.

Owner:BEIJING UNIV OF TECH

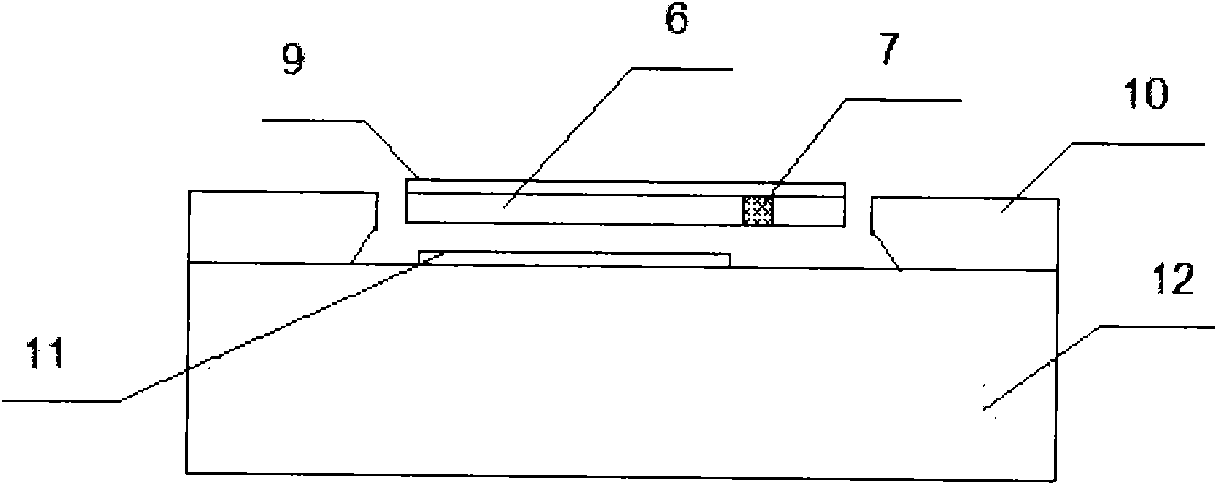

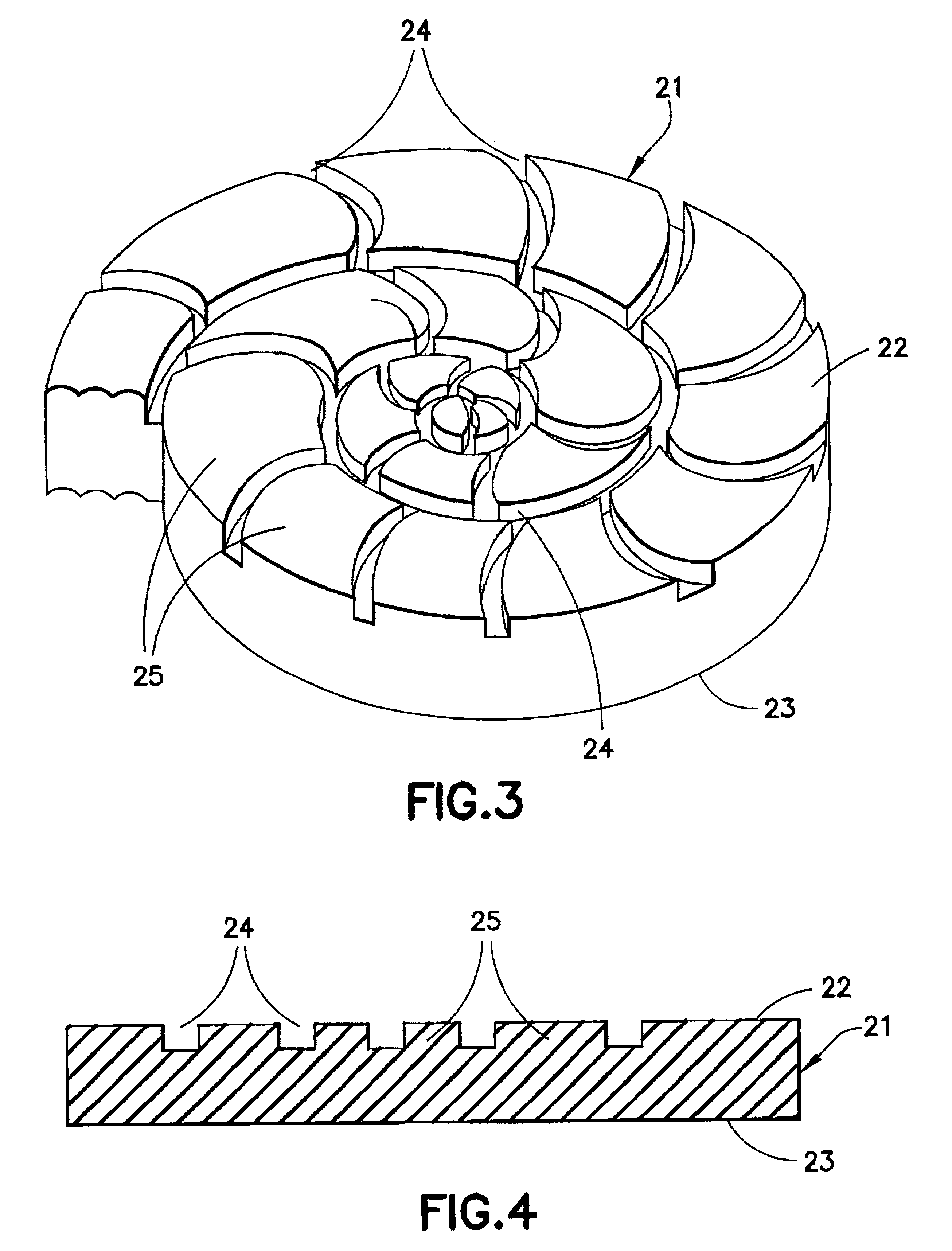

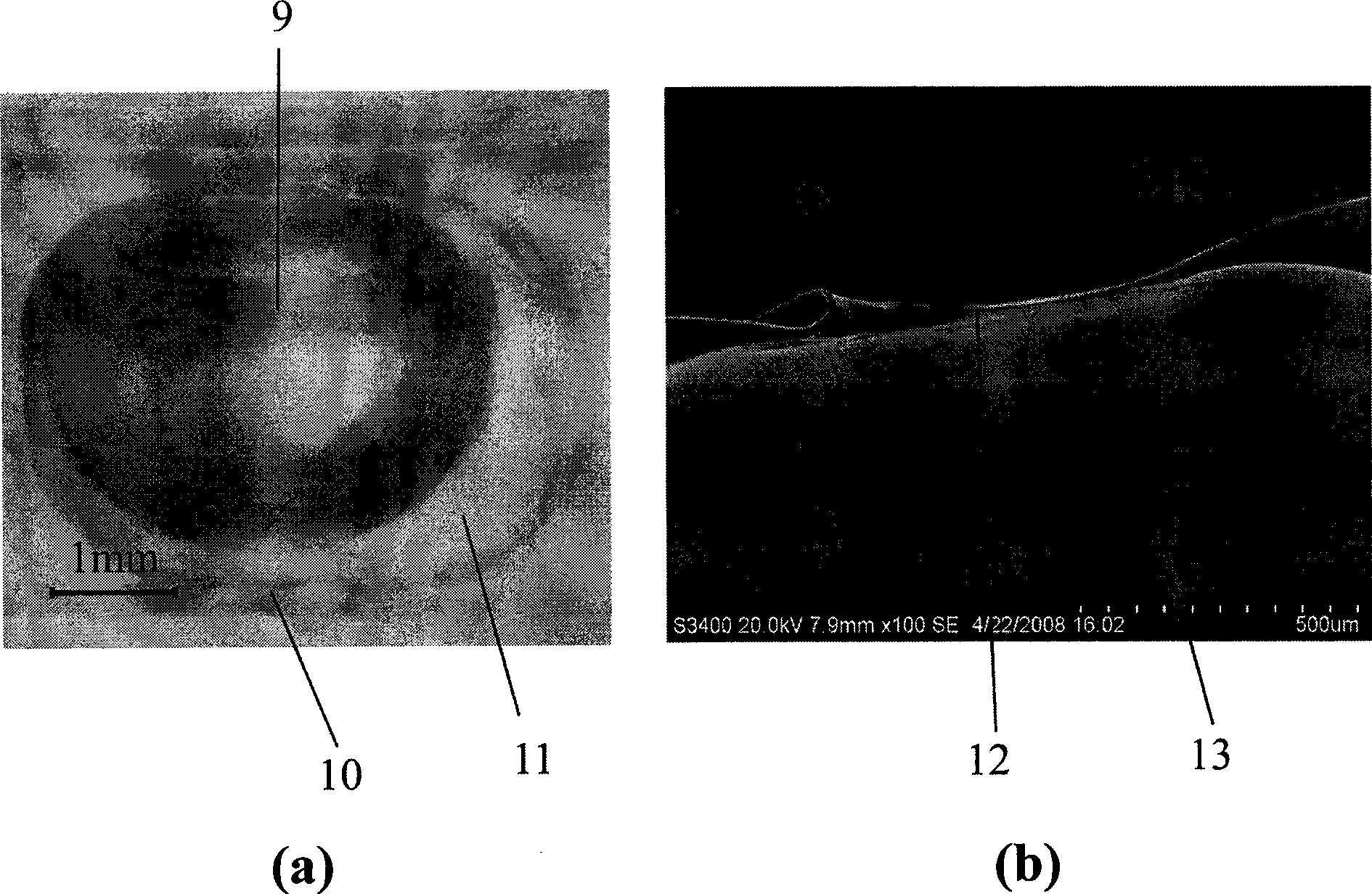

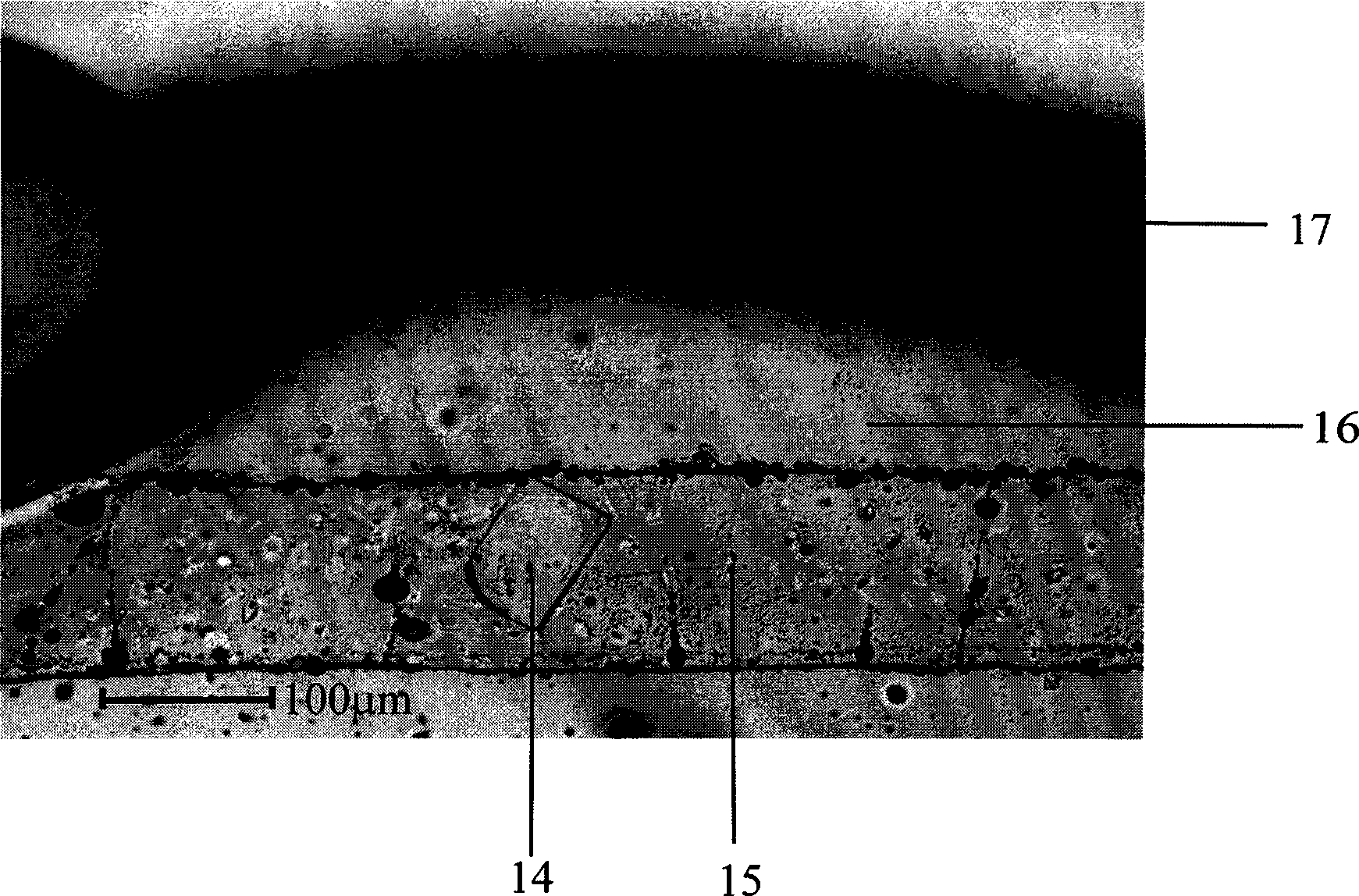

Optical fiber vibration sensing head and manufacturing method thereof

InactiveCN101608944AWide operating frequency rangeAggressive and obviously mass-producedSubsonic/sonic/ultrasonic wave measurementPhotomechanical apparatusFiberVibration acceleration

The invention discloses an optical fiber vibration sensing head, which consists of a vibration sensitive chip, a dual fiber collimator and an encapsulation shell, wherein the inside of the encapsulation shell under the dual fiber collimator is provided with a cavity, the vibration sensitive chip is arranged in the cavity and consists of micro light reflector, a silicon supporting frame and a substrate glass sheet; the silicon supporting frame is bonded with the substrate glass sheet; the micro light reflector is arranged in the silicon supporting frame; a damping air cavity is reserved between the micro light reflector and the substrate glass sheet; two sides of the micro light reflector is symmetrically provided with torsion shafts; and one end of each of the torsion shaft is connected with the silicon supporting frame. An MEMS process is used to integrate a MEMS vibration sensitive chip. Based on an asymmetric torsion micro light reflector structure, the MEMS vibration sensitive chip can be manufactured in batch. The torsion shafts are used as elastic elements, and the micro light reflector is used as a sensitive mass block to reflect vibration acceleration. The damping air cavity is used for controlling the damping characteristic of torsion. The invention has the advantages of batch production, low cost and high consistency.

Owner:上海前所光电科技有限公司

Manufacturing method of subminiature MEMS gyroscope sensor

InactiveCN101844739AReduce area sizeReduce areaTelevision system detailsSemi-permeable membranesSputteringResist

The invention discloses a manufacturing method of a subminiature MEMS gyroscope sensor, which comprises the following steps: providing MEMS wafer, depositing silicon dioxide through a CVD process, and then depositing silicon nitride through the CVD process; etching the patterns of silicon dioxide and silicon nitride on the front surface of the wafer, etching the wafer through using a RIE process, and forming a spring area and a metal landfill area in an MEMS structure; sputtering a metal layer on the front surface of the wafer to be as a seed layer, exposing the landfill area after photoetching, filling metal the density of which is more than that of silicon at the metal landfill area; removing photosensitive resist on the front surface of the MEMS wafer, removing the seed layer of the rest positions of the surface of the wafer; preparing sheet glass two sides of which are polished, corroding a groove on the glass by using a dry method to form a gap between a mass block and a glass cavity on the wafer; and sputtering metal on the back of the wafer, forming electrode after photoetching, and finally removing the photosensitive resist. The invention reduces the dimension of the mass block or increases the mass of the mass block.

Owner:SENODIA TECH (SHANGHAI) CO LTD

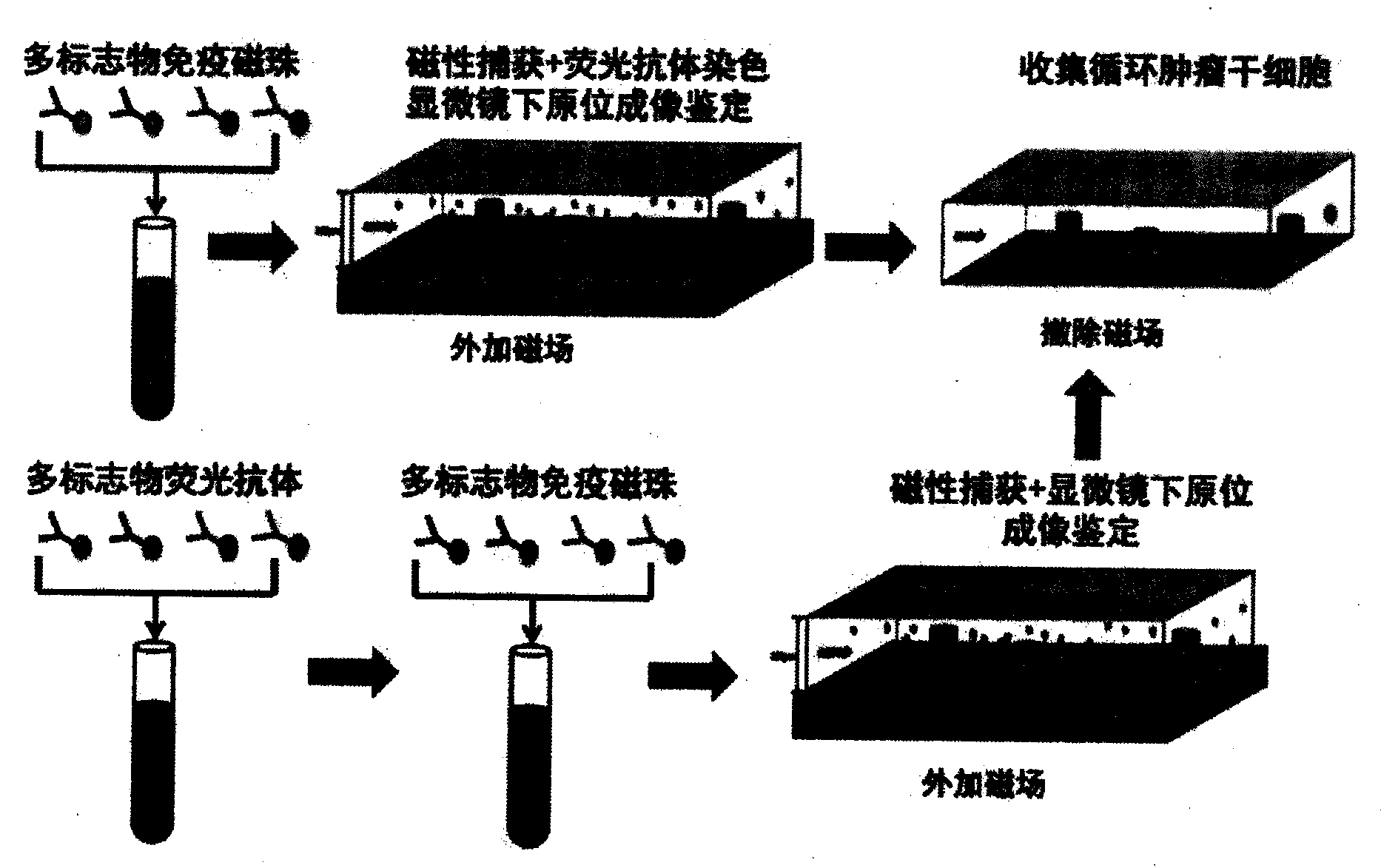

Circulating tumor stem cell detection kit based on magnetic beads and microfluidic chip

ActiveCN103869060AEasy to collectImplement classification detectionMaterial analysisGlass chipFluorescence

The invention provides a circulating tumor stem cell detection kit based on magnetic beads and a microfluidic chip. The circulating tumor stem cell detection kit is characterized by comprising a microfluidic chip, at least one immunomagnetic bead, and at least one fluorescent antibody against a tumor stem cell biomarker, wherein the immunomagnetic bead can be specifically bonded with the circulating tumor stem cell and marked with the tumor stem cell biomarker; the microfluidic chip comprises a glass chip base; a microfluidic channel is arranged on the glass chip base; a soft magnetic micro-array is arranged inside the microfluidic channel. By adopting the circulating tumor stem cell detection kit, a plurality of different categories of rare circulating tumor stem cells can be captured and detected by sampling once, and the circulating tumor stem cell detection kit has high sensitivity and specificity, is convenient and fast to operate, can easily collect captured cells, and does not need complicated surface modification processes of a first antibody and a second antibody of the microfluidic channel inside the chip.

Owner:ZHONGSHAN HOSPITAL FUDAN UNIV

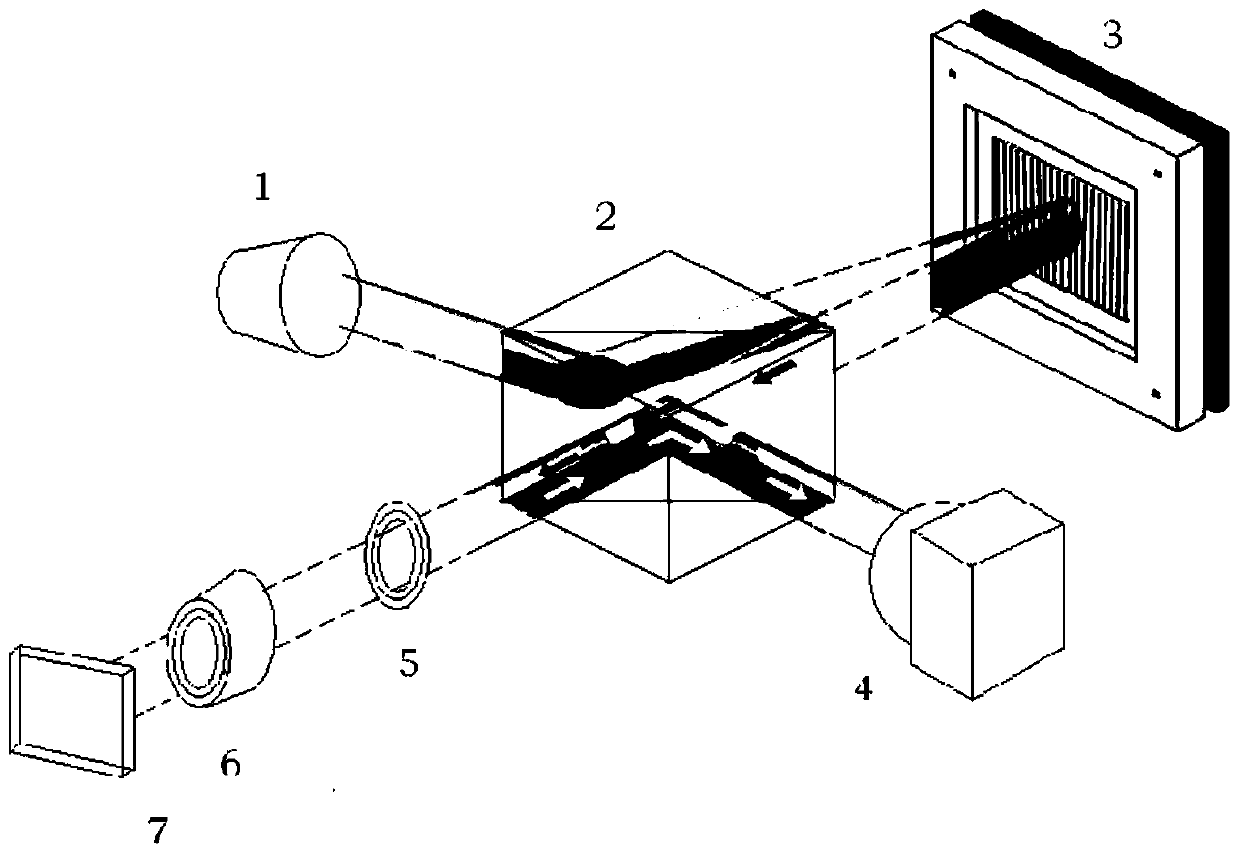

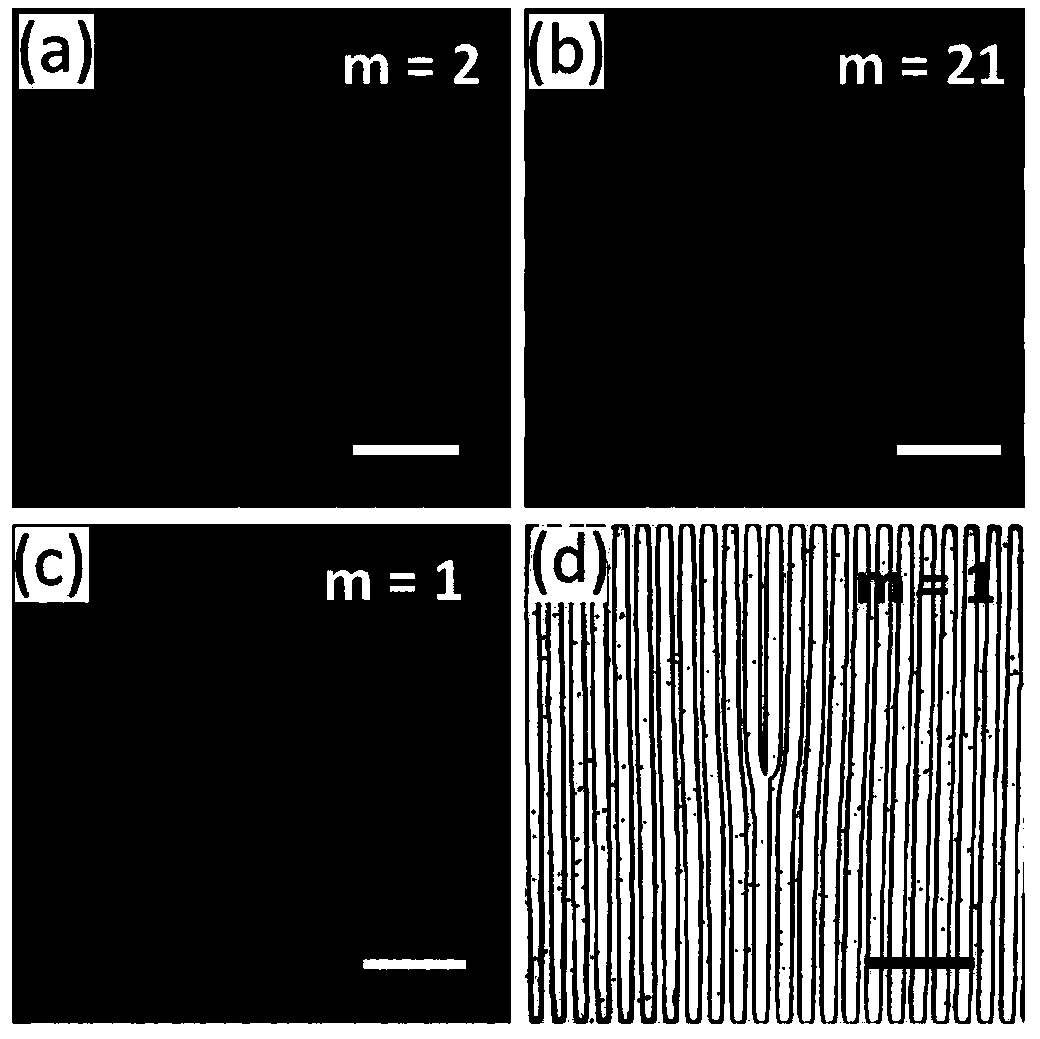

Forked liquid crystal grating preparation method and application of forked liquid crystal grating in vortex beam

InactiveCN103792605AImprove light energy conversion efficiencyChange in real timeDiffraction gratingsNon-linear opticsLithographic artistOptical axis

A forked liquid crystal grating is characterized in that liquid crystal orientation of adjacent liquid crystal areas of the forked liquid crystal grating is controlled differently such that the following three types of forked liquid crystal gratings can be formed, namely a TN / PA-type forked liquid crystal grating, an orthogonal PA-type liquid crystal grating and an orthogonal HAN-type liquid crystal grating; 90-degree twisted phase microcells of liquid crystal and parallel-oriented microcells of and the liquid crystal are alternately arranged so as to form the TN / PA-type forked liquid crystal grating; uniformly parallel microcells of the liquid crystal of which optical axes are in the same region and microcells in an adjacent region which are orthogonal to each other are alternately arranged to form the orthogonal PA-type liquid crystal grating. According to the preparation of the forked liquid crystal grating, a photoalignment method is adopted to control liquid crystal micro orientation so as to control the director distribution of the liquid crystal. Since a digital?micro-mirror device (DMD)-based micro projection-type lithography system is realized, a digital control device outputs liquid crystal forked gritting pattern signals to control the reflected light of each pixel of a digital?micro-mirror device (DMD), such that the imaging of a liquid crystal forked grating pattern can be realized; and after being narrowed through a micro objective, light beams are projected to photoalignment material agent conductive glass through a polarizing film.

Owner:NANJING UNIV

Two-layer protective coating system for LCD glass

InactiveUS6896928B2Same and smoothnessImprove scratch resistancePretreated surfacesRecord information storageSolubilityGlass chip

Two-layer protective coating system for glass surfaces is disclosed. The base coating comprises at least one polysaccharide, and the top coating has a lower solubility in water than the base coating. The coating system provides good protection against contaminants and glass chips, good removability in mild cleaning condition, and extra water resistance during process steps where water is used as a cooling agent.

Owner:CORNING INC

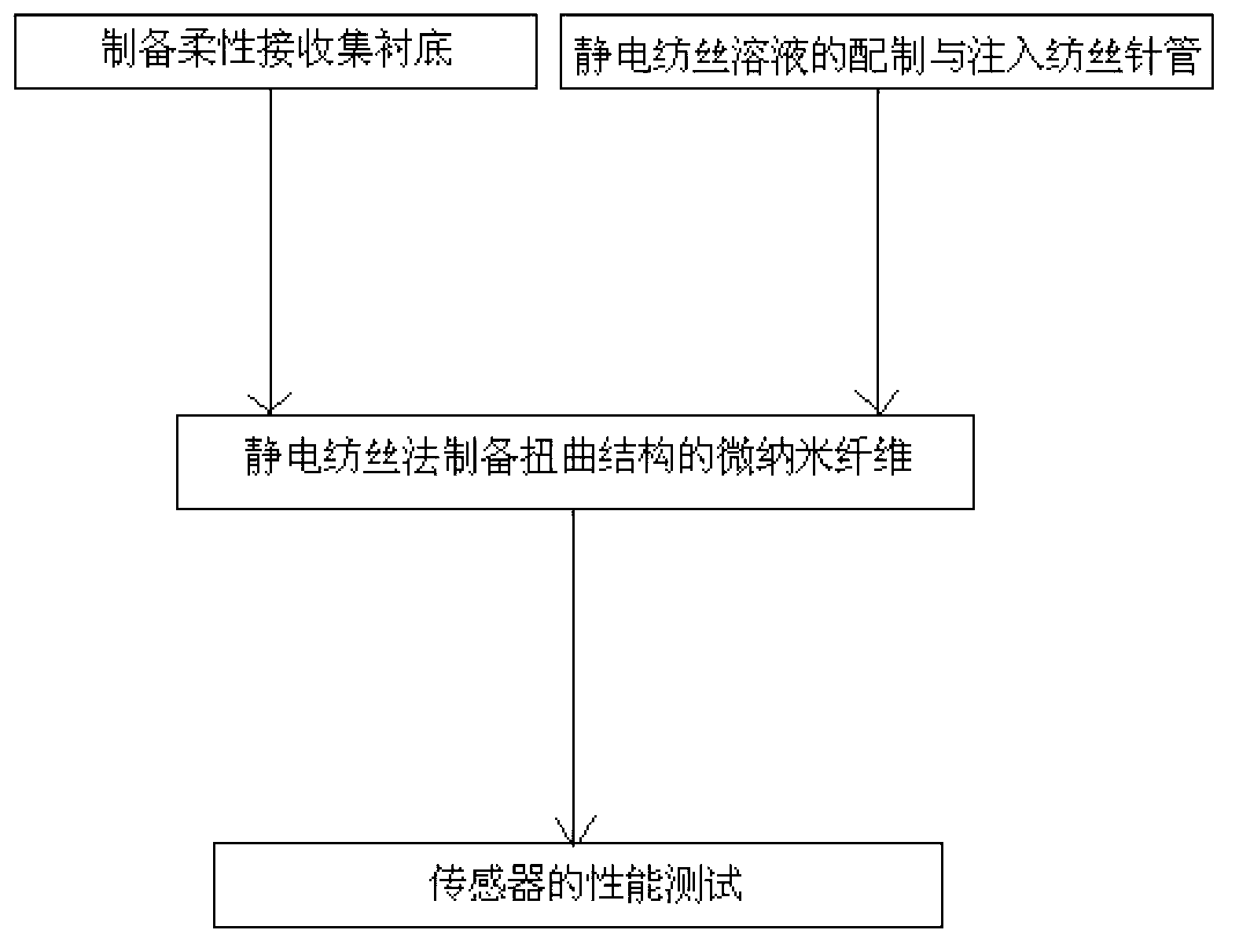

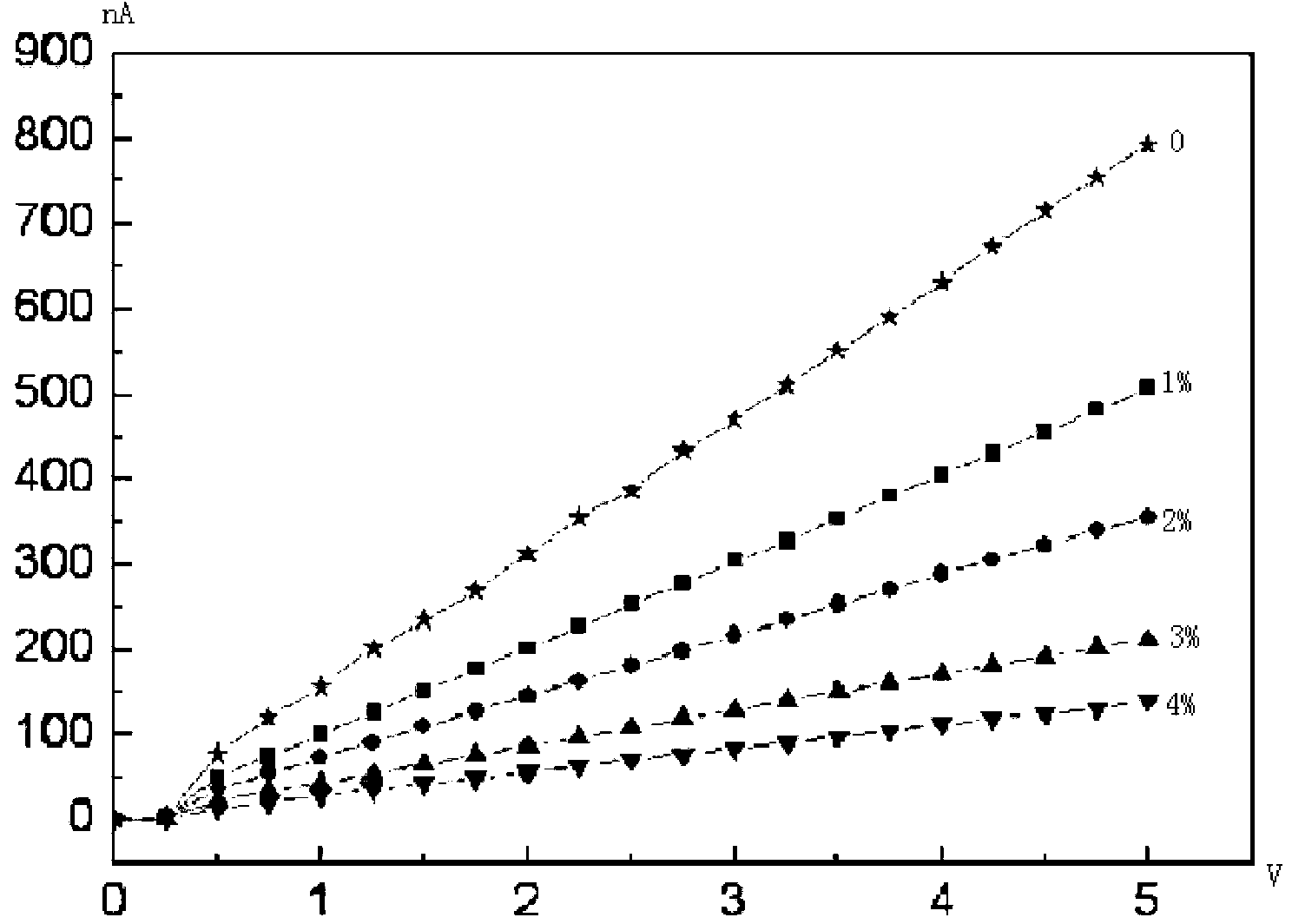

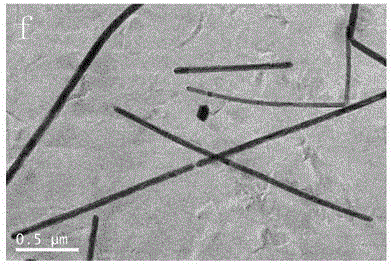

Preparation method of flexible tensile strain type sensor

InactiveCN103076031AQuick responseStrong resistance to deformationConverting sensor output electrically/magneticallyFiberEngineering

The invention relates to a preparation method of a flexible tensile strain type sensor and belongs to the technical field of sensor preparation. The preparation method concretely comprises four steps including flexible receiving set substrate preparation, electrostatic spinning solution preparation and filling into spinning needle tubes, distortion structure micro-nanometer fiber preparation by a electrostatic spinning method and sensor performance test: an elastic macromolecule material substrate is fixedly arranged on a glass sheet, and then, the glass sheet is placed on an aluminum foil of a power supply negative electrode; PVP (polyvinylpyrrolidone) ethanol solution of PEDOT / PSS (poly-3,4-ethylenedioxythiophene / polystyrolsulfon acid) blended with DMSO (dimethyl sulfoxide) is prepared as spinning solution and is filled into spinning needle tubes; distortion structure micro-nanometer fibers are prepared by selecting a spinning spraying head reciprocating linear motion type electrostatic spinning device; and the prepared sensor is subjected to performance test. The preparation method is simple, the principle is reliable, the preparation cost is low, the product performance is good, the operation is simple and convenient, the yield is high, and the environment is friendly.

Owner:QINGDAO UNIV

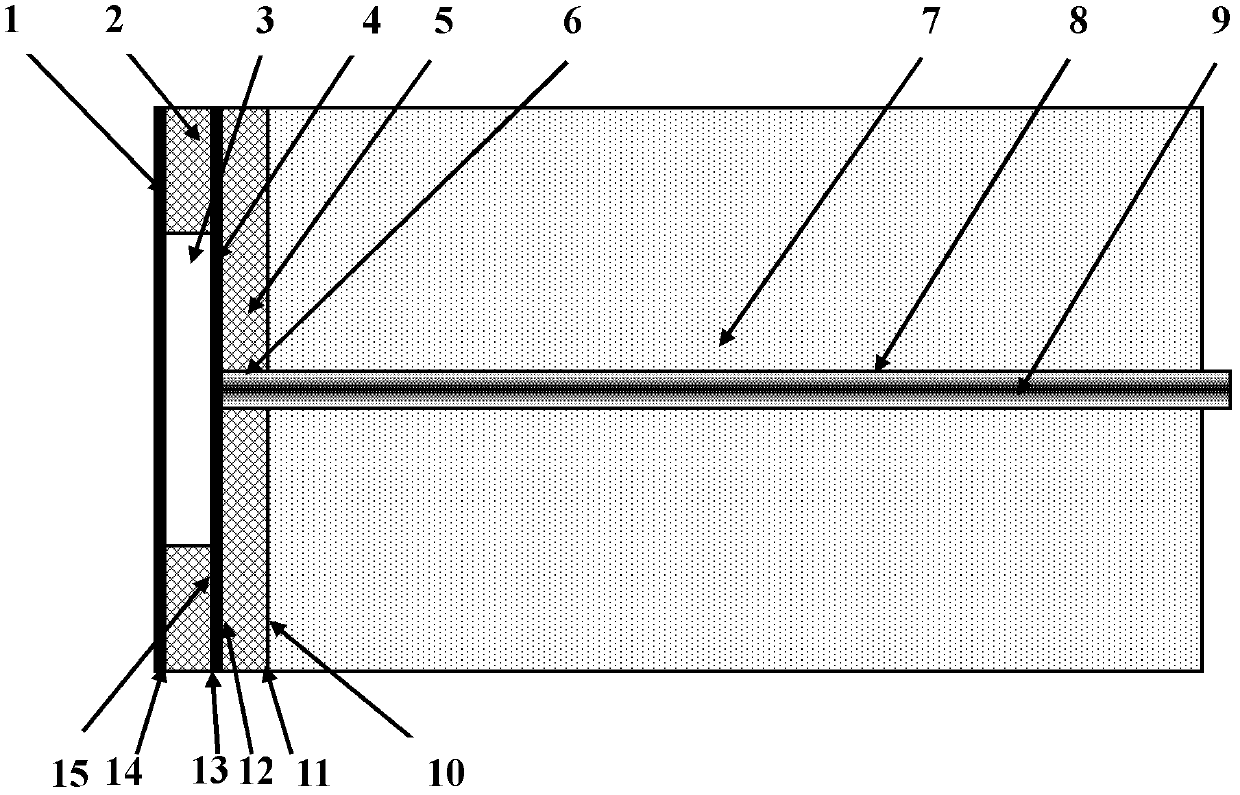

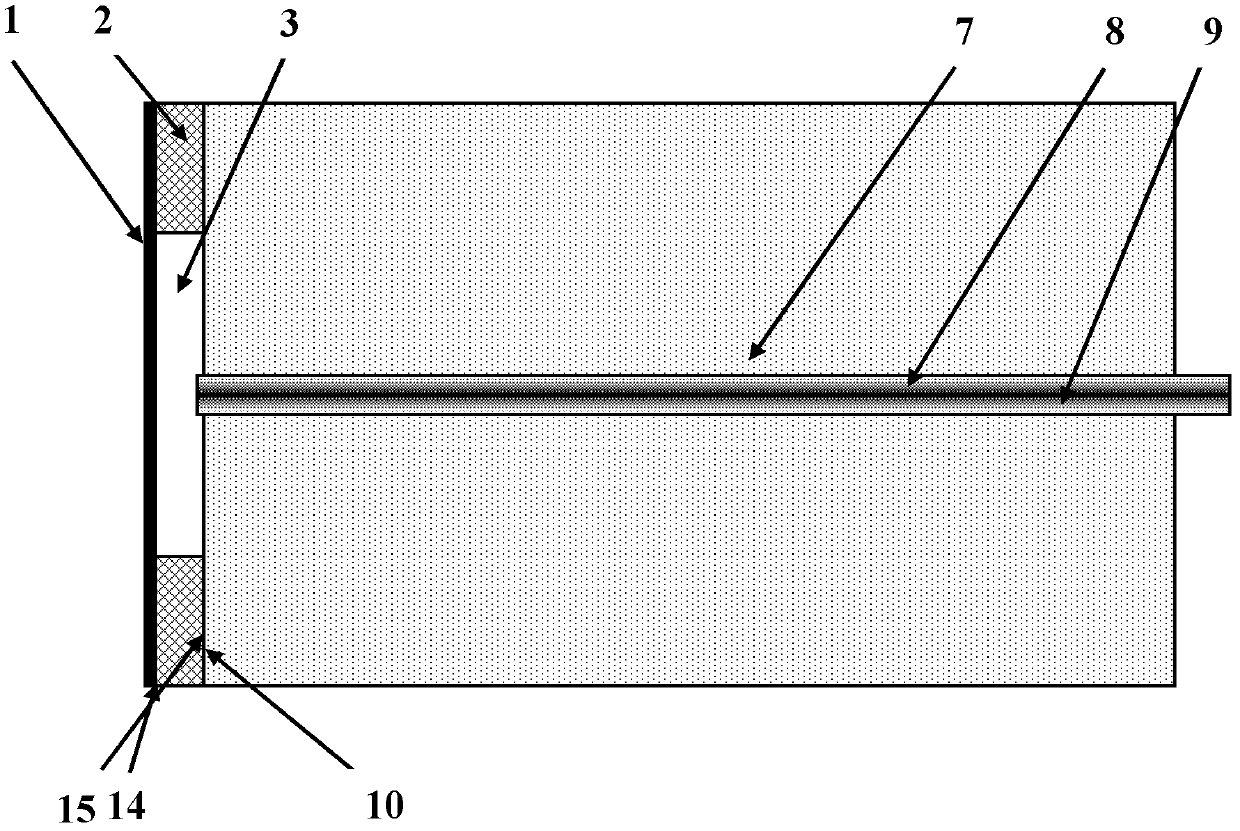

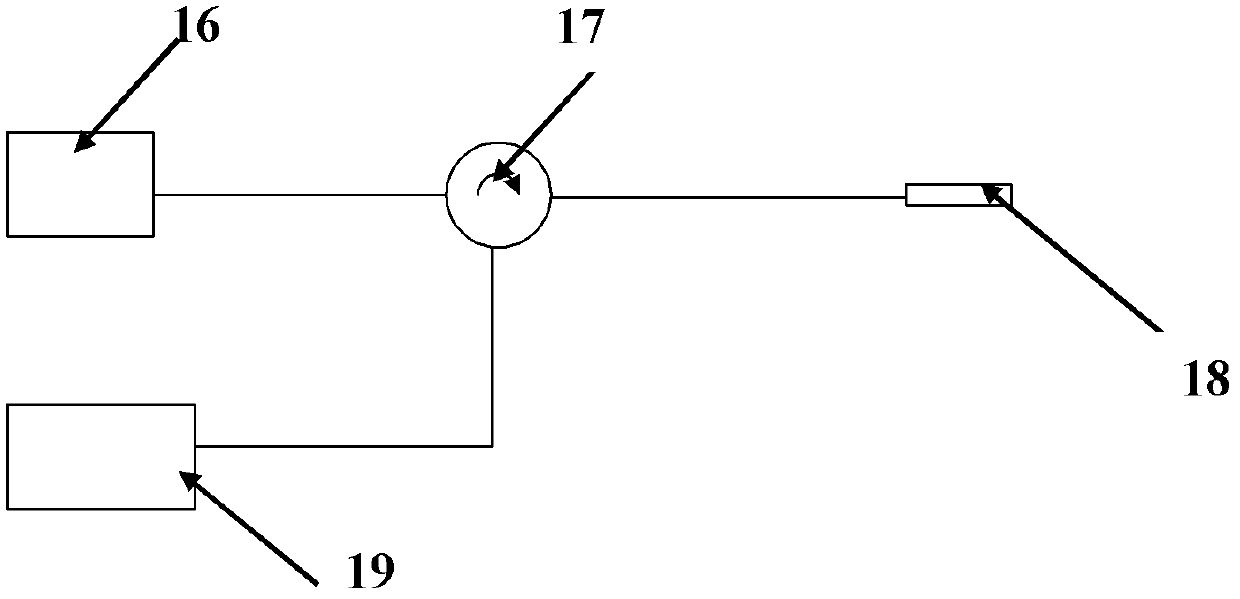

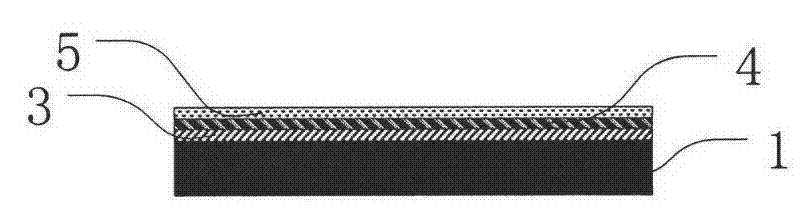

Glass chip packaging method

ActiveCN106449439AEasy extractionConvenient and lossless extractionSemiconductor/solid-state device manufacturingCrazingNonlinear absorption

The invention discloses a glass chip packaging method. A penetrating conductive metal electrode is prefabricated in the thickness direction of a glass sheet, and laser welding packaging is carried out on a glass chip by adopting ultrafast laser light. By using an ultra-high light intensity characteristic of ultra-short pulse laser light, a nonlinear absorption effect is generated in a transparent medium and the transparent medium is melted on a focus point, so that selective micro-welding in a transparent material space is achieved. The structure size processed by the ultra-short pulse laser light can break through an optical diffraction limit and precise welding smaller than a laser wavelength is achieved. Furthermore, the interaction time of the laser light and a material is extremely short, cracks and sputtered materials, caused by different expansion coefficients, of the material can be effectively avoided; and improvement of the welding packaging precision and quality is facilitated. Compared with other packaging technologies of bonding and the like, the glass chip packaging method has the advantages that the manufacturing process is simple, the thickness of the chip is not limited, fillers of different materials do not need to be added, the strength performance, the stability and the reliability of glass chip packaging can be improved and the service life of the glass chip is prolonged.

Owner:HUAZHONG UNIV OF SCI & TECH

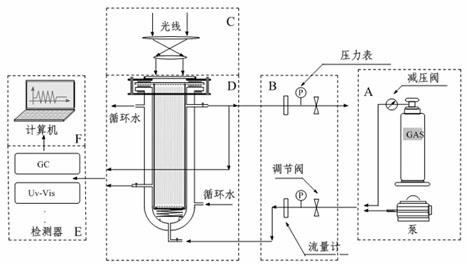

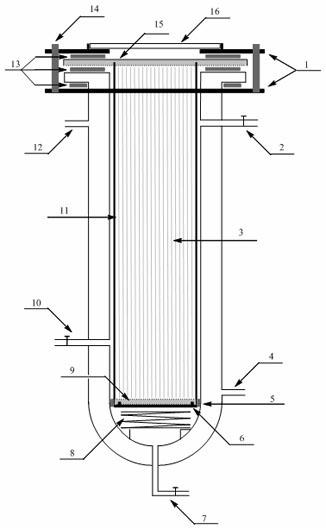

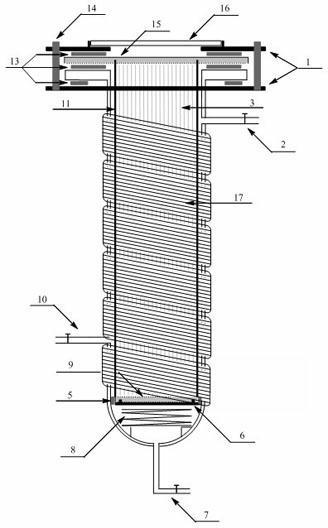

Titanium dioxide photo-catalytic micro-reactor

InactiveCN102580651ARaise the ratioSmall attenuationEnergy based chemical/physical/physico-chemical processesReaction layerFiber

The invention discloses a titanium dioxide photo-catalytic micro-reactor, characterized in that in the reactor, the lower ends of fibers are supported on a porous glass sand separator through a porous glass sheet, the upper end is fixed with a translucent sheet, the bottom of the reactor is provided with an air inlet pipe, and the side of the reactor is provided with a testing port and an injection port. According to the invention, the ratio of effective catalytic surface area to reactive volume is raised, the incident mode of a light source is changed into an internal reflection mode from a traditional external reflection mode, thus the attenuation after the light passes through the solution is reduced, and the utilization rate of the light is raised; compared with TiO2 nano-particles, the TiO2 nanotubes used as the photoreaction catalyst have higher catalysis catalysis effect; and compared with traditional coating modes, the reaction layer obtained by the catalyst layer of the photoreaction unit is more uniform, compact and firm.

Owner:NORTHWEST UNIV

Preparation method of glass substrate graphene/silver nano wire transparent conductive film

InactiveCN104934109AImprove conductivityImprove uniformity and stabilityConductive layers on insulating-supportsCable/conductor manufactureGlass chipGraphene flake

The invention discloses a preparation method of a glass substrate graphene / silver nano wire transparent conductive film, and belongs to the field of chemistry. The method comprises the following steps: A, preparing a stable and dispersive oxidized graphene colloid aqueous solution by use of graphite; B, preparing a 1-1.5mg / ml silver nano wire / graphene hybrid aqueous solution as a precursor for later use; C, processing a glass piece; D, manufacturing the silver nano wire / graphne transparent conductive film on the glass piece; and E, performing post treatment. According to the invention, one-dimensional silver nano wires are assembled on a graphene sheet layer through a simple hot pot method, the advantages of the fiber structures of the nano wires can be brought into full play, a good conductive network can be formed in a carrier of a graphene film, and the conductivity of the graphene film can be improved.

Owner:林州市清华·红旗渠新材料产业化发展中心

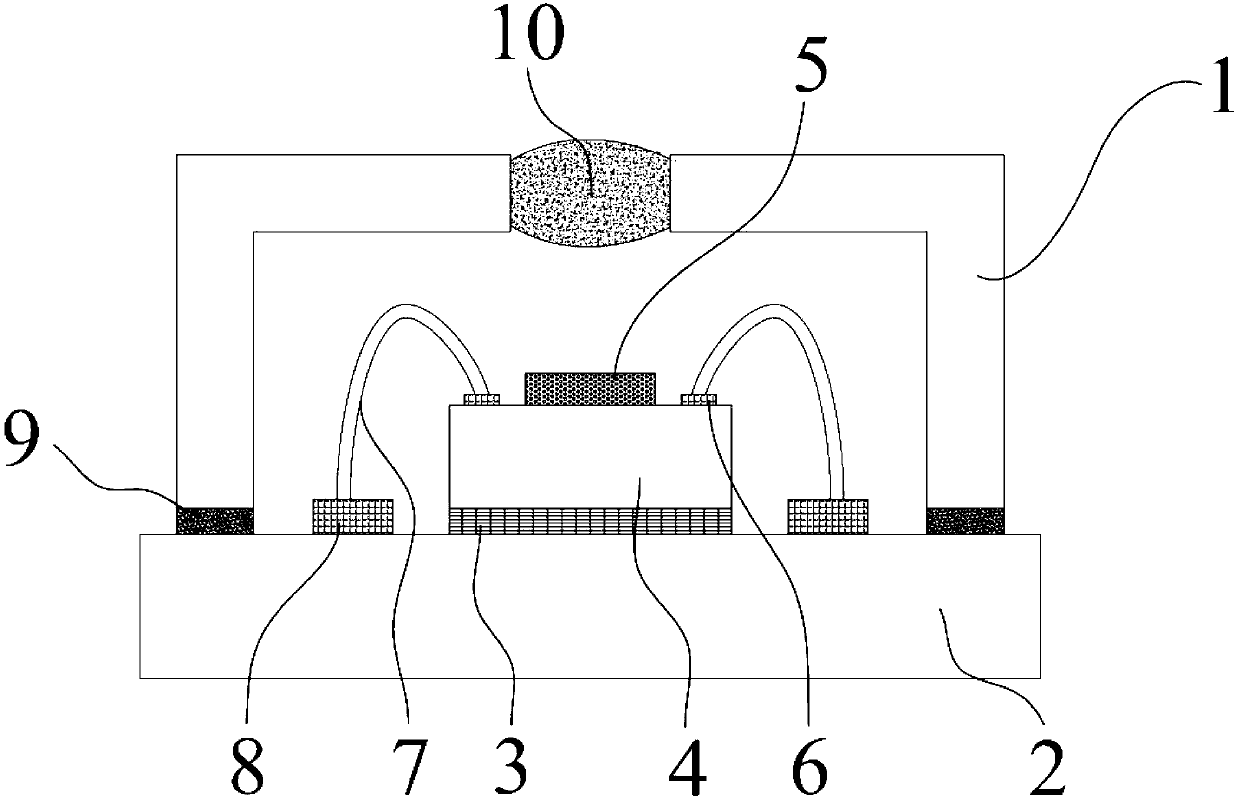

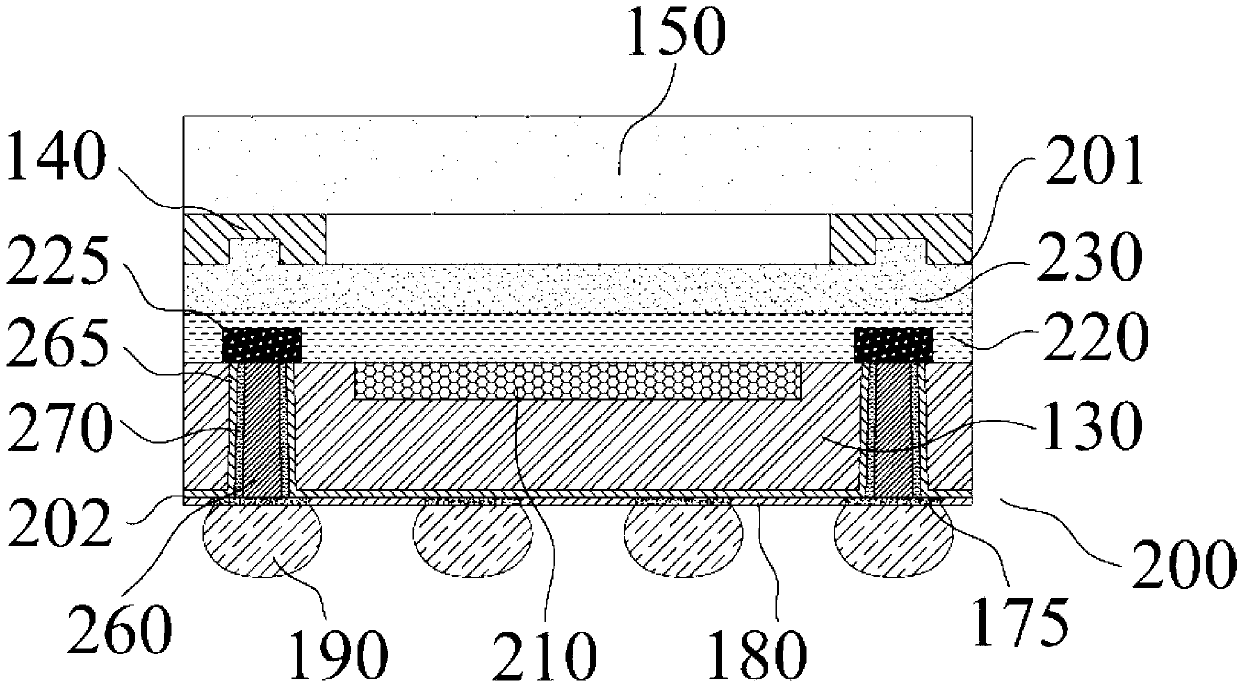

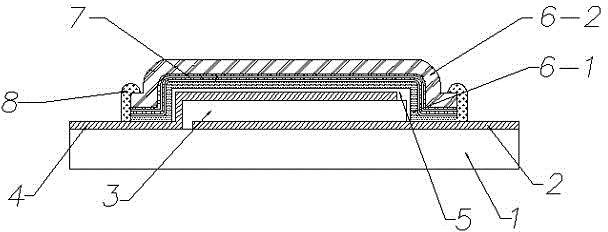

Large chip scale package and manufacturing method thereof

InactiveCN103000648AImprove bond strengthImprove layeringRadiation controlled devicesEngineeringInput/output

The invention provides large chip scale package and a manufacturing method thereof and belongs to the technical field of sensors. An optical interaction region is arranged at the center above a silicon substrate in a first surface of a wafer, one side provided with the optical interaction region is connected with a metal interconnection structure, and an input-output (I / O) around the optical interaction region on the silicon substrate is connected to an electrode pad through the metal interconnection structure. The surface of the metal interconnection structure is provided with a protective layer, and a stepped protrusion or groove structure is formed on the protective layer. The first surface of the wafer is bonded with a glass piece together, and a cavity is formed between the glass piece and the wafer. A second surface of the wafer is provided with a through silicon via (TSV) hole, the electrode pad penetrates through the silicon substrate through the TSV hole to be connected to a bonding pad on the second surface of the wafer, a passivation layer and a metal liner are sequentially manufactured on a hole wall of the TSV hole, and a polymer material is filled into the TSV hole. An anti-welding layer is manufactured on the second surface of the wafer, and a weld ball is manufactured on the bonding pad. By means of the large chip scale package and the manufacturing method, the layering problem of glass and the silicon substrate in an existing package structure is solved, and the packing reliability is improved.

Owner:BEIJING UNIV OF TECH

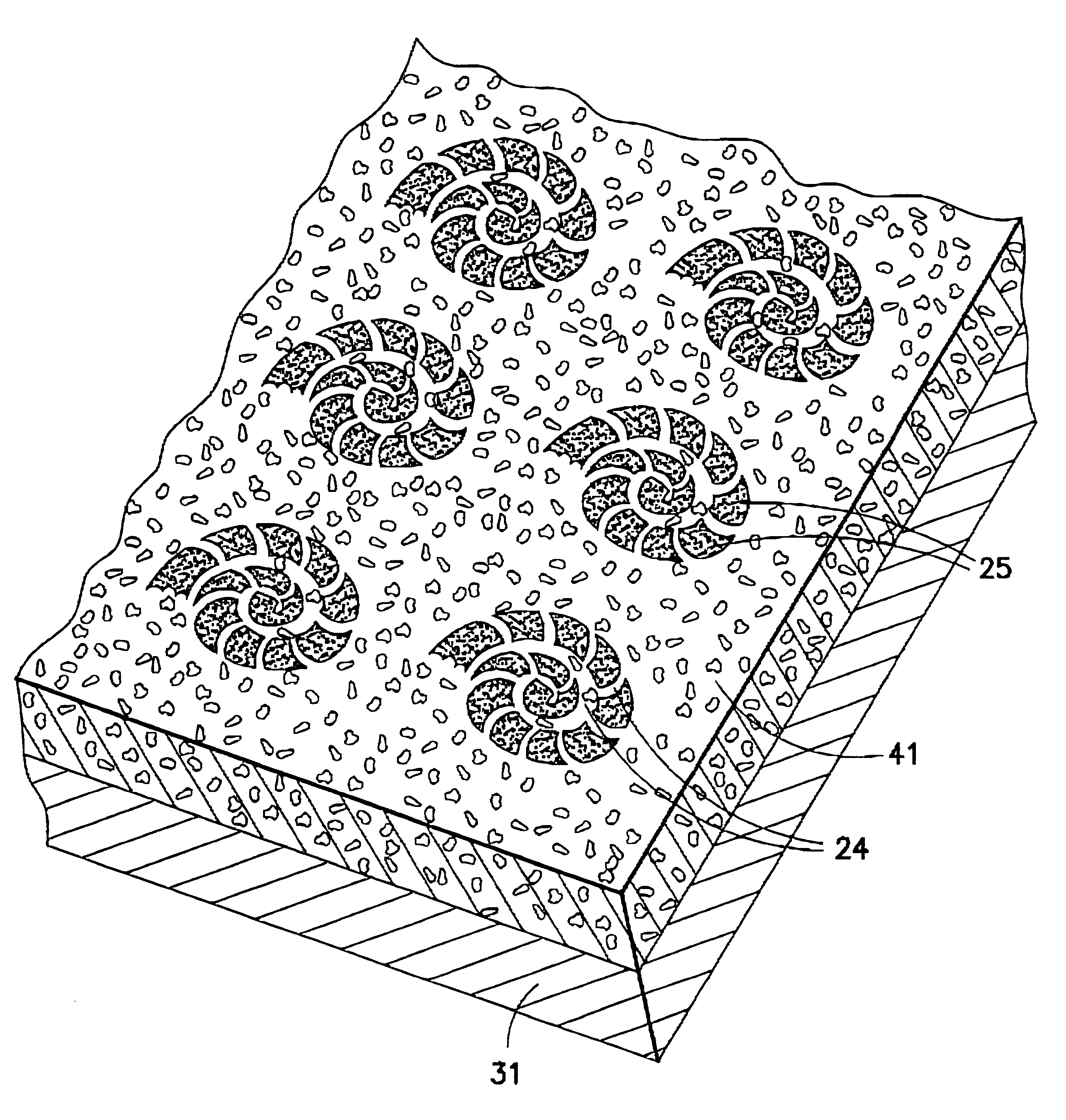

Method of making monolithic terrazzo floors having seamlessly integrated inlays

A method of making terrazzo floors with design inlays. The method utilizes pre-molded inserts as inlays in the finished floor, and generally includes four steps. First, inserts are pre-molded, which has design elements in terms of their color, nature of inclusions (chips, glass fragments, etc. and their colors), shape and / or a pattern of grooves in their upper surfaces. Second, the pre-molded inserts are placed on and affixed to the sub-flooring in a predetermined arrangement. Third, epoxy flooring mixture is poured to a height that fills the grooves in the inserts' upper surfaces and preferably cover the inserts. Fourth, the floor, after cured and hardened, is ground and polished to expose the upper surfaces of the inserts, which now become seamlessly integrated inlays within the overall finished floor. The designs in the inlays are viewable because the inserts contain different visual ingredients (pigments, colored plastic or glass chips, etc) in contrast with the overall floor and they are outlined by the filled grooves.

Owner:SEDAKA ALEN

Adhesive tape encapsulating structure of organic light emitting diode

InactiveCN103956435ASimple processIncrease production speedSolid-state devicesSemiconductor/solid-state device manufacturingOrganic layerProtection layer

The invention relates to an adhesive tape encapsulating structure of an organic light emitting diode (OLED). According to the adhesive tape encapsulating structure of the OLED, adhesive tape encapsulation is carried out on the OLED formed by a front electrode, an organic layer, a back electrode and a protection layer, the front electrode, the organic layer and the back electrode are arranged on the upper face of a substrate, the OLED is sealed through adhesive tape which is arranged on the upper face of the OLED and formed by an adhesive sticker and a flexible film strip capable of preventing water vapor and oxygen from passing through, an air barrier layer formed by multilayer films of multilayer thin films made of different materials is further arranged on the upper face or the lower face of the flexible film strip, a layer of filter film can be further arranged on the lower face of the flexible film strip, a sealing rubber ring is arranged on the periphery of the sealing adhesive tape to cover the adhesive tape and the substrate so that air cannot permeate into the OLED from the periphery, and a thin glass sheet or a thin metal sheet can be further arranged on the upper face of the sealing rubber ring to prevent air from entering from the upper face. According to the adhesive tape encapsulating structure of the OLED, due to the fact that the main encapsulating process is the adhesive tape adhering process, the technological process of the adhesive tape encapsulating structure is much simpler relative to a previous method, the production speed can be improved, production cost is lowered, and the adhesive tape encapsulating structure is especially suitable for large-area and large-batch production.

Owner:SHANGHAI UNIV

Ultraviolet flame sensor and manufacturing method thereof

InactiveCN101251416AThe overall structure is small and beautifulGuaranteed spacingSpectrum investigationPhotometryGlass chipPhotocathode

An ultraviolet flame sensor and a manufacturing method thereof relate to a solar blind type ultraviolet flame sensor. The invention provides the ultraviolet flame sensor with simple structure, small size, high stability, high strength and high linearity and sensitivity, and the sensor manufacturing method with good versatility, simple technique and low cost. The invention is characterized in that: the ultraviolet flame sensor comprises a uviol piece, a meshed anode which is arranged on the uviol piece, a cathode substrate glass piece, a photocathode which is arranged on the cathode substrate glass piece, a glass ring which is arranged between the cathode and the anode, a vacuum orifice which is arranged on the glass ring, a plastic packaged base which is arranged under the cathode substrate glass piece, a cathode and an anode lead which are adhered to the plastic packaged base and are respectively connected with the cathode and the anode, and a plastic casing which is arranged around the plastic packaged base, the glass ring and the glass piece.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Micro-fluidic apparatus integrated with PDMS film, manufacturing method and application thereof

InactiveCN101530775AImprove breathabilitySimple preparation stepsVolume/mass flow by thermal effectsFixed microstructural devicesFlat glassGlass chip

The invention relates to a micro-fluidic apparatus integrated with a polydimethyl siloxane (PDMS) film, which is structurally characterized in that a flat glass sheet is pasted with a PDMS sheet, the pasting face of the PDMS sheet and the glass is provided with a groove to form a micro-fluidic pipeline, the surface of the PDMS sheet on the upper part of the central position of the micro-fluidic pipeline is a concave spherical surface, the thickness of the PDMS sheet between the lowest point of the concave spherical surface and the micro-fluidic pipeline is less than or equal to 10 microns, the PDMS sheet at two ends of the micro-fluidic pipeline is respectively provided with pores, and the pores are communicated with the micro-fluidic pipeline so as to form a fluid storage tank. The micro-fluidic apparatus can be applied to experiments such as film evaporation and crystallization or biological molecule concentration and the like in a micro-fluidic system. Special equipment is not needed to manufacture the micro-fluidic apparatus, the manufacturing step is simple, the cost is low, and the micro-fluidic apparatus is easily popularized and used in common laboratories. The invention also discloses a method for manufacturing the micro-fluidic apparatus.

Owner:NANJING UNIV

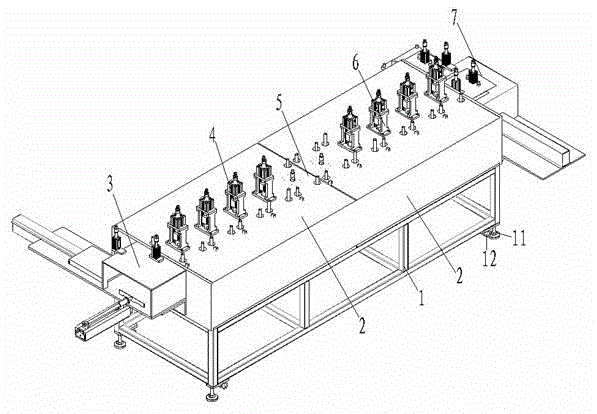

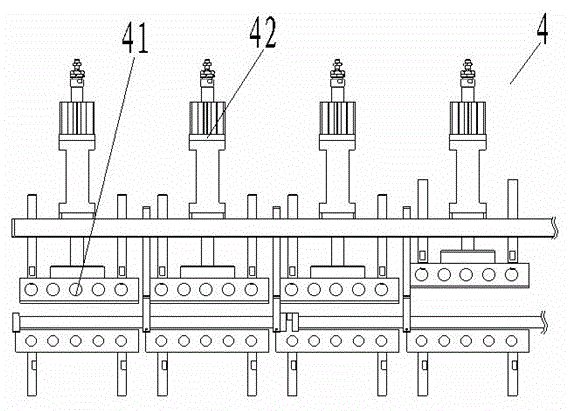

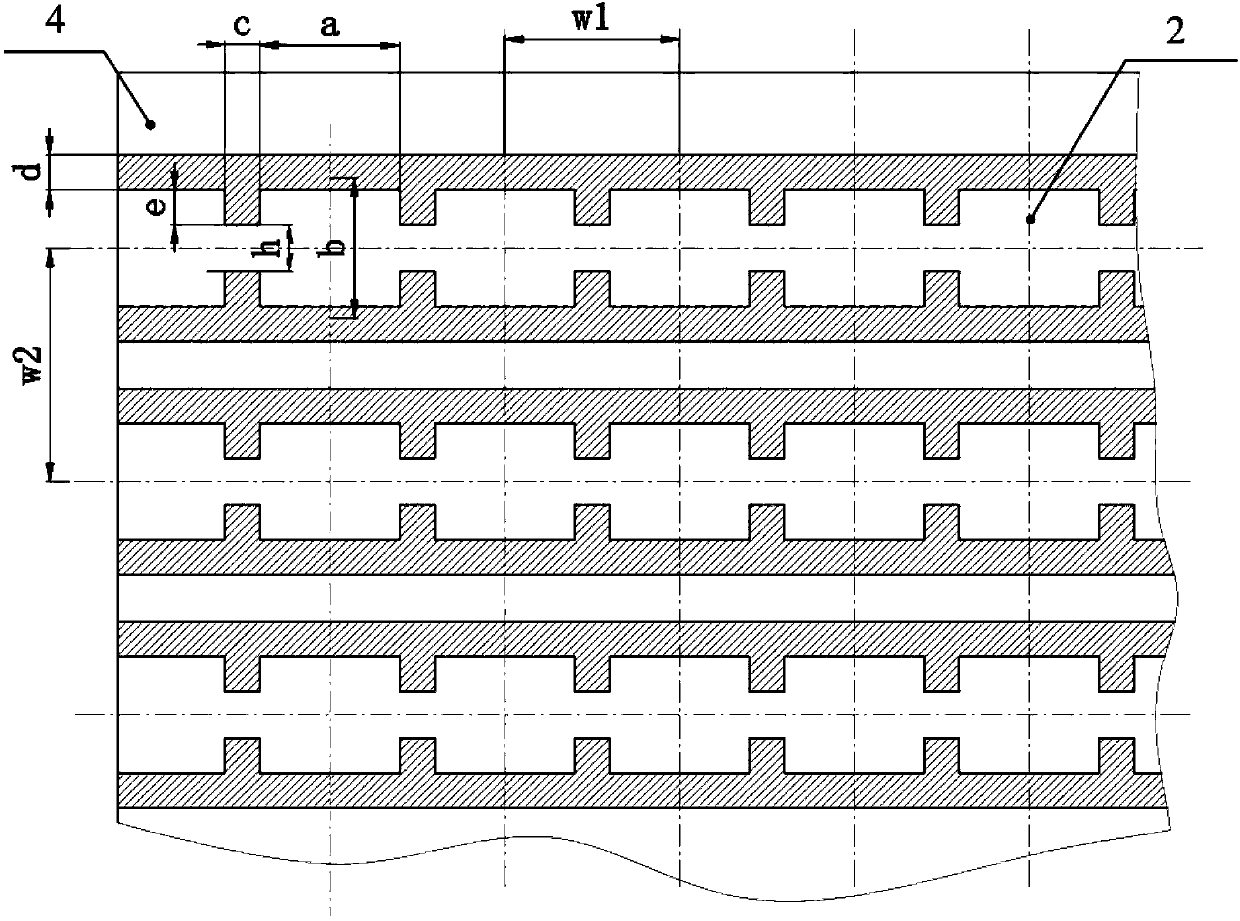

Machining device and machining technology for glass sheet hot bending molding

InactiveCN104986948AImprove loading performanceImprove sealingGlass reforming apparatusGlass productionEngineeringGraphite

The invention relates to the field of glass sheet hot bending molding, in particular to a machining device and machining technology for glass sheet hot bending molding. The machining device and machining technology finish machining through a jig structure and the simple process. The machining device mainly comprises a whole rack and a supporting part. The whole rack is of a rack structure with the periphery sealed and a cavity inside. The supporting part is arranged under the whole rack to support the whole rack. The inner cavity of the whole rack is sequentially and transversely provided with a preheating area, a molding area and a cooling area from left to right. Isolation areas are installed at the left end and the right end of the outer side of the whole rack. Meanwhile, the whole rack is provided with a conveying rail which is communicated with the isolation areas at the two ends and connected with the preheating area, the molding area and the cooling area. Glass sheets are loaded and pressed through a jig so as to finish the whole process of glass sheet hot bending molding. Loading performance of the graphite jig is stable, pressing and heating of the jig are uniform, the structure of the whole machining device is simplified, and the machining technology is simple.

Owner:东莞市华星镀膜科技有限公司

Fluorescent glass piece for white-light LED (Light Emitting Diode) and preparation method thereof

The invention discloses a fluorescent glass piece for a white-light LED (Light Emitting Diode) and a preparation method thereof. The fluorescent glass piece is characterized by being composed of a transparent glass substrate layer and a fluorescent glass layer which is melted to be integrated with the surface of the transparent glass substrate layer, wherein the fluorescent glass layer is prepared by steps of coating batch containing a basic solvent (glass powder) and fluorescent powder which hare in a certain proportion on the glass substrate and firing at certain temperature; and the preparation method is characterized by adopting the steps of coating the batch of the fluorescent glass on the glass substrate layer and firing at certain temperature and under the condition of normal-pressure air or N2 atmosphere. The fluorescent glass piece for the white-light LED is low in porosity and good in environmental stability, and is especially suitable for package of LEDs with low heat resistance and large power.

Owner:ANHUI LANRUI ELECTRONICS TECH

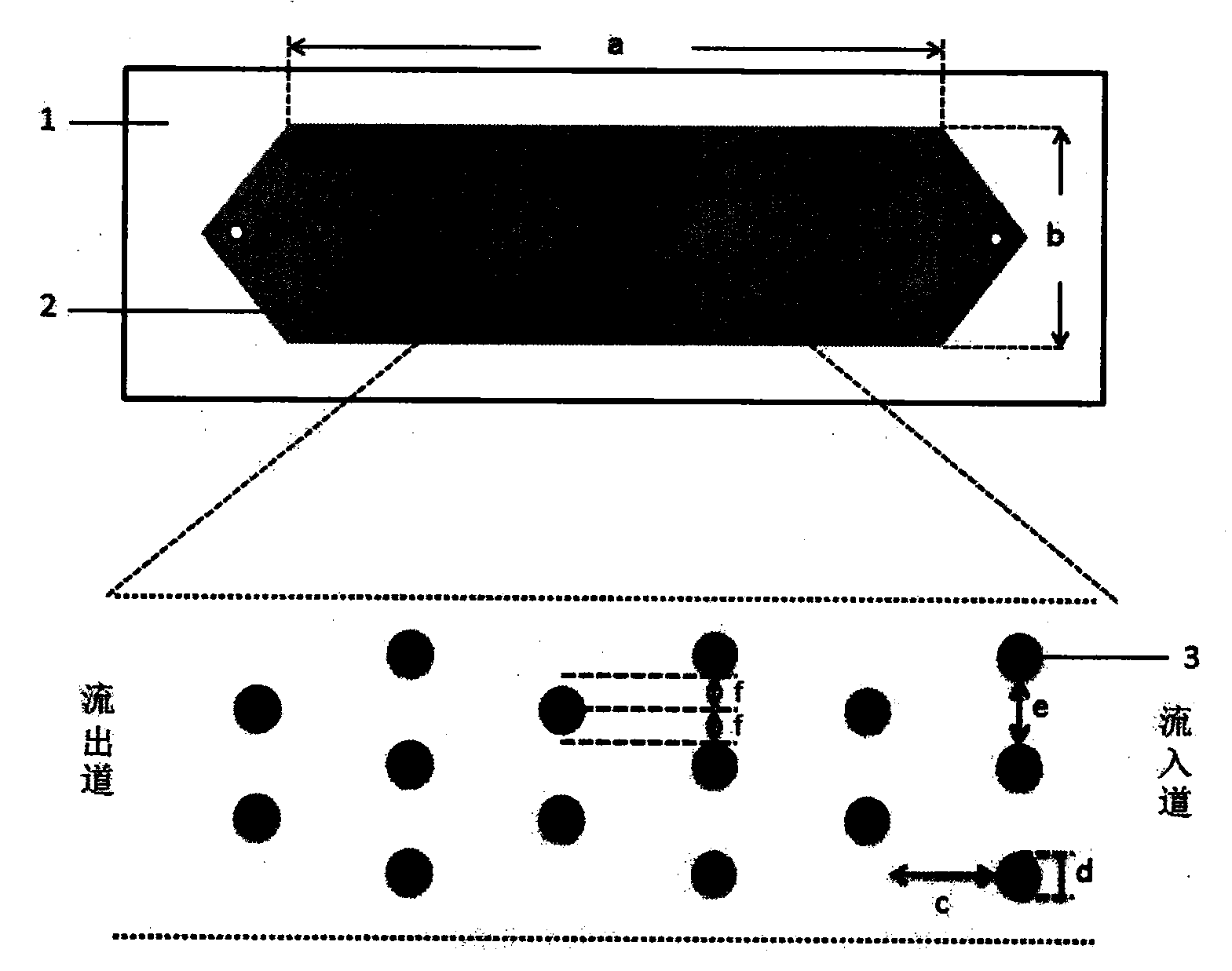

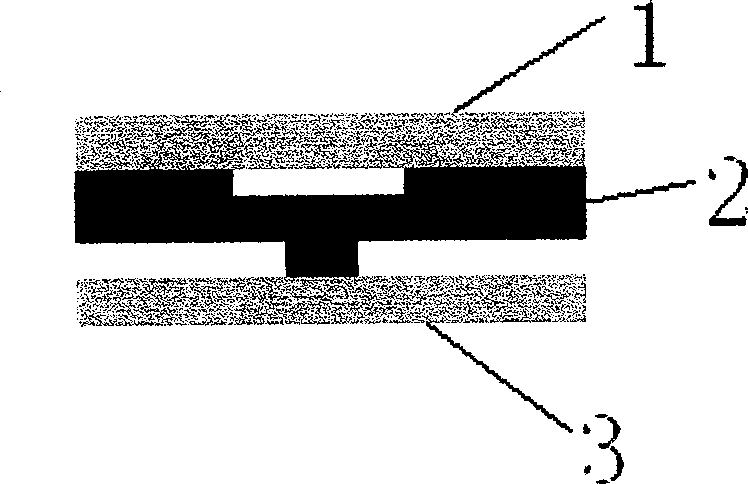

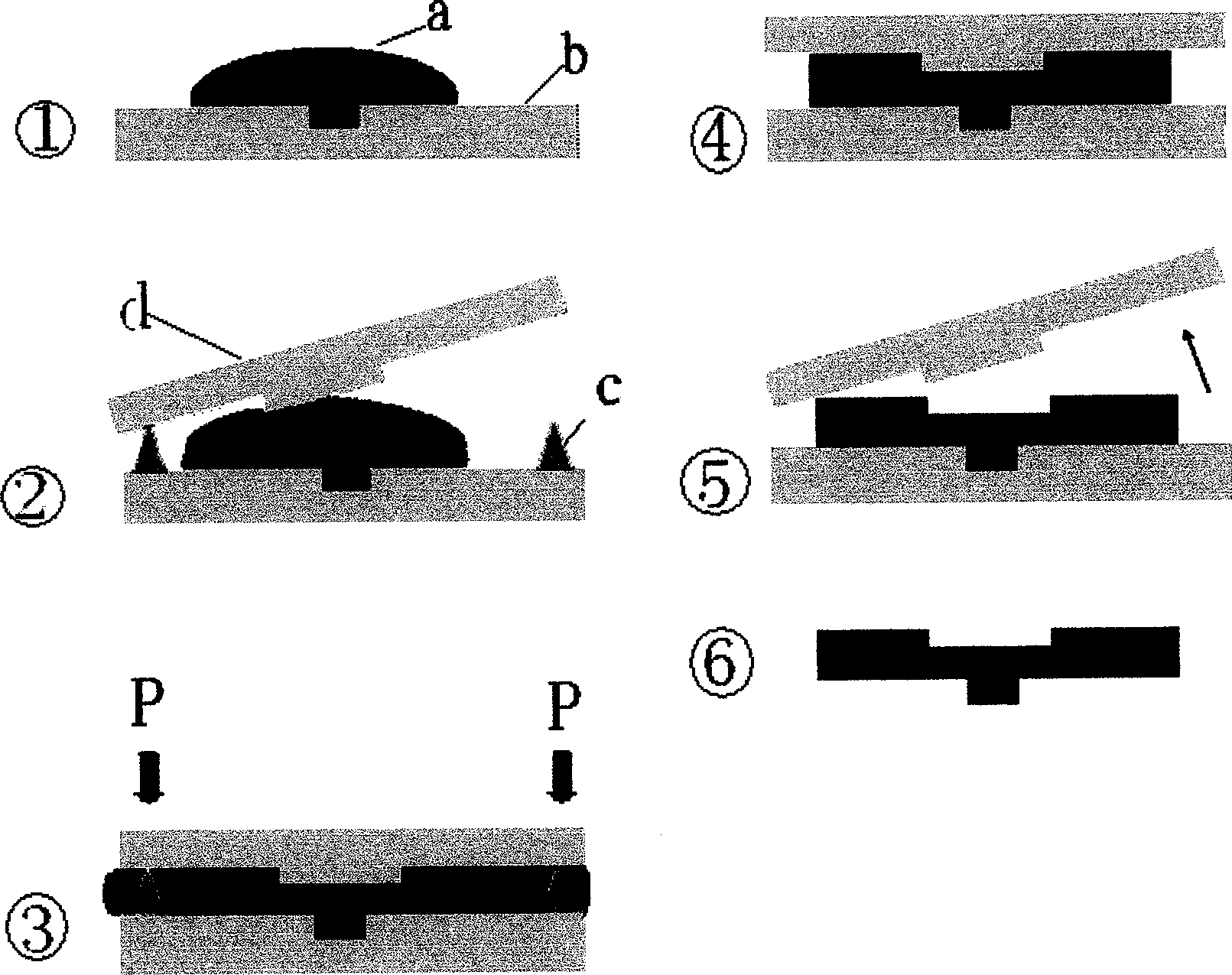

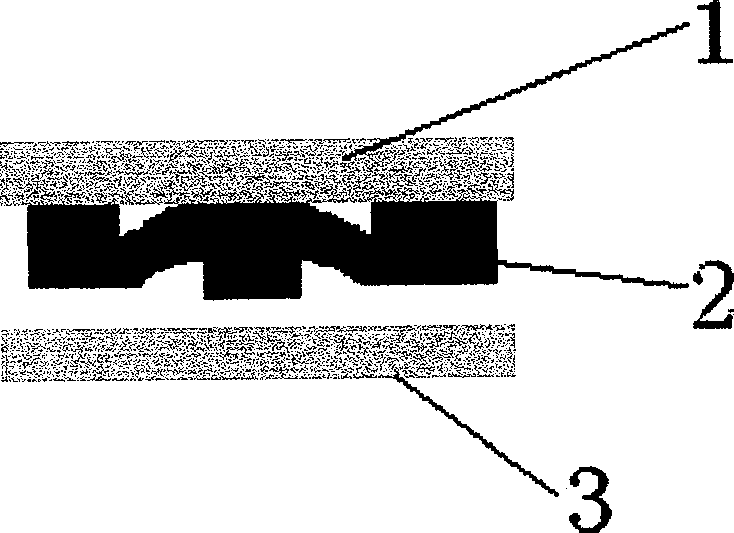

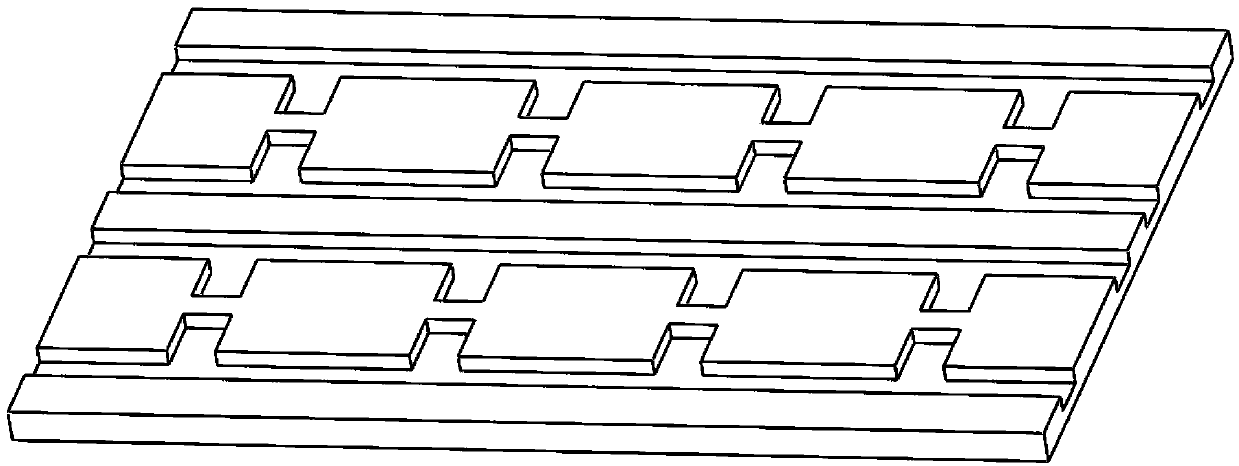

Integrated normal-closed PDMS micro-valve, preparation process thereof and micro-pump containing micro-valve

The invention provides an integrated normal-closed PDMS micro-valve, comprising an upper glass sheet 1, a lower glass sheet 3 and a PDMS film 2 that is arranged between the two glass sheets; wherein the upper glass sheet 1 contains a sample cell only; the lower glass sheet 3 contains an air path control hole only; and a fluid passage and an air path control passage are formed on two surfaces of the PDMS film 2 respectively. In the normal-closed valve, the fluid passage and the air path control passage are not etched on the upper glass sheet and the lower glass sheet, but formed on two surfaces of the middle PDMS film respectively; furthermore, two glass sheets only contain the sample cell and the air path control hole respectively; wherein the PDMS film can be repeatedly prepared by the same template, and the glass sheets only need to be drilled simply, thus reducing the template preparation steps of complex and high cost during the preparation process of the chip, thereby being more suitable for preparing the micro-fluidic chip of the integrated PDMS micro-valve / micro-pump.

Owner:DALIAN INST OF CHEM PHYSICS CHINESE ACAD OF SCI

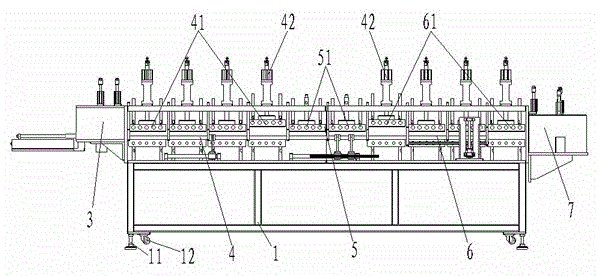

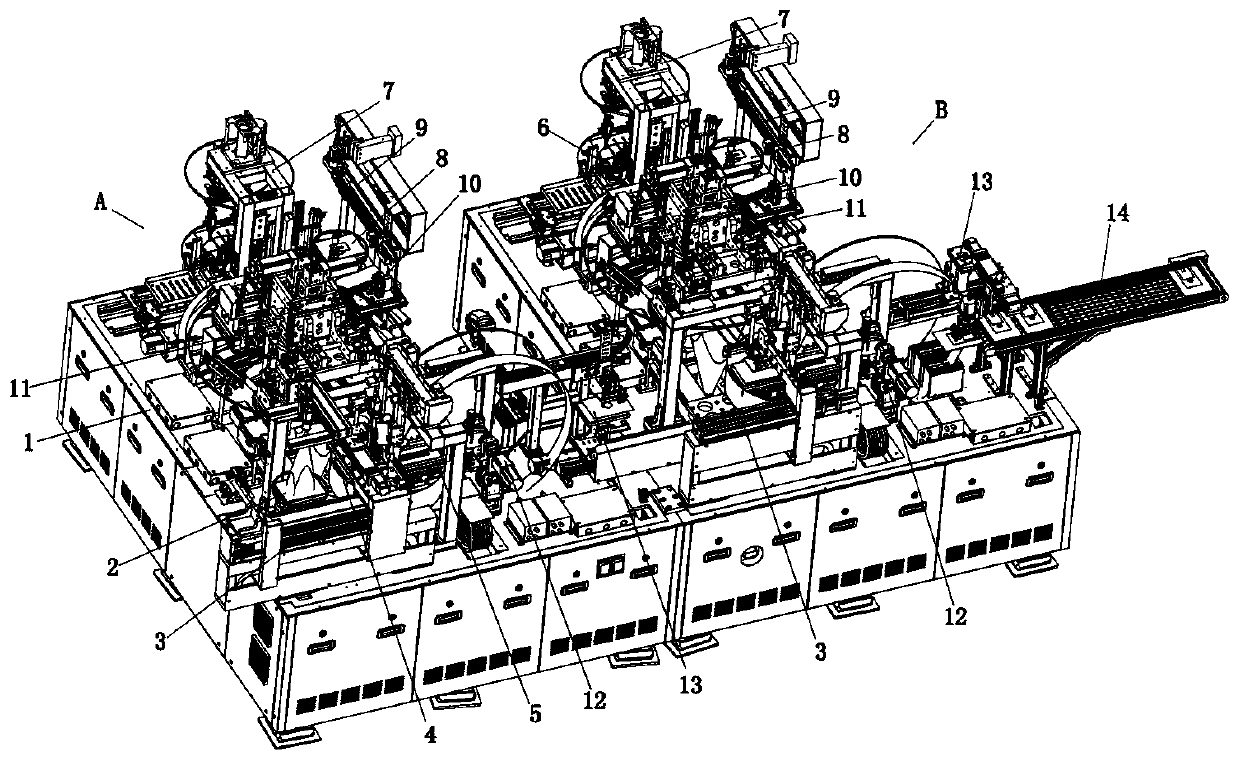

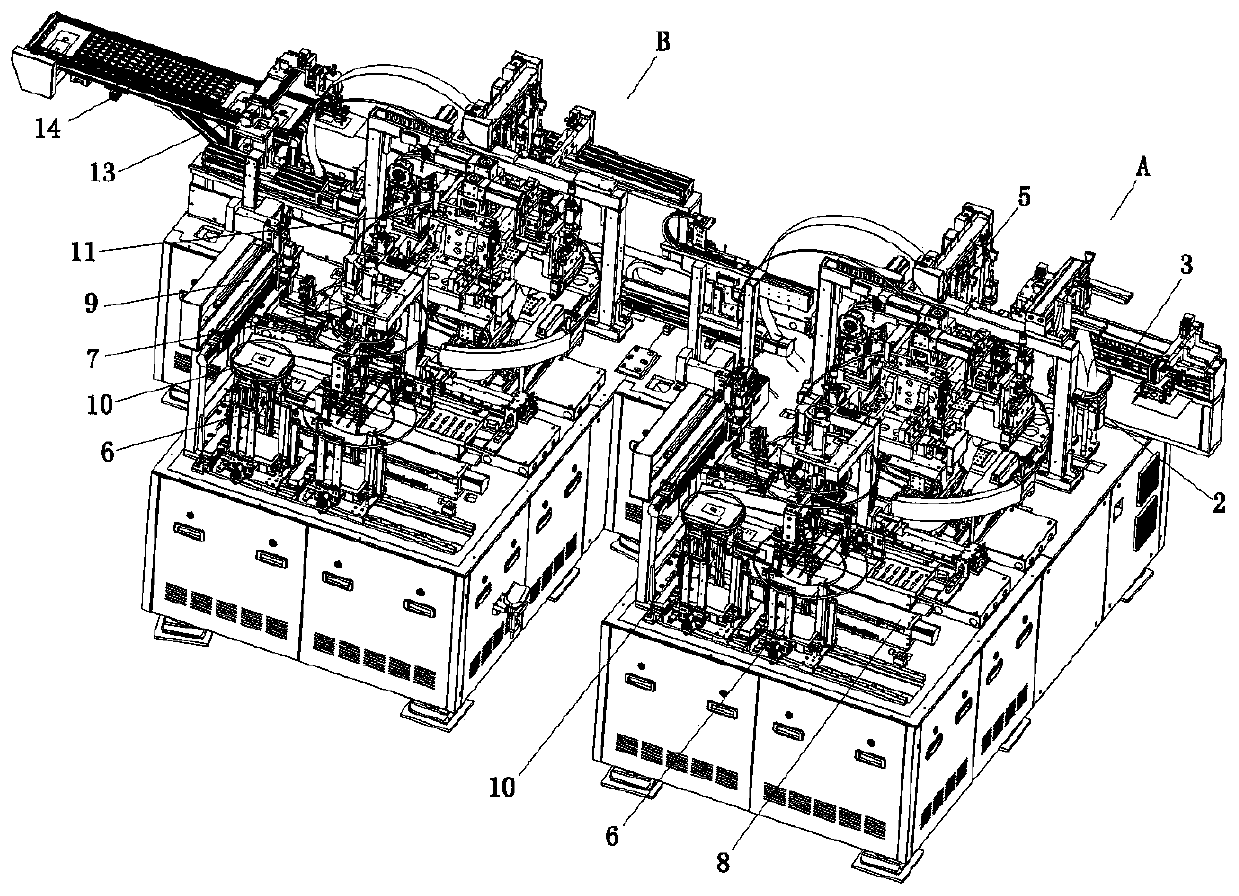

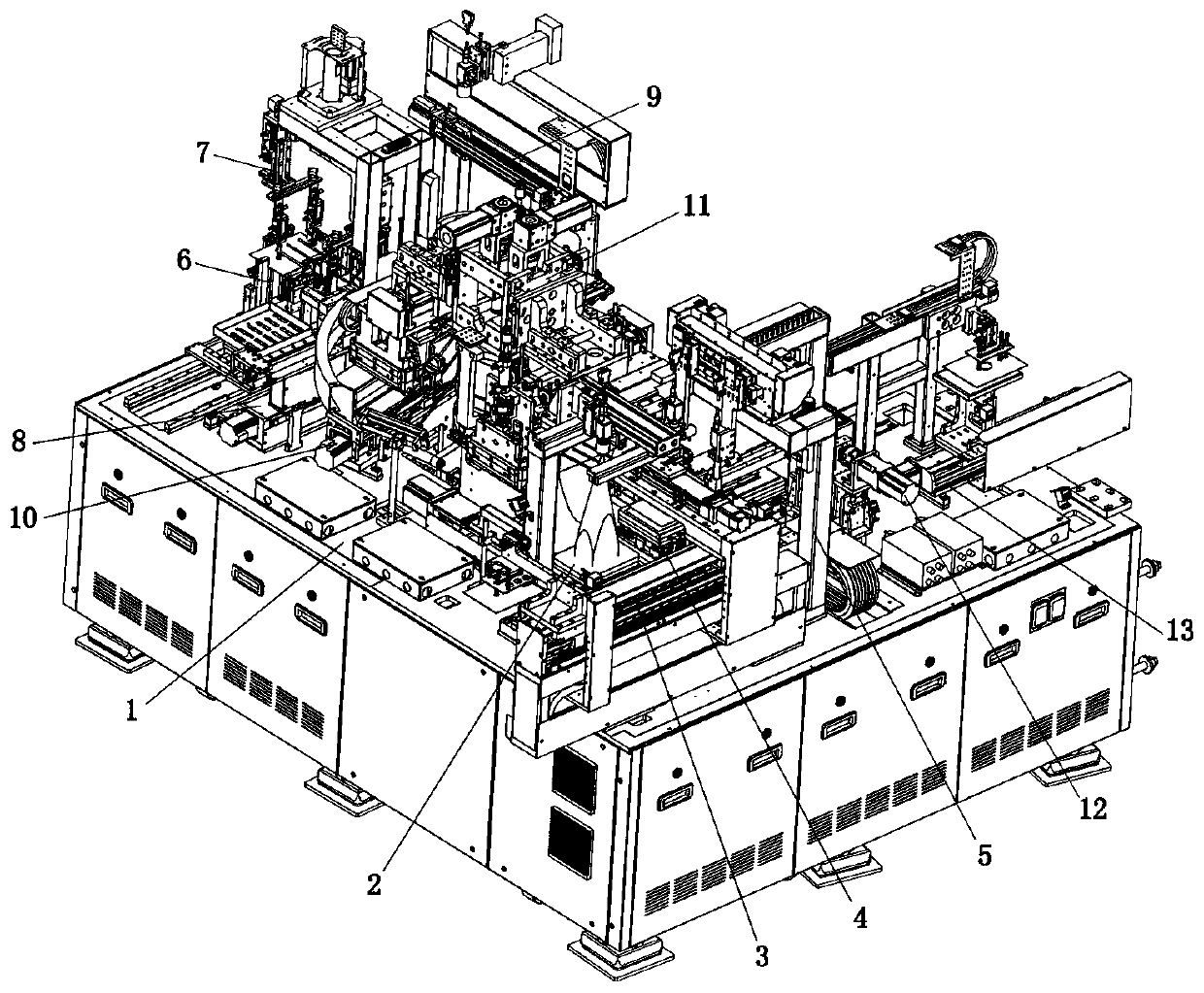

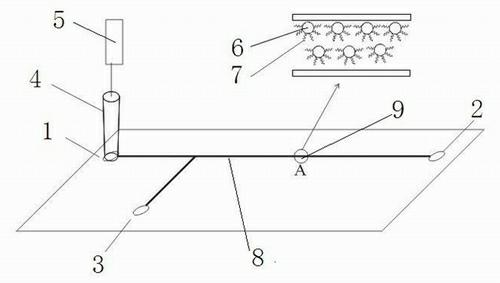

Full-automatic screen double-sided chip mounter and chip mounting technology thereof

PendingCN110174715ARealize automatic and efficient connectionReduce the presence of air bubblesNon-linear opticsOptical elementsEngineeringPolarizer

The invention discloses a full-automatic screen double-sided chip mounter and a chip mounting technology thereof. The full-automatic screen double-sided chip mounter comprises a first mounting part, aturnover mechanism, a second mounting part and a discharging belt which are arranged at intervals in sequence. After one side surface of a to-be-mounted glass sheet is subjected to chip mounting at the first mounting part, the glass sheet is moved to the turnover mechanism; after the glass sheet is turned over by the turnover mechanism, the other side surface of the glass sheet is subjected to chip mounting at the second mounting part; and the glass sheet is exported and discharged through the discharging belt. According to the chip mounter and the chip mounting technology, automatic and efficient connection of double-sided and single-sided mounting devices is effectively realized; automatic mounting of double polarizers is completed; the functions of alternate film tearing, alternating chip mounting, alternate discharging after chip mounting, and the like are realized; the material waiting time of each process gap is effectively utilized; the chip mounting time is shortened; the chipmounting productivity is effectively improved; the polarizers are adhered by adopting a flexible chip mounting adhesive tape; the attachment of the polarizers is completed by single-sided rolling attachment of a rolling attachment assembly; chip mounting air bubbles are effectively reduced; and the chip mounting quality is improved.

Owner:SHENZHEN ETMADE AUTOMATION EQUIP

DNA (deoxyribonucleic acid) biosensor chip based on nanometer magnetic bead technique and experimental method thereof

InactiveCN102174383AStrong specificityImprove stabilityBioreactor/fermenter combinationsBiological substance pretreatmentsElectrochemical detectorDead volume

On a conventional T-shaped glass chip, a permanent magnet is utilized to fix and decorate a nanometer magnetic bead of a DNA probe in a separation channel of a chip; the rapid, sensitive, high-specific, high-stability, low-cost separation detection on the DNA is realized by utilizing electric drive sampling and combining a laser induced fluorescence detector or an electrochemical detector, thus solving the defects that the time of separating and detecting the DNA by utilizing a microfluidic chip is long, the separation effect is poor, the sensitivity is low, the specific is poor and the stability is poor and the like; the interface manufacturing is avoided by an electric sampling manner; the influence of dead volume is removed; and the sample use amount is reduced in a narrower and uniform micro pipeline, and meanwhile the lower detection limit is ensured.

Owner:FUZHOU UNIV

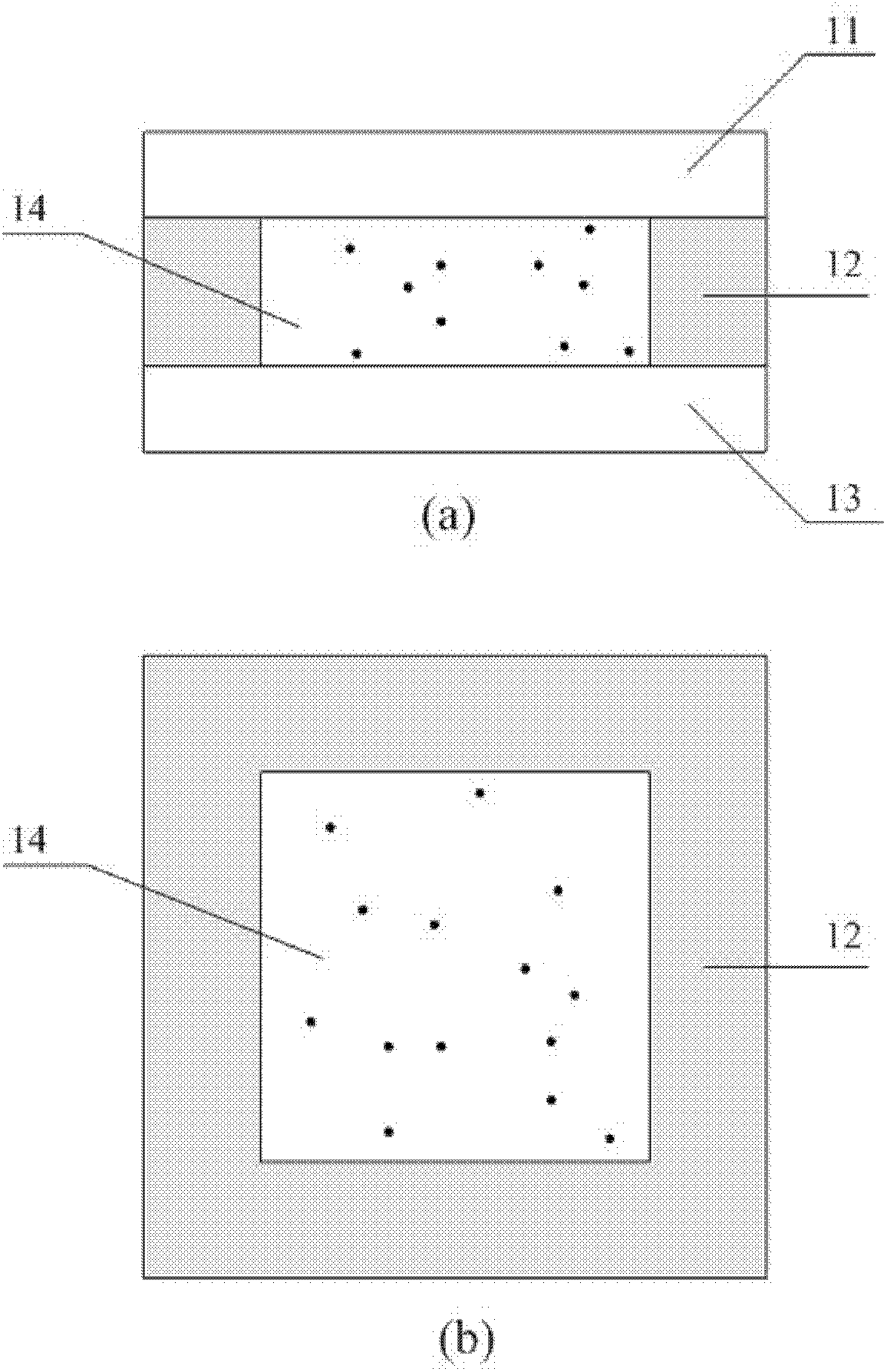

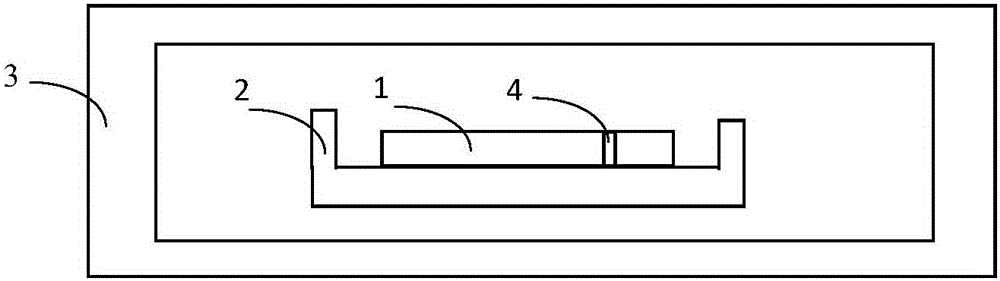

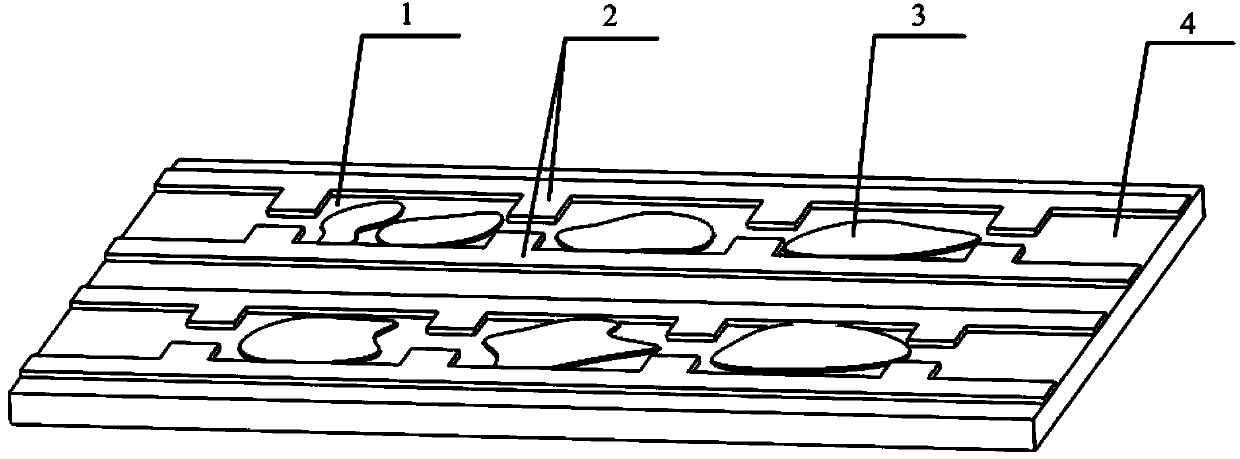

Glass chip for cultivating single cell array based on microfluidic patterning technology and preparation method thereof

InactiveCN103421691AEasy to operateGraphical structure is simpleTissue/virus culture apparatusCell adhesionAdhesion process

The invention discloses a glass chip for cultivating a single cell array based on microfluidic patterning technology, and a preparation method thereof, and belongs to the field of biological micro electro mechanical systems. The glass chip adopts the structure that a layer of PHEMA hydrogel pattern 2 is arranged on a glass base 4, and divides the glass base 4 into a plurality of rectangular cell growth zones 1 to generate the single cell array. The preparation process is that graphical PHEMA processing is performed on the surface of a glass sheet through a PDMS elastic stamp. The glass chip has the benefits that the stable surface chemical modification is adopted, so that hydrogel dressings capable of resisting cell adhesion is arranged on the surface of the glass in a graphical manner to form the cell graphical surface containing cell adhesion and resisting cell adhesion so as to cultivate the single cell array; the preparation process is simple and easy to operate; when the chip is applied to cell culture, the single cell growth array is obtained, and a new tool for studying basic cell biology is provided.

Owner:NORTHWESTERN POLYTECHNICAL UNIV