Interconnection test fixture and interconnection test method for silicon-based component

A test method and test fixture technology, which is applied in the direction of single semiconductor device testing, measuring device casing, etc., can solve the problems of no test fixture and test method, long production and debugging cycle, low test coverage, etc., to achieve application prospects and market potential Wide, improve the test pass rate, take into account the effect of efficiency and adequacy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

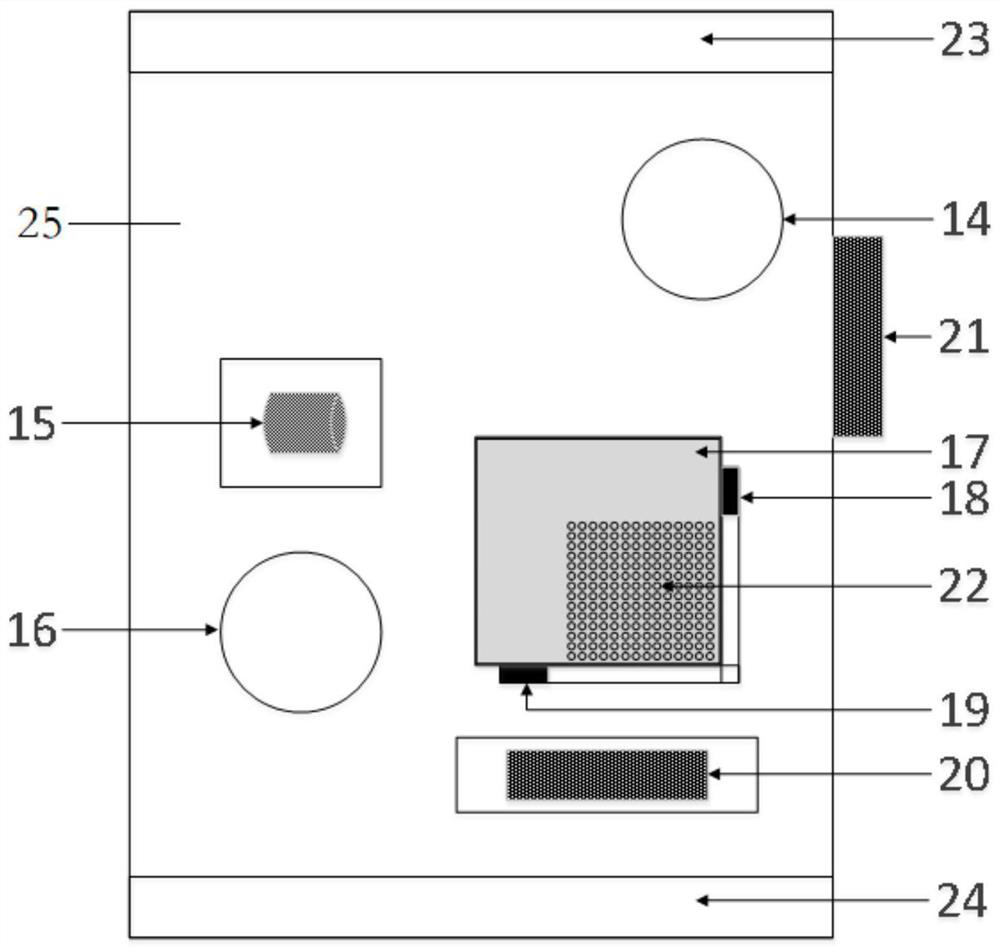

[0070] Taking the assembly test of a package on package and PoP of silicon-based components as an example, the interconnection test of silicon-based components is carried out from the aspects of DUT information, test process, test technology, test coverage and test time. illustrate.

[0071] DUT information

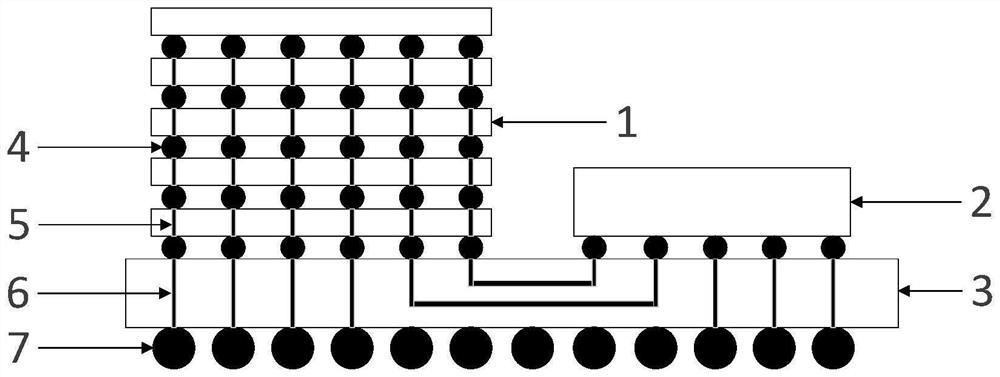

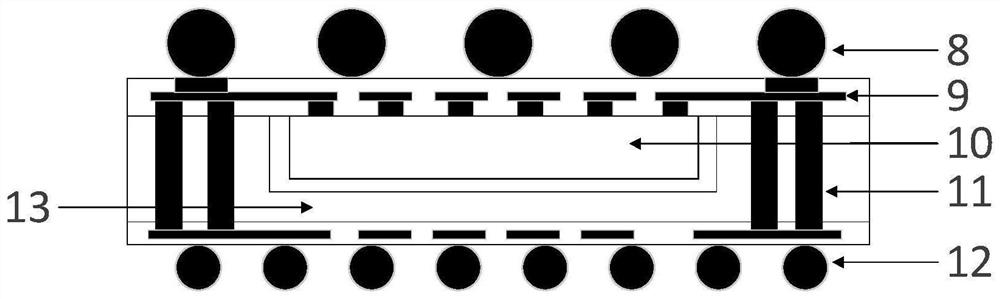

[0072] The DUT is a 3-layer silicon-based component PoP information processing micromodule, such as Figure 9 As shown, the uppermost layer is a silicon adapter board flip-chip 1 PowerPC processor die, the middle layer is a silicon adapter board flip-chip 3 DDR memory bare cores, and the bottom layer is a silicon adapter board flip-chip 2 Flash memory bare cores. core.

[0073] Table 1 DUT information

[0074]

[0075] It can be seen that the test surface requirements of PowerPC, DDR, Flash single-layer silicon-based components and DDR+Flash silicon-based components after 2-layer stacking are rear, double-sided, double-sided, and double-sided respectively; the heigh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More