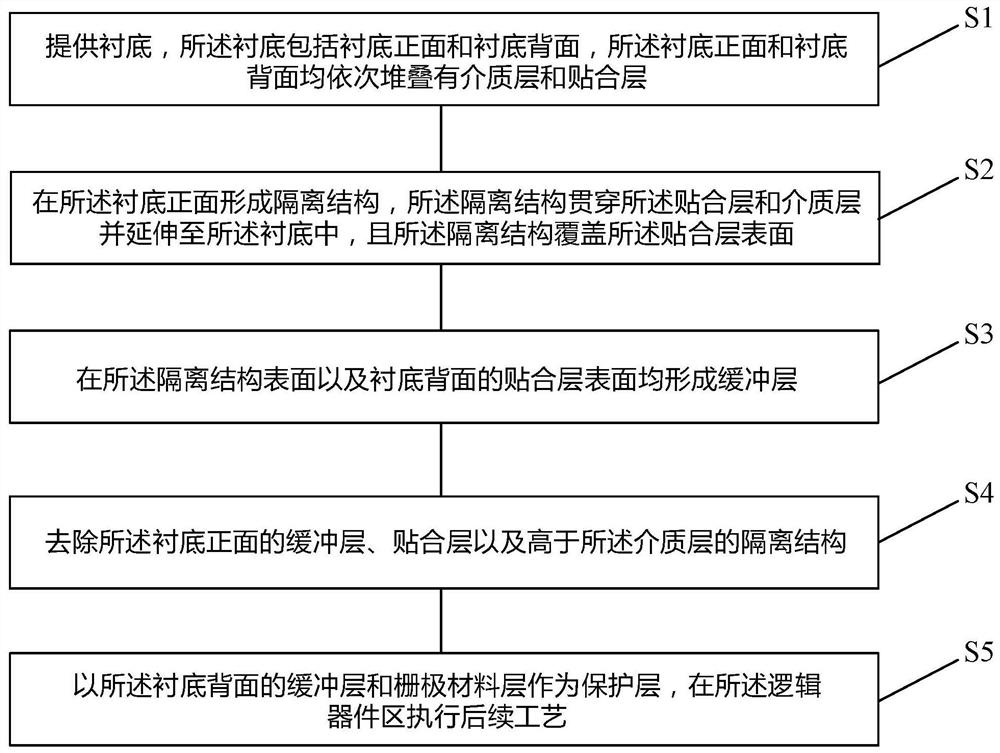

Semiconductor structure and forming method thereof

A semiconductor and isolation structure technology, applied in the field of semiconductor structure and its formation, can solve problems such as increased time and cost, difficulty in absorbing wafers, surface defects, etc., to improve yield rate, suitable for large-scale production, and ensure integrity The effect of sex and uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

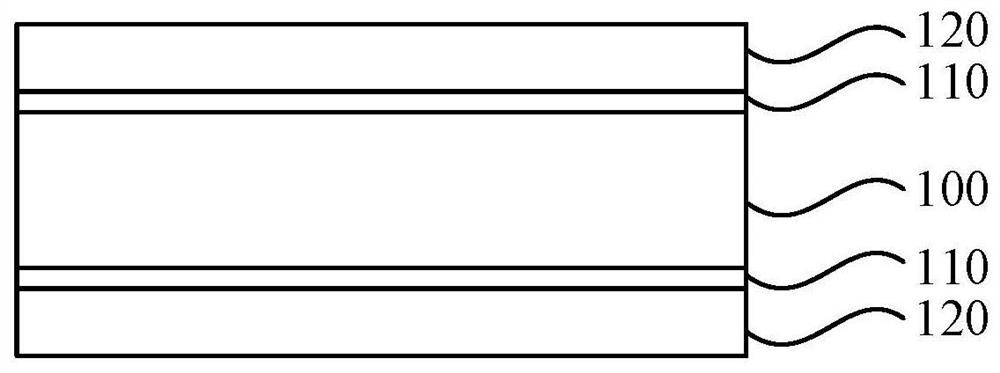

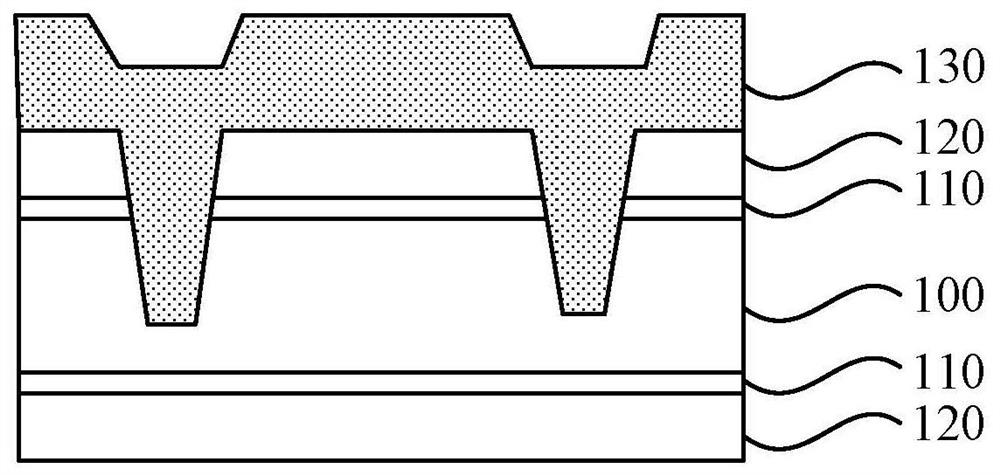

[0030] The following description provides specific application scenarios and requirements of the application, with the purpose of enabling those skilled in the art to manufacture and use the contents of the application. Various local modifications to the disclosed embodiments will be readily apparent to those skilled in the art, and the general principles defined herein may be applied to other embodiments and embodiments without departing from the spirit and scope of the application. application. Thus, the application is not limited to the embodiments shown, but is to be accorded the widest scope consistent with the claims.

[0031] The method for forming the semiconductor structure of the technical solution of the present application forms a bonding layer on the back of the substrate, and forms a buffer layer and a gate material layer on the surface of the bonding layer, so that the buffer layer and the gate material layer can be used in subsequent processes. Play a role in ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More