A Design Method of Digital Marker in Test Layout

A technology of digital marking and virtual pattern, applied in electrical digital data processing, computing, special data processing applications, etc., can solve the problem of weakening the photolithography, etching process window, reducing the overall uniformity of the layer pattern, and not distinguishing the key layers of the design, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

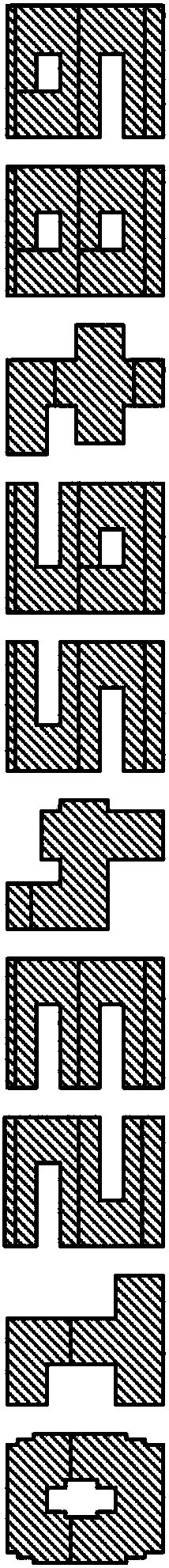

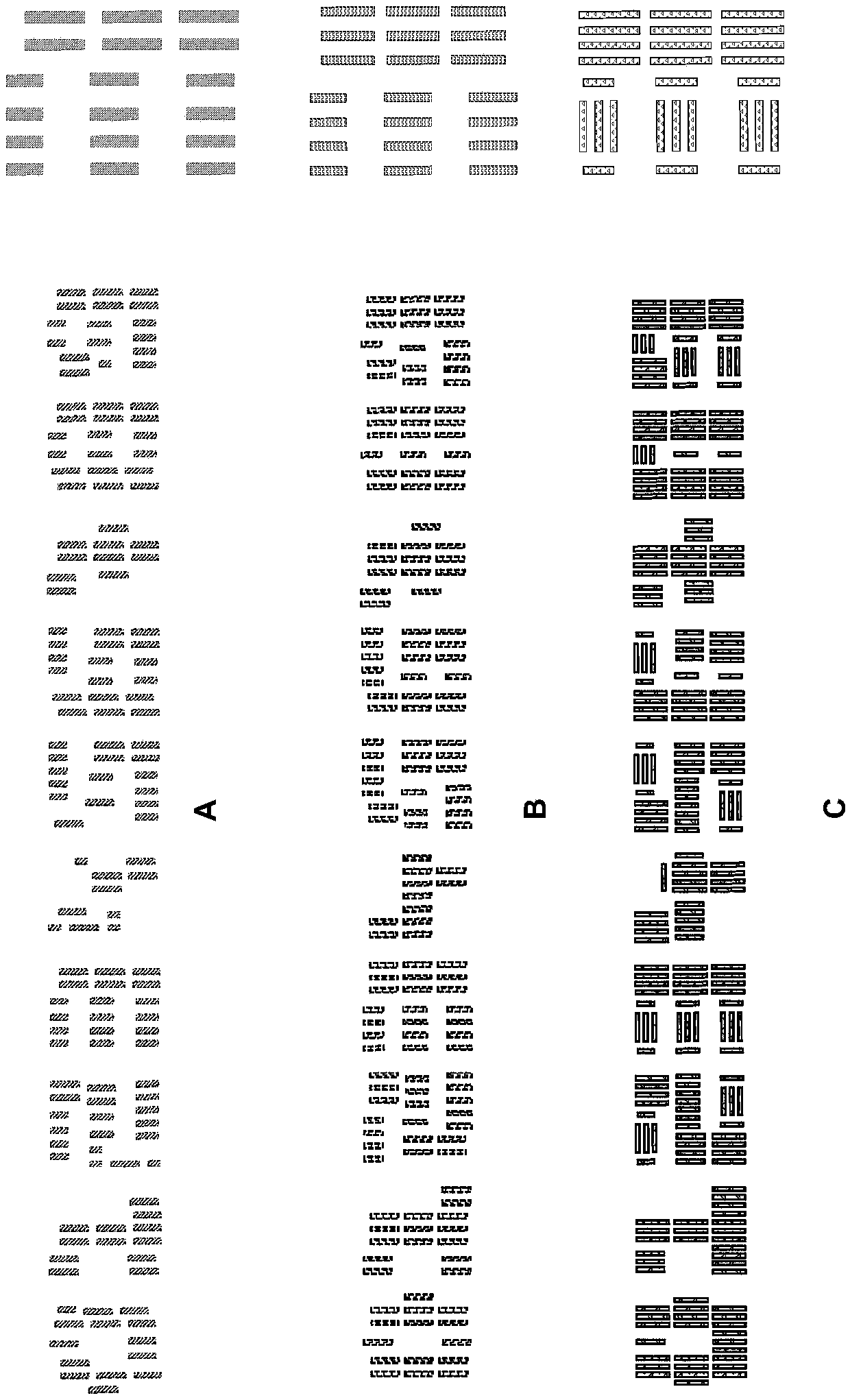

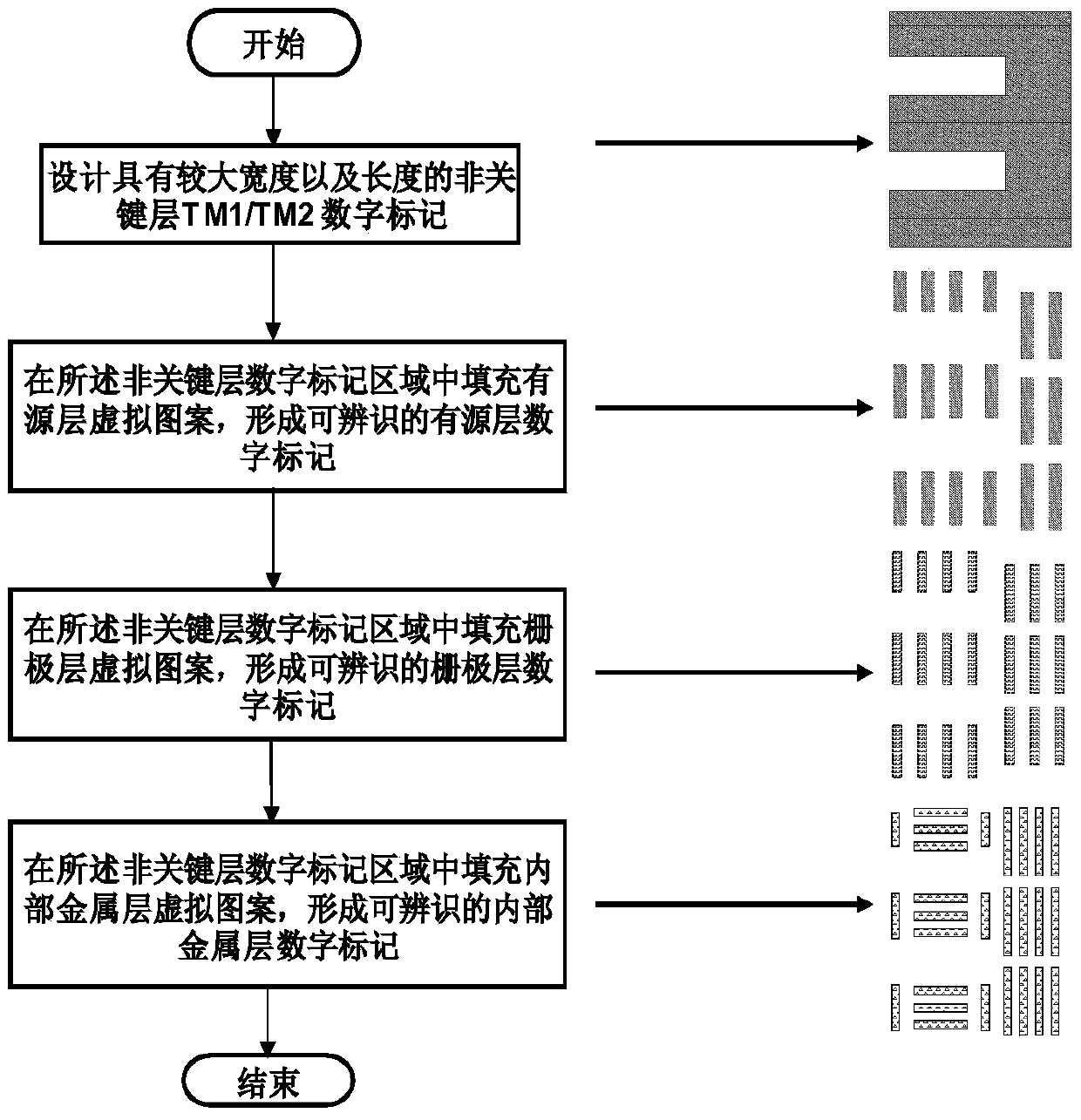

[0047] Attached below Figure 2-3 The method for forming the digital mark in this embodiment will be described in detail.

[0048] First, refer to figure 2 , in the present invention, in order to solve the problems caused by selecting a digital mark with a larger size on the key physical layer, a new method for forming a digital mark is provided, in which the non-critical physical layer (non-critical physical layers) and the key physical layer are designed differently, and digital marks with different key sizes are formed on different layers, so that the digital marks and the main pattern of the layer have a uniform key size.

[0049] For example in figure 2 Among them, digital marks with larger critical sizes are first formed in non-critical physical layers. The width and length of digital marks formed in non-critical physical layers are relatively large. Also in non-critical physical layers The standard circuit also has similar critical dimensions, so that a pattern wit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More