Full FIFO (first in, first out) circuit design method and universal test bench of method

A technology for circuit design and general verification, applied in computing, electrical digital data processing, special data processing applications, etc., can solve the problems of lack of a general integrated circuit chip verification platform, complex interface methods of integrated circuit chips, and lack of versatility. Achieve the effects of omitting duplication of labor, shortening the research and development cycle, and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

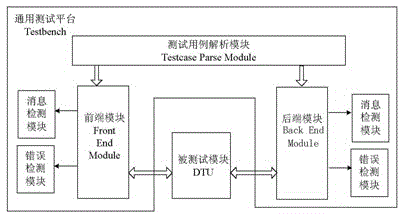

[0038] The detailed structure of the present invention, application principle, function and effect, refer to the appended Figure 1-7 , which will be described through the following embodiments.

[0039] The present invention realizes the object of the invention through following two aspects:

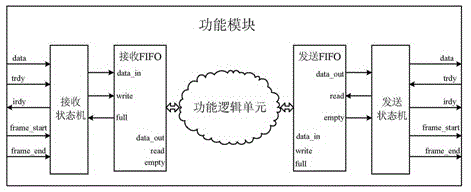

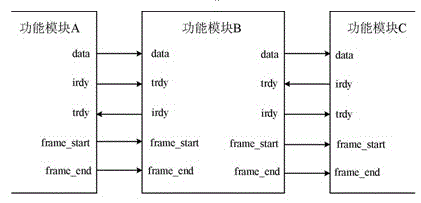

[0040]The first is the full FIFO circuit design: the design idea is realized through a unified architecture and a standard interface. This design is mainly used in FPGA or ASIC chip circuit design for step-by-step processing of digital signals. Specifically, the signal is sent from the input terminal to the functional module, and after a series of processing by the functional module, it is sent to the next step through the output terminal. function modules. For a functional module, the architecture of the full FIFO circuit design can be found in figure 1 The shown circuit realizes the block diagram, and the input end is made up of receiving state machine and receiving FIFO, and recei...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More