In cell touch panel and display device

A built-in touch screen, in-area technology, applied in the direction of instrument, electrical digital data processing, data processing input/output process, etc. Effects of touch signal-to-noise ratio and touch sensitivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

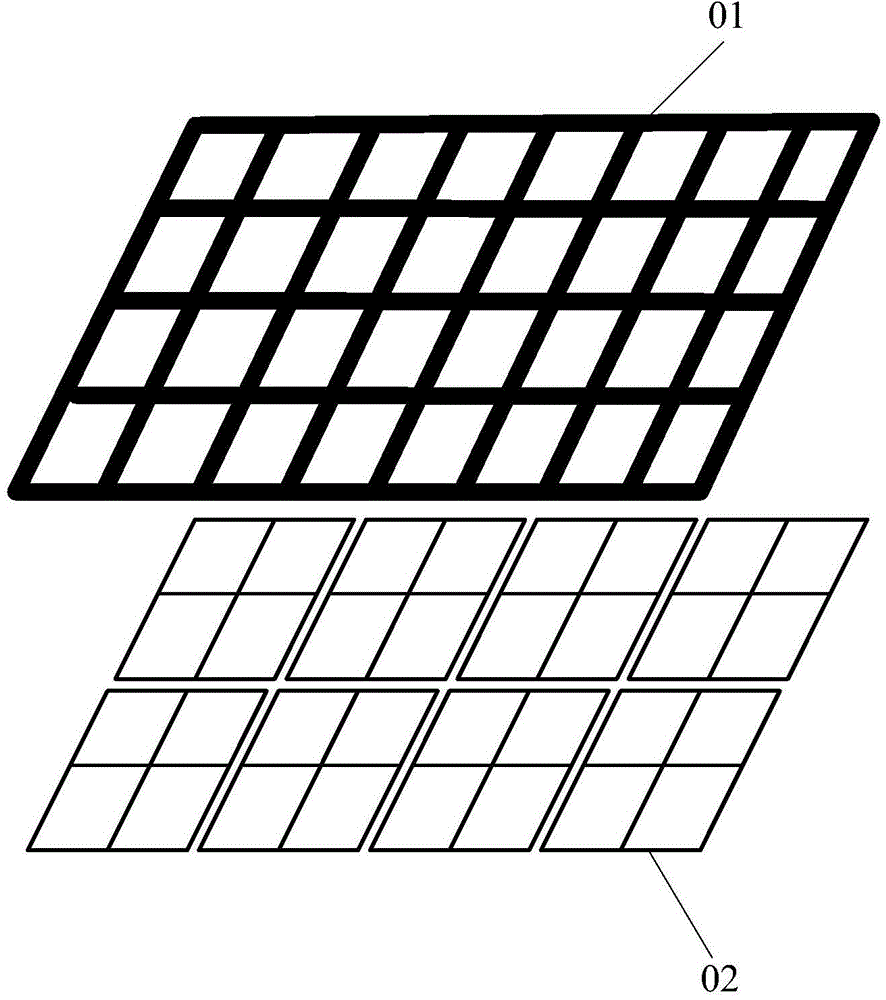

Embodiment 1

[0109] Such as Figure 6a As shown, the in-cell touch screen includes a plurality of sub-pixels 05 ( Figure 6a The specific structure of the sub-pixels is not shown in the figure), the two gate lines gate between the sub-pixels 05 in adjacent rows, with each two adjacent columns of sub-pixels 05 as a pixel group, share a gate line located between the two columns of sub-pixels The data line data between pixels 05. The common electrode composed of the self-capacitance electrode 02 connects the corresponding self-capacitance electrode 02 to the wire 06 of the driving circuit, wherein the wire 06 and the data line data are mutually insulated, arranged in the same layer and in parallel, and each wire 06 is connected to the corresponding wire through a via hole. The self-capacitance electrodes 02 are connected and arranged in gaps between adjacent pixel groups. It also includes: a plurality of segments of fourth connecting wires 07 located in the area corresponding to each wire 0...

Embodiment 2

[0113] Such as Figure 7a As shown, the in-cell touch screen includes a plurality of sub-pixels 05 ( Figure 7a The specific structure of the sub-pixel is not shown in the figure), the two data lines data between the sub-pixels 05 in adjacent columns, each two adjacent rows of sub-pixels 05 as a pixel group, share a data line located in the two rows of sub-pixels The grid line gate between pixel 05. The common electrode composed of the self-capacitance electrode 02 connects the corresponding self-capacitance electrode 02 to the wire 06 of the drive circuit, wherein the wire 06 is insulated from the gate line gate, arranged in the same layer and in parallel, and each wire 06 passes through the via hole and the corresponding wire 06 The self-capacitance electrodes 02 are connected and arranged in gaps between adjacent pixel groups. It also includes: multiple segments of fourth connecting wires 07 located in the area corresponding to each wire 06 and electrically connected to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More