Task scheduling method in heterogeneous multi-core architecture

A task scheduling and heterogeneous multi-core technology, which is applied in the directions of multi-program device, program startup/switching, resource allocation, etc., can solve the problem of low technology maturity, not widely used, non-master-slave heterogeneous multi-core system implementation Complicated problems, to achieve the effect of good scalability, low call overhead, and meet real-time scheduling requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will now be described in further detail with reference to the accompanying drawings and preferred embodiments. These drawings are all simplified schematic diagrams, and only illustrate the basic structure of the present invention in a schematic manner, so they only show the structures related to the present invention.

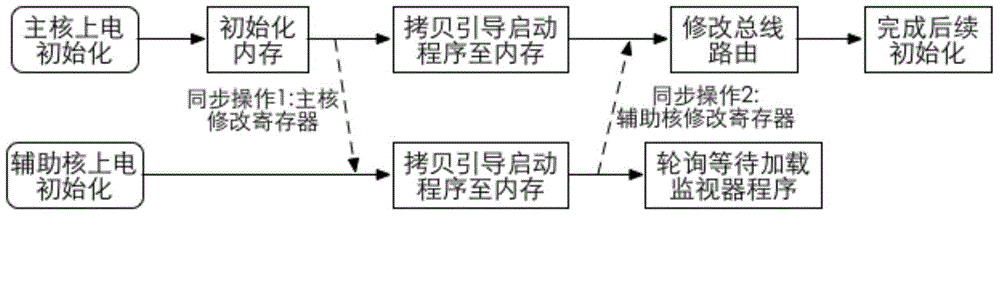

[0023] figure 1 The flow chart of heterogeneous multi-core booting is shown: after the system chip is powered on, each processor core will jump to the booting address to start instruction fetch execution.

[0024] Since self-copying is required in the boot process of the auxiliary core, a memory access operation will occur, and this operation can only be performed after the main core completes the memory initialization. Therefore, the main core and the auxiliary core cannot independently complete their respective boot-up processes, and an interactive mechanism needs to be established to ensure the smooth progress of the following o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More