Heterogeneous multi-core SoC design evaluation system

An evaluation system, heterogeneous multi-core technology, applied in computing, special data processing applications, instruments, etc., can solve problems such as prone to errors, low work efficiency, complicated technology, software and processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

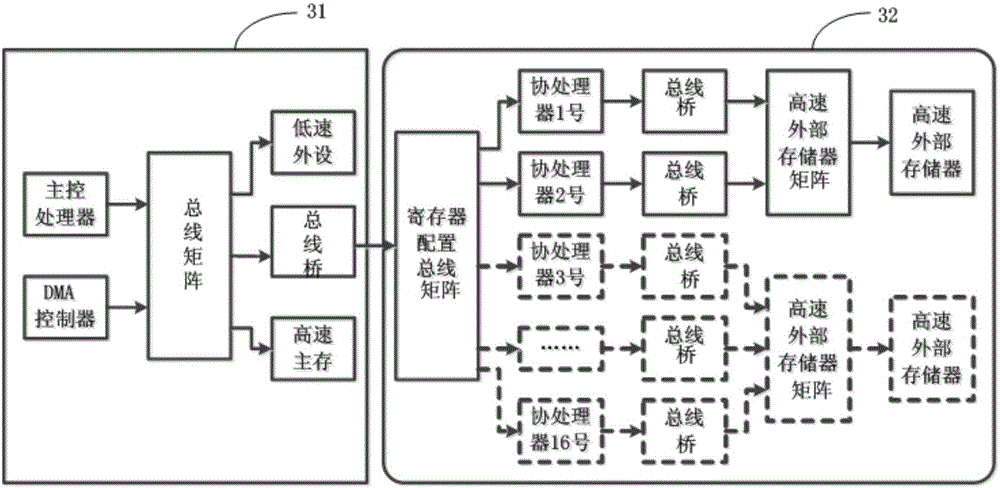

[0013] The heterogeneous multi-core SoC design evaluation system provided by the embodiment of the present invention will be described in detail below with reference to the accompanying drawings.

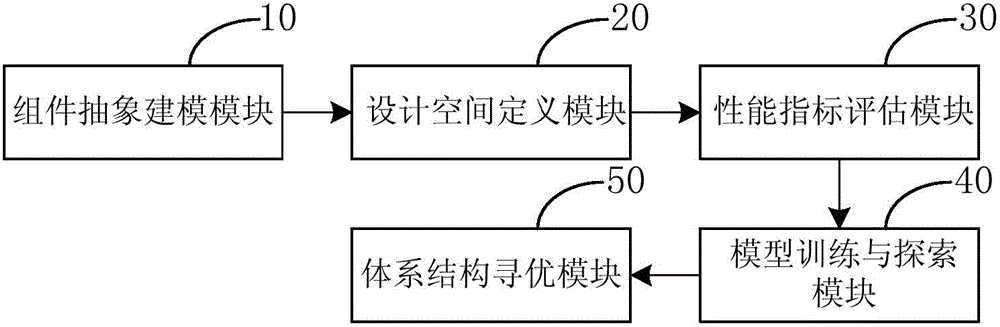

[0014] figure 1 It is a schematic diagram of a heterogeneous multi-core SoC design evaluation system provided by an embodiment of the present invention.

[0015] refer to figure 1 , the system includes a component abstract modeling module 10 , a design space definition module 20 , a performance index evaluation module 30 , a model training and exploration module 40 and an architecture optimization module 50 .

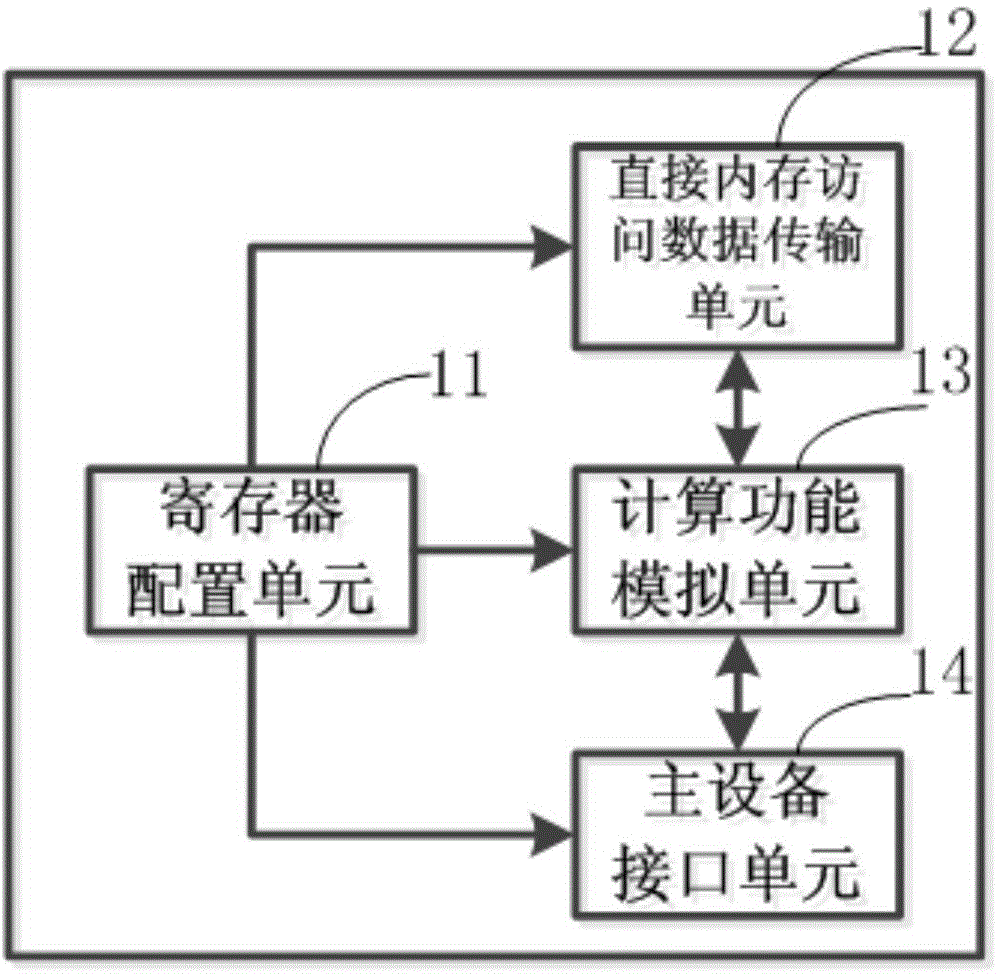

[0016] The component abstract modeling module 10 is used for performing abstract modeling on the master-slave components of the bus, wherein the master-slave components include functional components such as coprocessors, internal and external storage units, and high-speed IOs.

[0017] Here, the principle of the component abstract modeling module 10 is to focus on the conne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More