EEPROM memory cell gate control signal generating circuit

A technology for controlling signals and memory cells, applied in information storage, static memory, read-only memory, etc., can solve the problems of high voltage, drains cannot be directly connected together, etc., to save costs and simplify circuits.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

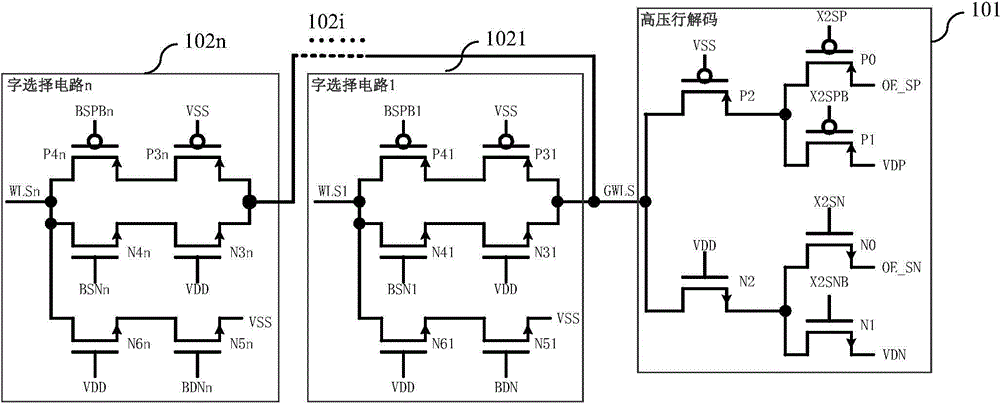

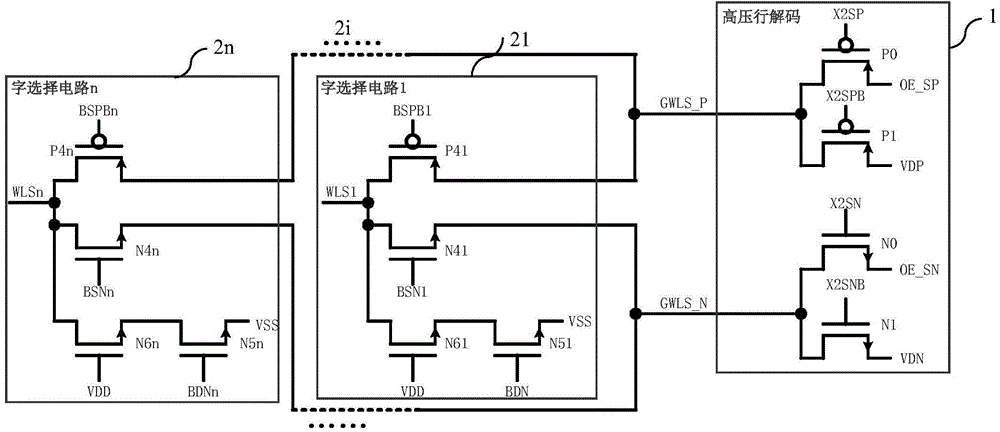

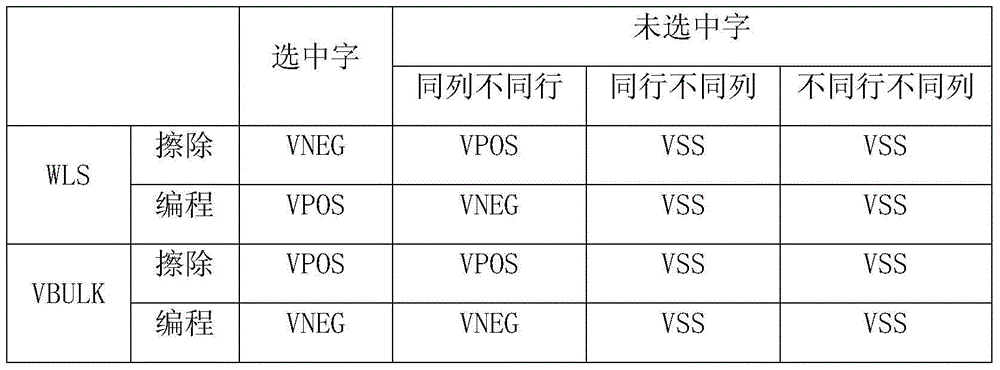

[0033] Such as figure 2 Shown is the circuit diagram for generating the gate control signal of the EEPROM storage unit according to the embodiment of the present invention. The EEPROM storage unit gate control signal generation circuit in the embodiment of the present invention includes:

[0034] High-voltage line decoding circuit 1 and multiple word selection circuits, such as word selection circuit 1 to word selection circuit n are marked with 21 to 2n respectively, wherein 2i marks word selection circuit i, and i represents any value in 1 to n.

[0035] The high-voltage row decoding circuit 1 includes a first partial row decoding circuit composed of a first PMOS transistor P0 and a second PMOS transistor P1, and a second partial row decoding circuit composed of a first NMOS transistor N0 and a second NMOS transistor N1.

[0036]The drain of the first PMOS transistor P0 is connected to the drain of the second PMOS transistor P1 and outputs the first total word line voltage...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More