Early-stage detecting system and method for silicon chip electrical test

A silicon chip and electrical technology, applied in the field of early detection system of silicon chip electrical test, can solve the problem that WAT test data analysis cannot detect electrical performance in time, and solve the untimely nature of manual inspection, simple structure and steps , the effect of saving time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

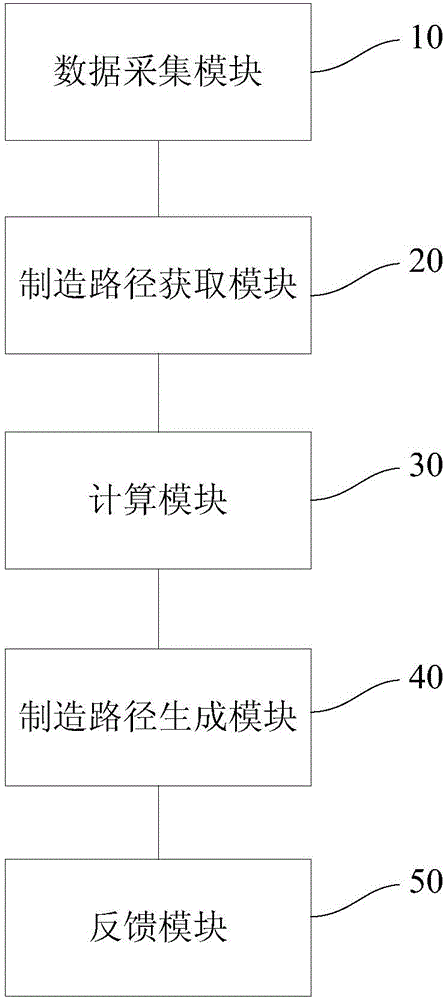

[0033] like figure 1 and image 3 As shown, this embodiment provides an early detection system for electrical testing of silicon wafers, including:

[0034] The data collection module 10 is used to collect silicon wafer electrical test data, and determine normal silicon wafers and abnormal silicon wafers based on the test data;

[0035] The manufacturing path acquisition module 20 is used to acquire the manufacturing paths of each of the normal silicon wafers and each of the abnormal silicon wafers in the process machine matrix;

[0036] The calculation module 30 is used to calculate the normal silicon wafer pass rate and abnormal silicon wafer pass rate of each process machine in the process machine matrix according to the manufacturing path;

[0037]The manufacturing path generation module 40 is used for generating a suitable manufacturing path for silicon wafers according to the normal silicon wafer throughput rate and the abnormal silicon wafer throughput rate.

[0038]...

Embodiment 2

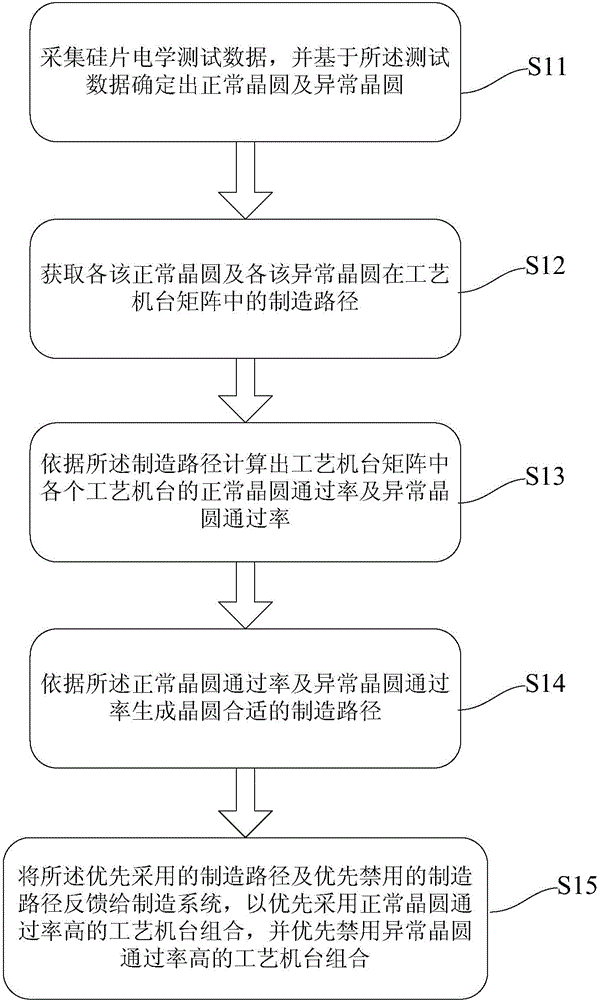

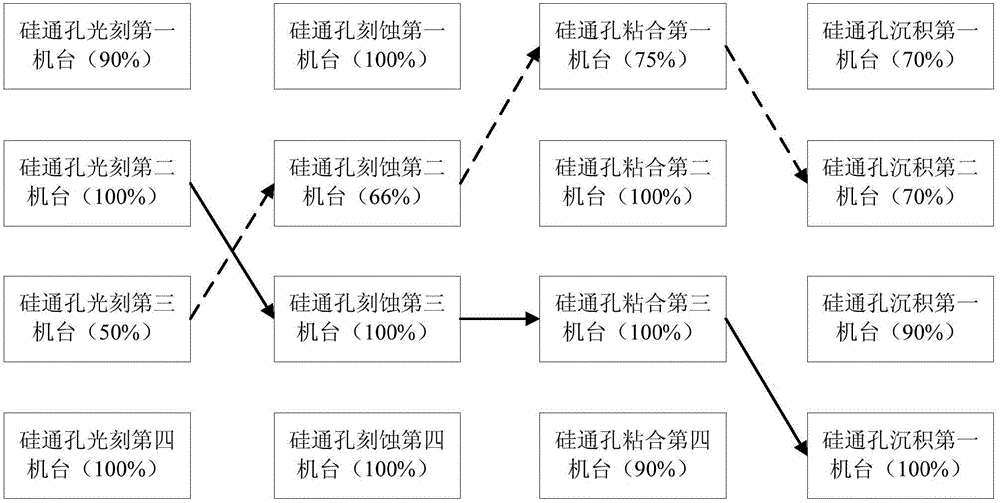

[0047] like figure 2 and image 3 As shown, this embodiment provides an early detection method for electrical testing of silicon wafers, including steps:

[0048] like figure 2 As shown, step 1) S11 is first performed to collect electrical test data of silicon wafers, and determine normal silicon wafers and abnormal silicon wafers based on the test data.

[0049] As an example, the silicon wafer electrical test data uses some special parameter test structures to replace products for current, voltage and capacitance tests to determine the silicon wafer electrical performance. The special parameter test structures include transistors, various line widths, Resistivity structure, capacitance structure, contact hole, via chain, meander structure, frame-in-frame structure, can be used to test resistance, voltage, capacitance, current and open circuit or short circuit test. .

[0050] As an example, this step uses a comparison method based on the test data to determine normal s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More