Fully differential increment sampling method of successive approximation type analog-digital converter

An analog-to-digital converter, successive approximation technology, applied in analog-to-digital conversion, code conversion, instruments, etc., can solve the problem of SARADC high-bit conversion redundancy and other problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

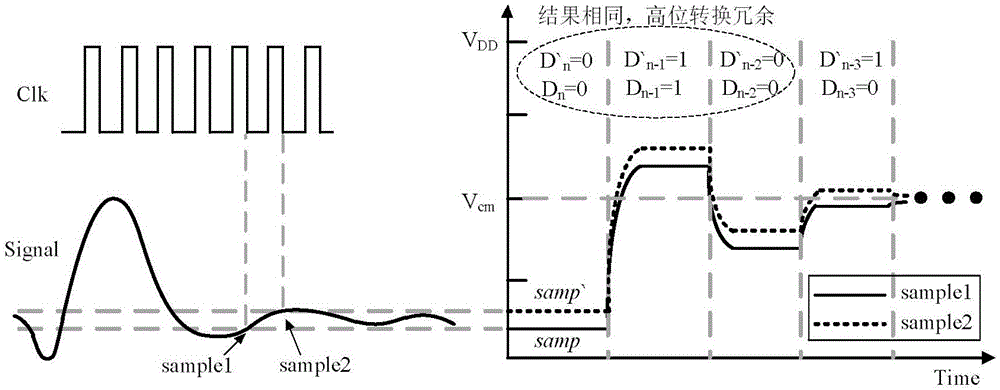

[0051] The invention provides a full differential incremental sampling method of a successive approximation analog-to-digital converter, which shields high-bit redundant conversion by judging the size of the sampled incremental value, and optimizes the DAC capacitance of the SAR ADC when the input signal variation range is small Switching power consumption enables low power consumption design.

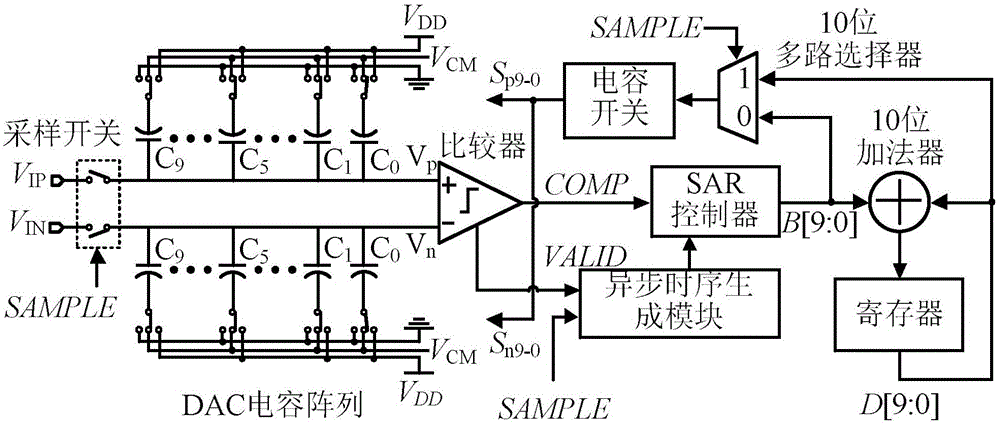

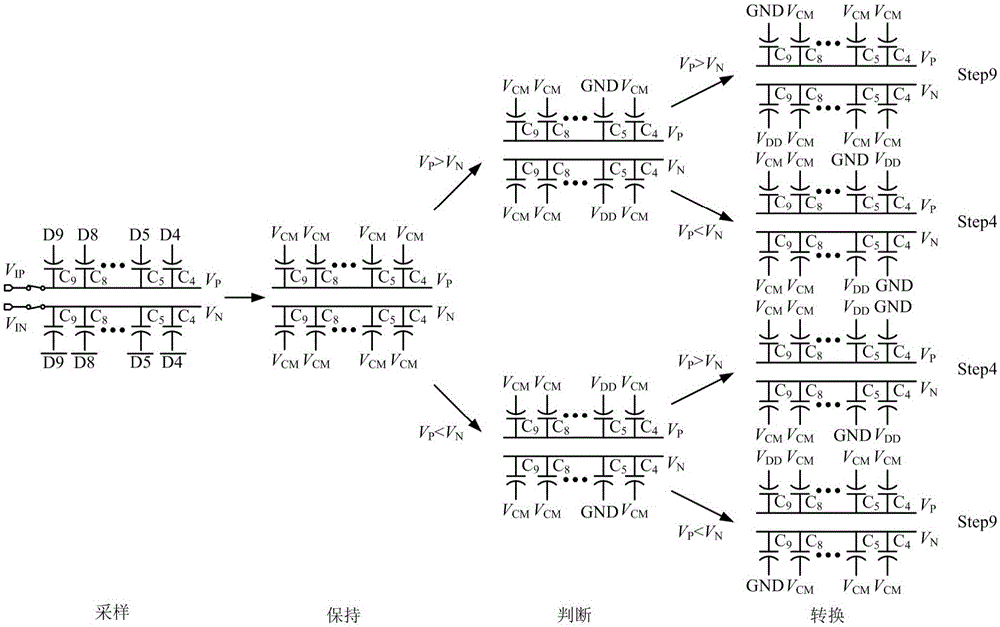

[0052] The overall circuit of the SAR ADC designed by the present invention is as follows figure 2 shown. The circuit mainly includes sampling switch, DAC capacitor array, capacitor switch, comparator, SAR controller, asynchronous timing generation module, 10-bit adder, 10-bit multiplexer 8 and register 9. The work of SAR ADC includes three phases, which are sampling phase, holding phase and conversion phase.

[0053] The DAC capacitor array includes a P-type capacitor array and an N-type capacitor array, and each capacitor array includes 10 capacitors C0-C9; the upper plates of all...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More