Heterogeneous platform based multi-parallel error detection system framework

A technology of error detection and architecture, applied in the fields of instruments, electrical digital data processing, computers, etc., can solve the problems of idle computing units, unreasonable use of shared resources, etc., and achieve the effect of small running overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

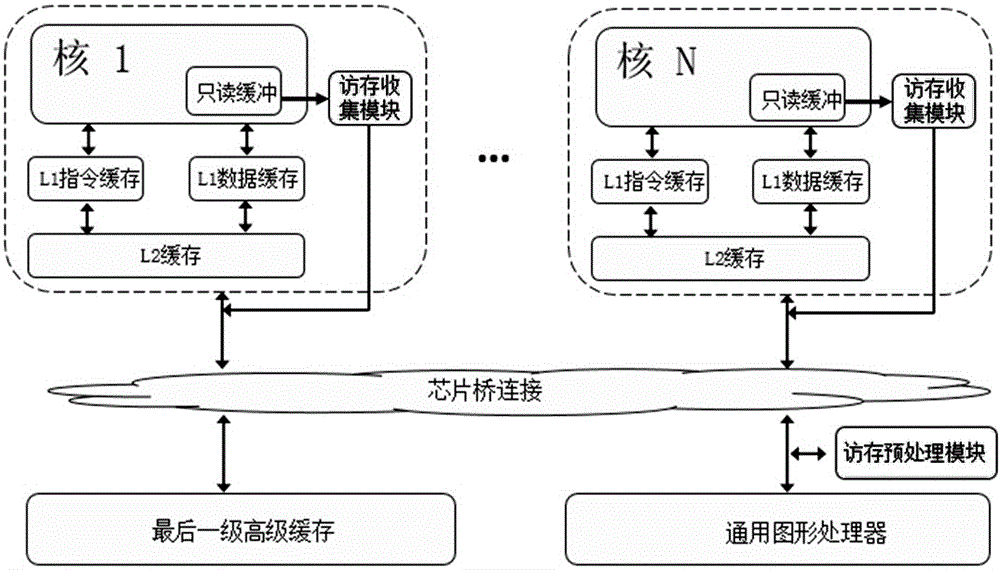

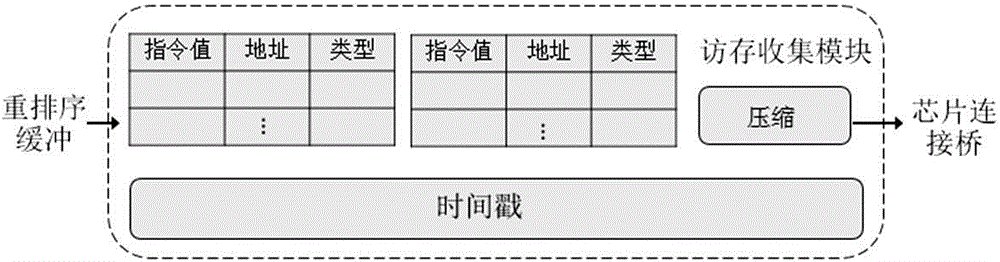

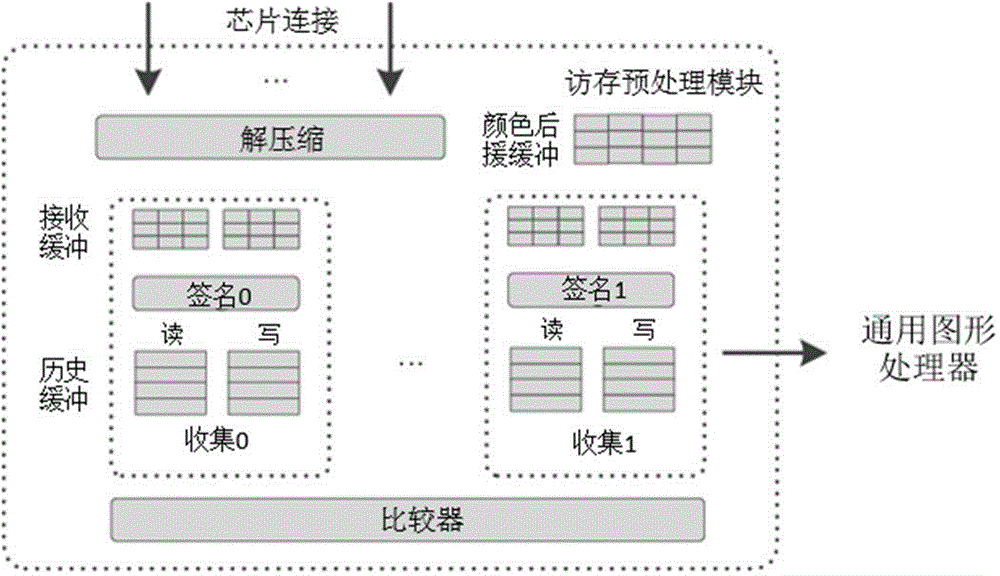

[0021] The technology in the present invention will be described in detail below in conjunction with the description of the drawings and the pseudo code of the algorithm. The invention mainly utilizes the powerful parallel computing ability and programmability of the graphic processor in the heterogeneous platform. Collect memory access records on the general processor side, send the records to the graphics processor side through the on-chip interconnection bus, and finally perform error detection on the graphics processor side. On this basis, the present invention utilizes: (1) Utilize Bloom filter to filter secure memory access records; (2) Avoid shared memory access from being replaced; (3) "Last write" identification simplifies detection work, these three optimization strategies Improve detection speed and detection accuracy.

[0022] 1. Implementation of heterogeneous platforms required for multiple parallel error detection

[0023] First, in order to improve universa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More