SAR ADC adopting low resolution DAC capacitor array and application method thereof

A capacitor array and low-resolution technology, applied in the field of SARADC, can solve the problem of increasing the complexity of the circuit layout required for capacitor array matching, and achieve the effects of shortening conversion time, avoiding conversion time, and stable and reliable circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Further describe the technical scheme of the present invention in detail below in conjunction with accompanying drawing:

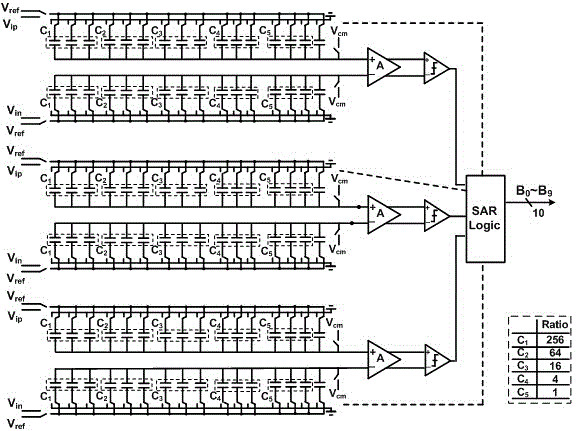

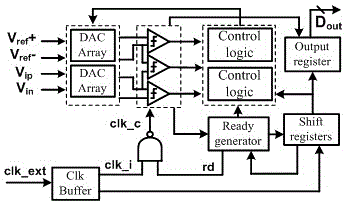

[0041] This embodiment is a 2-bit / period SARADC structure, in which 2-bit interpolation and 8-bit capacitor digital-to-analog array are used. Therefore, the ADC can obtain 10-bit resolution, which realizes the use of low-resolution DAC capacitors. array implements a high-resolution SARADC.

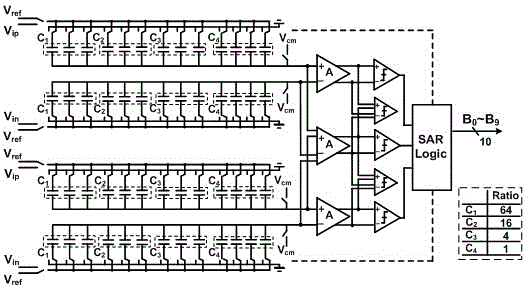

[0042] Such as figure 2 As shown, this embodiment is composed of two 8-bit DAC arrays, three preamplifiers, five comparators and SAR control logic. An interpolation structure is adopted between the two DAC arrays, and one DAC array can be reduced compared with the traditional 2-bit / period SARADC structure. figure 2 The ratio of C1:C2:C3:C4 in the binary DAC array is 64:16:4:1, and a capacitive DAC array consists of 256 unit capacitors. During sampling, the inputs of the three preamplifiers are all connected to a common-mode voltage, and the bottom plate of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More