HDLC protocol controller based on FPGA chip

A protocol controller and controller technology, applied in the direction of data exchange through path configuration, electrical components, transmission systems, etc., can solve the problems of poor flexibility and limited storage capacity, and achieve low design and manufacturing costs, low power consumption, The effect of ensuring reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

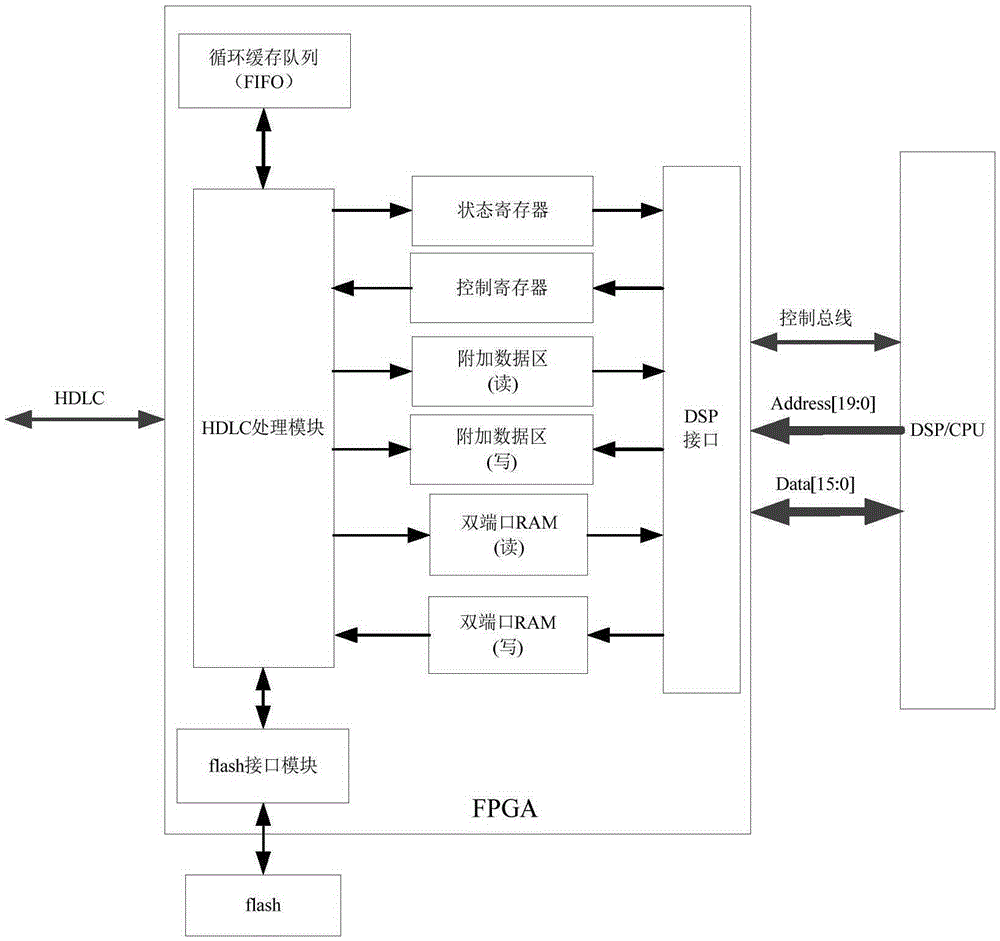

[0018] figure 1 It is a system block diagram of a preferred embodiment of the present invention, wherein the main functions of each module are as follows:

[0019] (1) HDLC processing module

[0020] This module is mainly responsible for extracting the content of the frame information field from the received HDLC frame or encapsulating the frame information into HDLC frame format and sending it;

[0021] (2) DSP interface module

[0022] This module is responsible for the conversion of DSP bus timing and controller internal RAM and register read and write timing.

[0023] (3) Flash interface module

[0024] This module is responsible for the conversion of Flash read and write timing and frame processing module to Flash operation timing.

[0025] (4) Dual-port RAM (read, write)

[0026] The dual-port RAM includes RAM (read) and RAM (write). RAM (read) is responsible for temporarily storing the frame information (info) received by the HDLC processing module from the master ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More