ROM memory cell, storage array, memory and reading method

A technology of storage unit and storage array, which is applied in the fields of memory and readout, storage array, and ROM storage unit, can solve the problems of inability to further reduce the memory chip area and low storage density, and achieve easy implementation, increase storage density, and circuit simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] In order to make the purpose, features and effects of the present invention more obvious and understandable, the specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0058] Many specific details are set forth in the following description to facilitate a full understanding of the present invention, but the present invention can also be implemented in other ways than described here, so the present invention is not limited by the specific embodiments disclosed below.

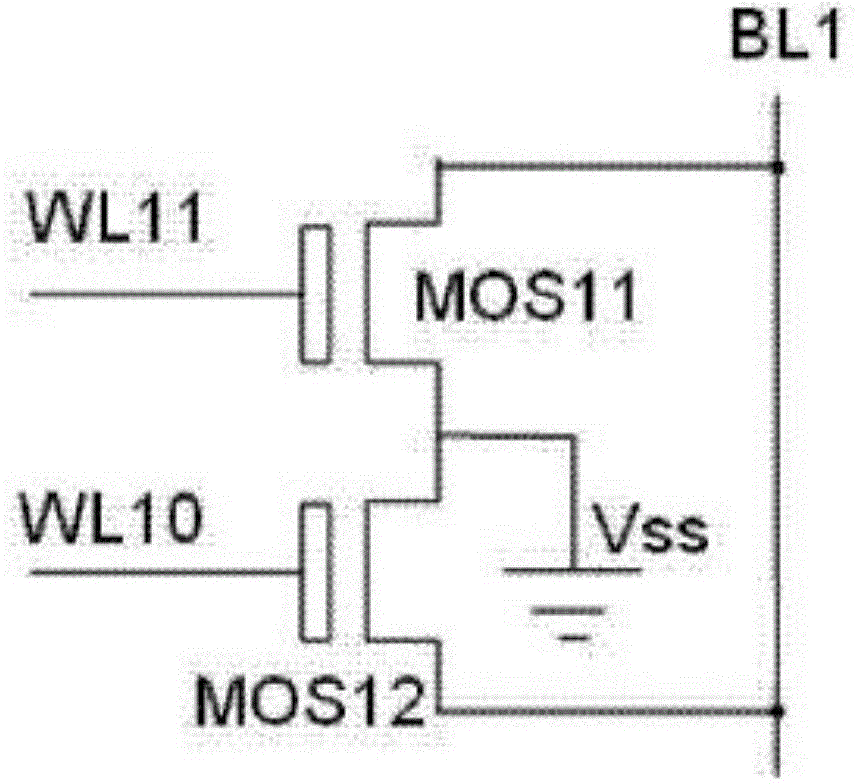

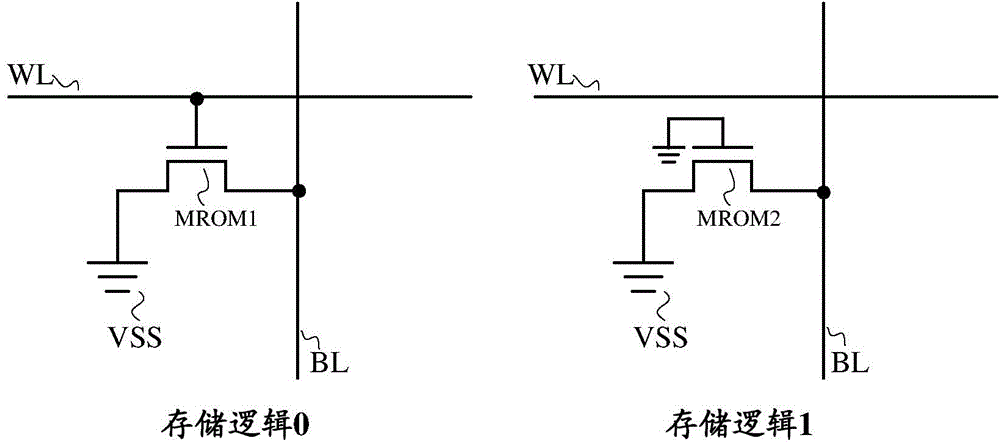

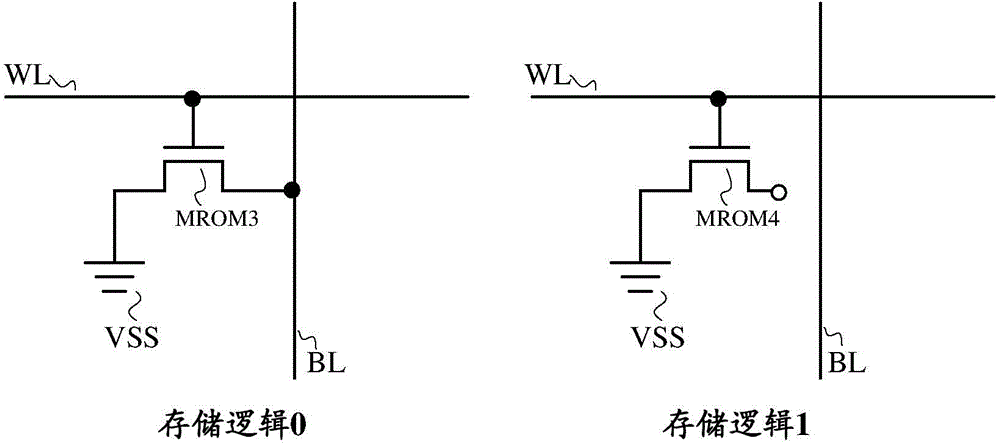

[0059] With reference to the ROM storage unit in the prior art, its constituent unit is a MOS transistor, and the channel control capability of this MOS transistor is single, therefore, as figure 2 or image 3 The memory cells shown, whether word line programming or bit line programming, can only store logic states by turning on and off MOS transistors, so the amount of information stored per unit is limited, and the chip...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com