Semiconductor structures and methods of forming them

A technology of semiconductor and nanostructure, applied in semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve problems such as short channel effect, leakage current power consumption increase, chip integration limit, etc., and achieve high carrier migration Efficiency, improved performance, and improved contact area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] As mentioned in the background technology, in the prior art, as the size of semiconductor devices is gradually reduced, various adverse effects restrict the further reduction of device size. How to use high-performance one-dimensional nanostructures to form transistors with better performance is an urgent problem to be solved. The problem.

[0034] This embodiment provides a method for forming transistors and complementary transistors using one-dimensional nanostructures to form transistors with higher performance and higher integration.

[0035]In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

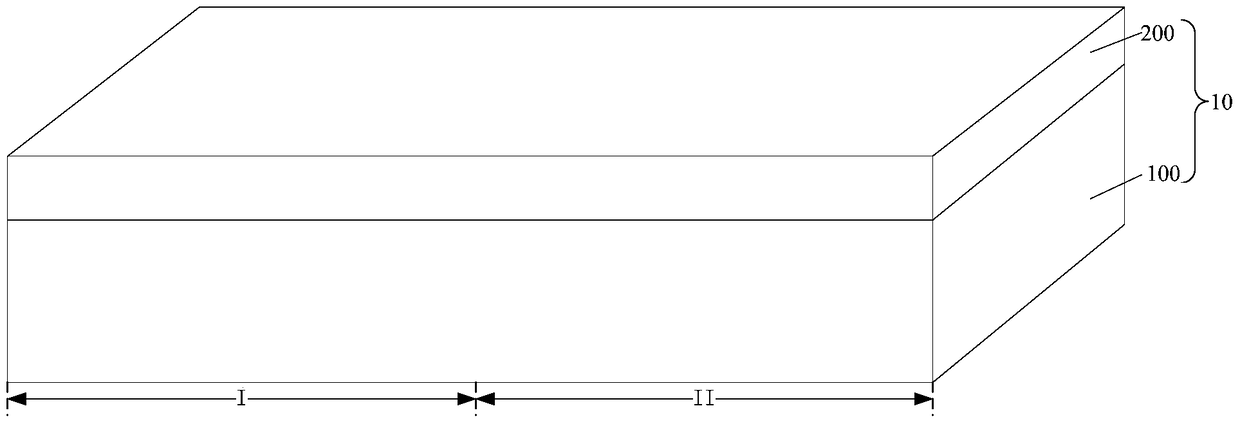

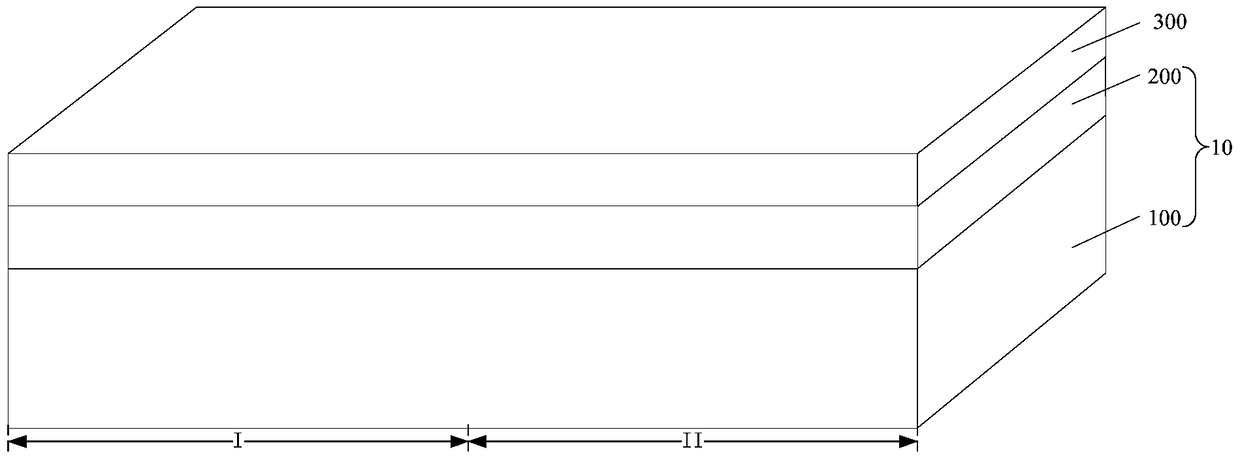

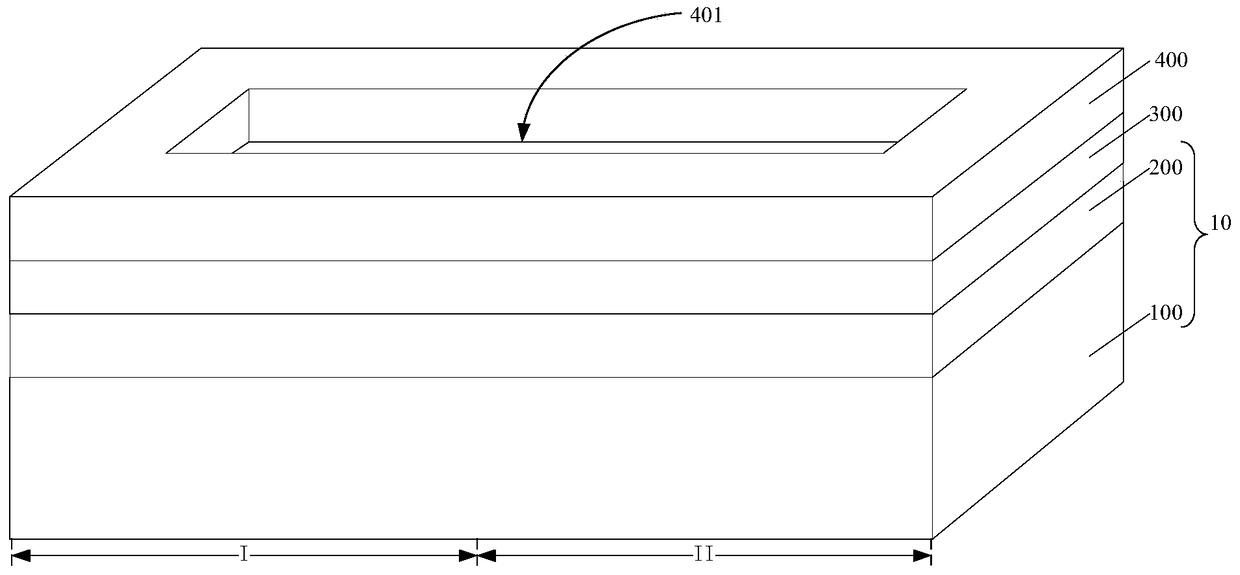

[0036] Please refer to figure 1 , providing a substrate 10 .

[0037] The material of the substrate 10 includes semiconductor materials such as silicon, germanium, silicon germanium, gallium ars...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More