DP video signal timing sequence recovery device and method

A video signal and timing technology, applied in color TV parts, TV system parts, TV and other directions, can solve the problem that the signal quality is easily interfered by other signals, the design layout and wiring are difficult, and the DDR data is complicated to read and write. and other problems, to achieve the effect of reducing the size of the PCB board, reducing the cost, and reducing the difficulty of layout

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments:

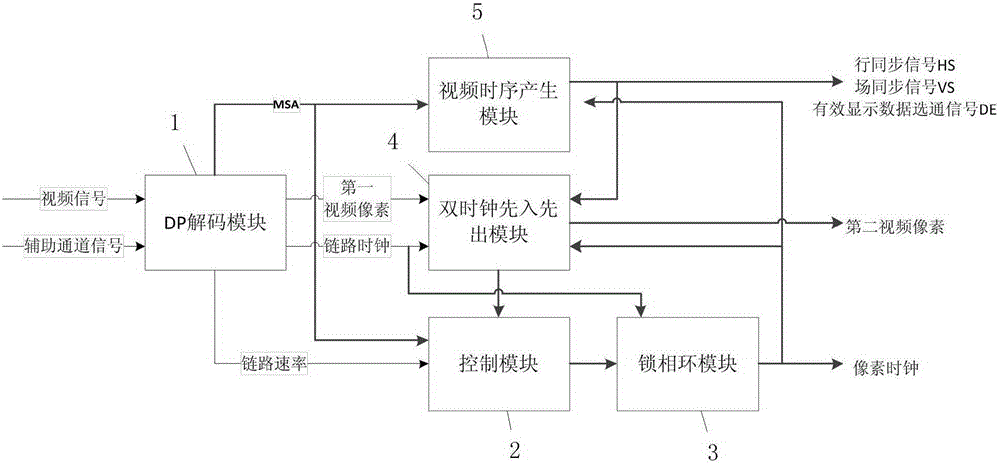

[0024] like figure 1 As shown, the device shown in the present invention includes a DP decoding module 1 , a video timing generation module 5 , a dual clock FIFO module 4 , a control module 2 and a phase-locked loop module 3 .

[0025] The video timing generation module 5 receives the MSA parameters output by the DP decoding module 1 and the pixel clock output by the phase-locked loop module 3, and generates field synchronization signals VS, horizontal synchronization signals HS, effective Display data strobe signal DE. The dual clock FIFO module (DoubleClockFirstInFirstOut) 4, that is, the FIFO queue in which the write clock and the read clock can be different. Receive the first video pixel and the link clock sent by the DP decoding module 1, store the first video pixel according to the link clock, receive the pixel clock input by ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More