A dram DDR calibration circuit and method based on zq pins

A technology of DRAMDDRZQ and pins, which is applied in the field of detecting the use status of DRAMDDRZQ pins, can solve problems such as misjudgment, and achieve the effect of avoiding misjudgment and improving robustness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

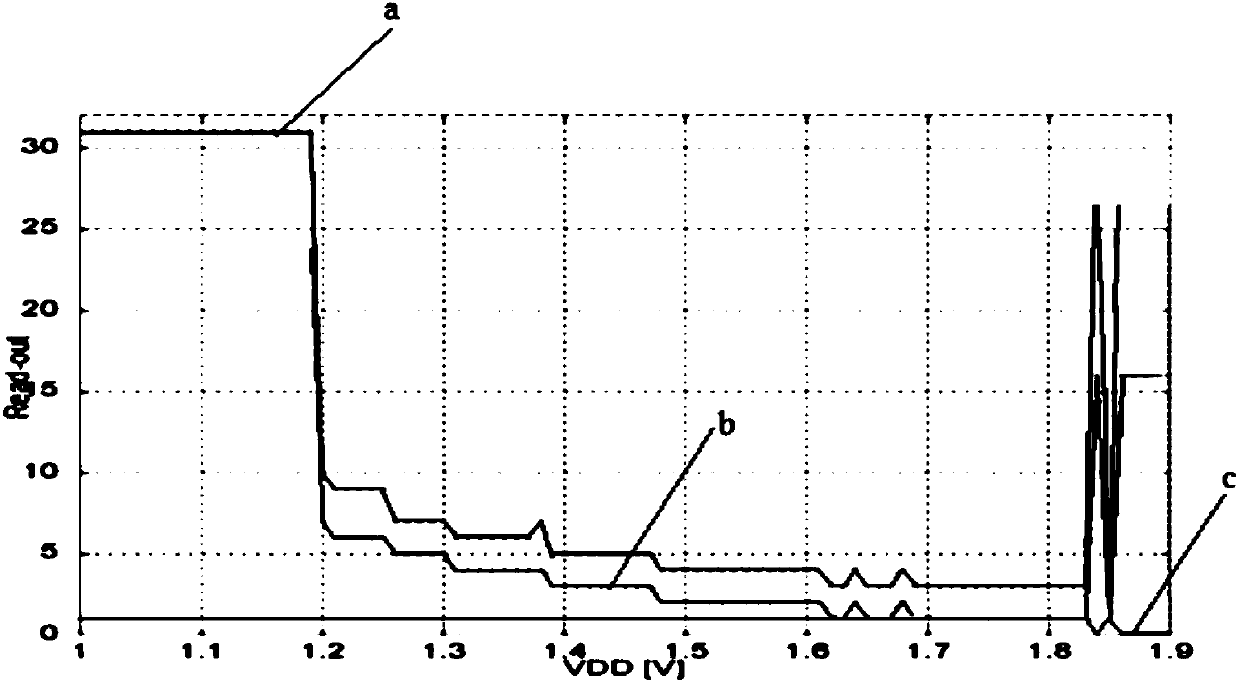

[0048] Embodiment 1: as Figure 4 As shown, the detection circuit of DRAM DDR ZQ pin usage status includes PMOS tube group, comparator, reference voltage supply circuit and ZQ pin judgment control module. The size of the PMOS tube is divided into N, so that the resistance of the PMOS tube group is at least 10 times greater than the reference resistance RZQ provided by the ZQ pin. The ZQ pin judgment control module includes a state judgment module. One end of the PMOS tube group is connected to the external power supply VDD. The other end of the PMOS tube group is connected to the ZQ pin and then connected to the positive phase input terminal of the comparator, the negative phase input terminal of the comparator is connected to the reference level, the output terminal of the comparator outputs the comparison result to the state judgment module, and the state judgment module Judge the use state of the ZQ pin according to the input comparison result.

[0049] Generally, the PMOS...

Embodiment 2

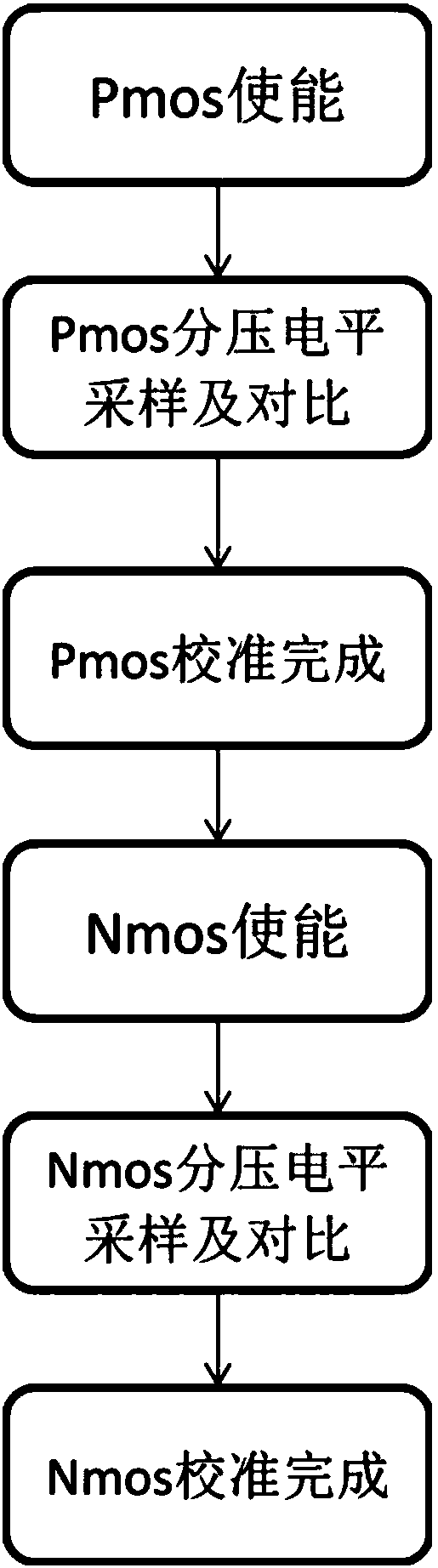

[0050] Embodiment 2: the detection method of DRAM DDR ZQ pin use state, comprises the following steps:

[0051] 1] Configure the PMOS enable signal so that the PMOS tube group is configured in the limit resistance state; for example, the limit resistance mode is configured as 2kΩ, and the general standard RZQ=240Ω;

[0052] 2] Compare the reference level and the divided voltage level to obtain the comparison result;

[0053] 3] According to the comparison result, judge the usage status of the ZQ pin:

[0054] If the divided voltage level is less than the reference level VDD / 2, the ZQ pin is valid and connected with a resistor RZQ;

[0055] If the divided voltage level is greater than the reference level VDD / 2, the ZQ pin is floating, and the resistor RZQ is not connected.

[0056] The working principle is to use 2kΩ to compare with the external standard RZQ=240Ω. If a ZQ resistor is connected, the divided voltage level must be much smaller than VDD / 2. If there is no external...

Embodiment 3

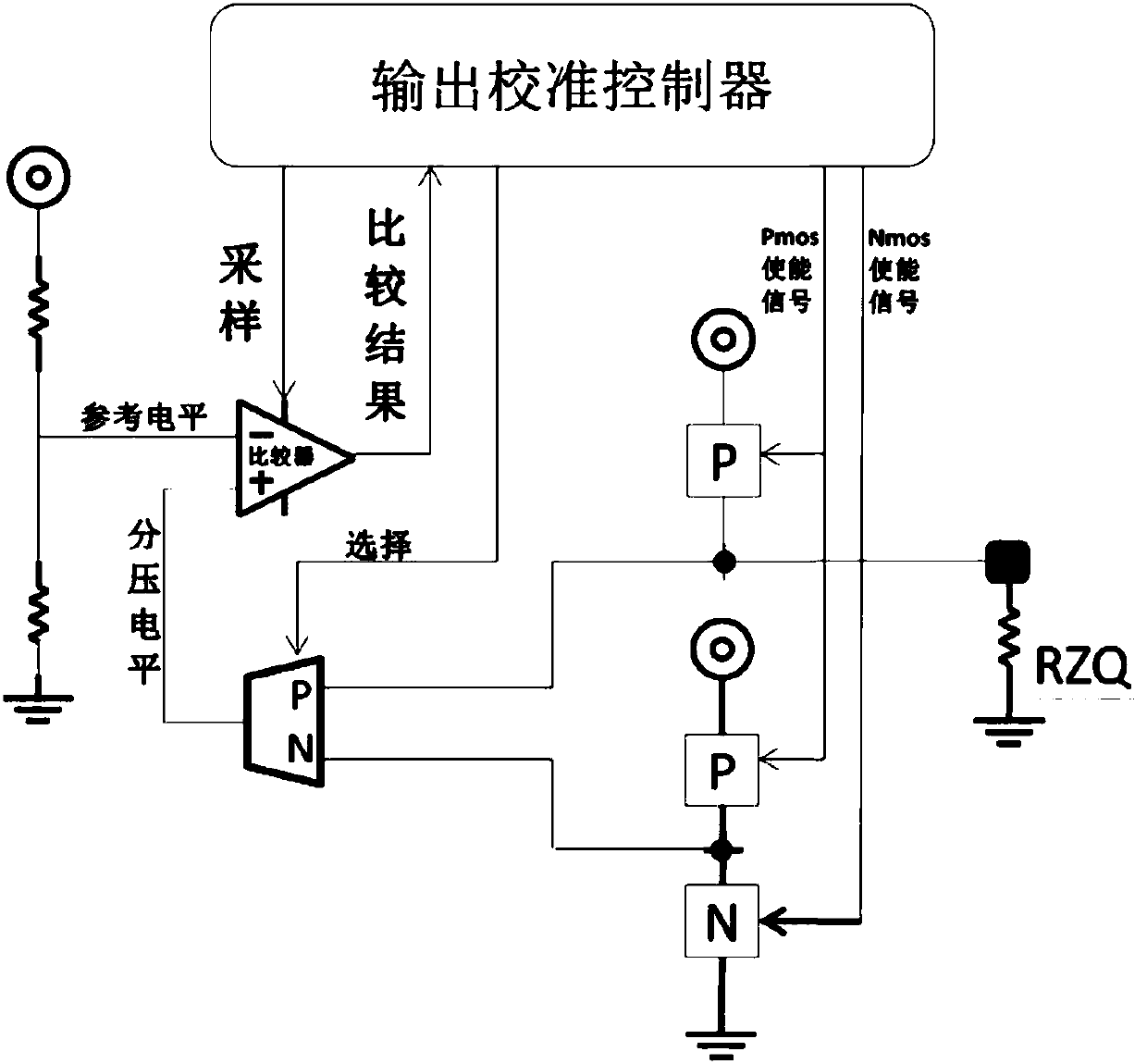

[0057] Embodiment 3: as Figure 5 As shown, the DRAM DDR calibration circuit includes a detection circuit, and also includes a mirrored PMOS tube group, an NMOS tube group, and a selector. The ZQ pin judgment control module also includes an enable generation module. The reference voltage generated by the reference voltage supply circuit is equal to VDD / 2, the PMOS tube with the smallest size in the PMOS tube group is divided into N, so that the resistance of the PMOS tube group is at least 10 times greater than the reference resistance RZQ provided by the ZQ pin, and the mirrored PMOS tube group is the same as the NMOS tube group and the PMOS tube group One end of the PMOS tube group is connected to the external power supply VDD, the other end of the PMOS tube group is connected to the ZQ pin and then connected to an input terminal of the selector; one end of the mirrored PMOS tube group is connected to the external power supply VDD, and the other end of the mirrored PMOS tube...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More