A decryption hardware platform based on fpga

A hardware platform, ciphertext technology, applied in the field of information security, can solve the problems of low clock frequency, long time consumption, poor general performance of hardware platform, etc., to achieve the effect of increasing data transmission bandwidth, reducing data transmission time, and improving the efficiency of cracking

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further described in detail below in conjunction with the embodiments and the accompanying drawings, but the embodiments of the present invention are not limited thereto.

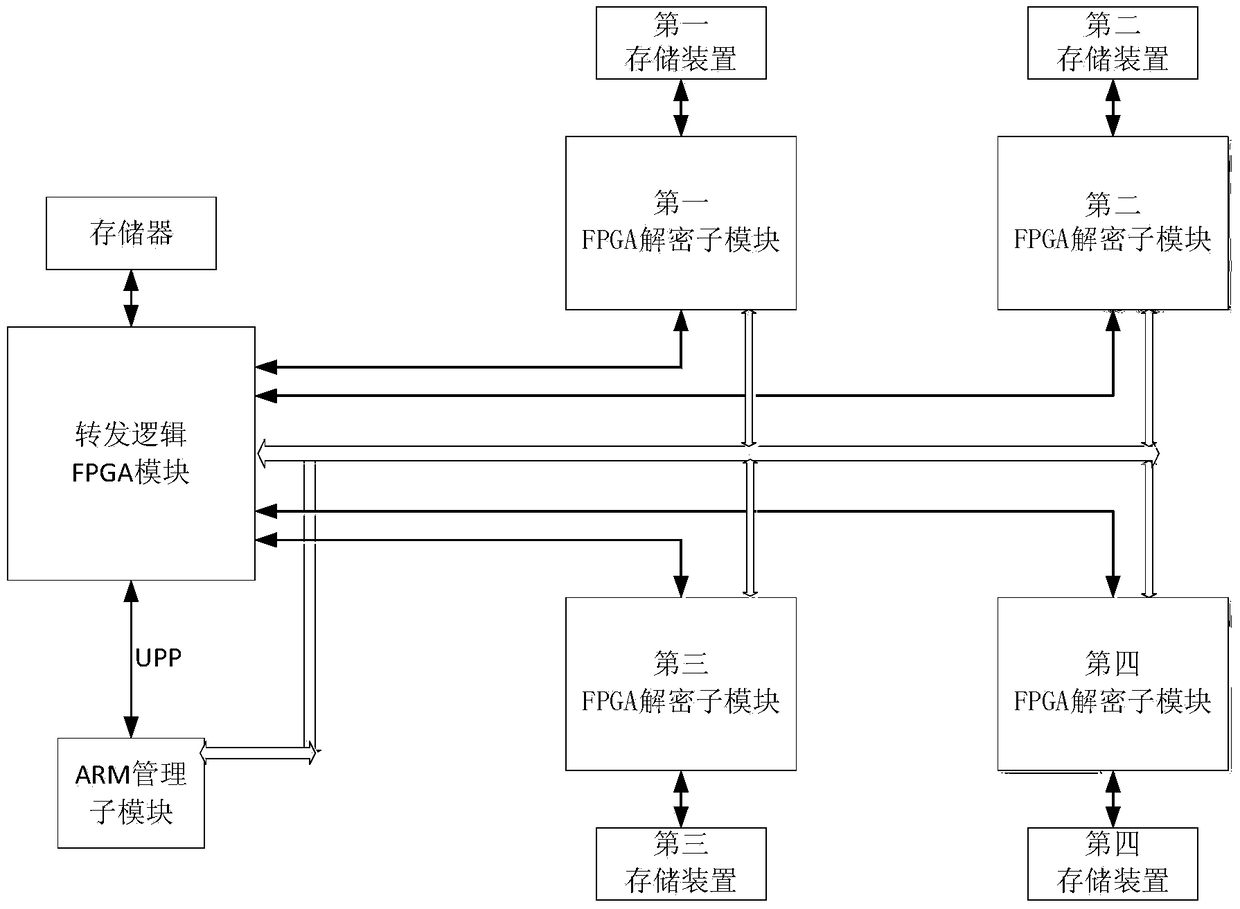

[0036] Such as figure 1 , an FPGA-based decryption hardware platform, including a forwarding logic FPGA module, N mutually independent FPGA decryption sub-modules and ARM management sub-modules respectively connected to the forwarding logic FPGA module, and a forwarding logic FPGA module, N mutually independent An independent FPGA decryption sub-module and a power management module powered by the ARM management sub-module, the N mutually independent FPGA decryption sub-modules are respectively connected to the ARM management sub-module, N≥2; wherein

[0037] The forwarding logic FPGA module is responsible for sending and uploading data, and communicates with N mutually independent FPGA decryption sub-modules and ARM sub-modules; communicates with the ARM management sub-m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More