Automatic endurance test device and test method of discrete memory

A test device and test method technology, applied in the direction of static memory, instrument, etc., can solve the problems of endurance test efficiency decline, test time consumption, etc., and achieve the effect of saving time and cost, eliminating communication time, and adjustable endurance voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

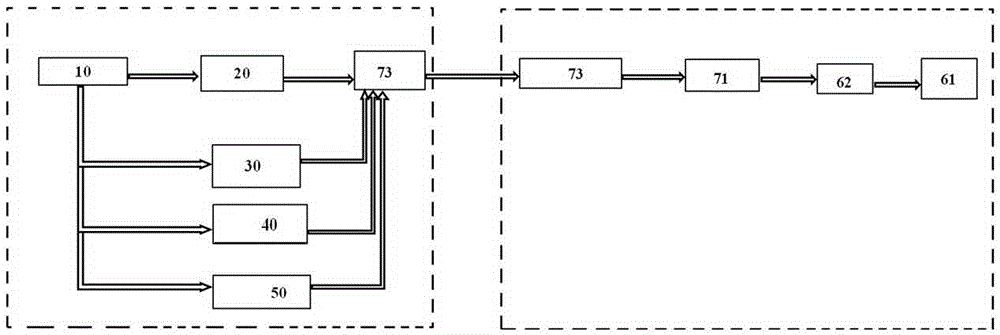

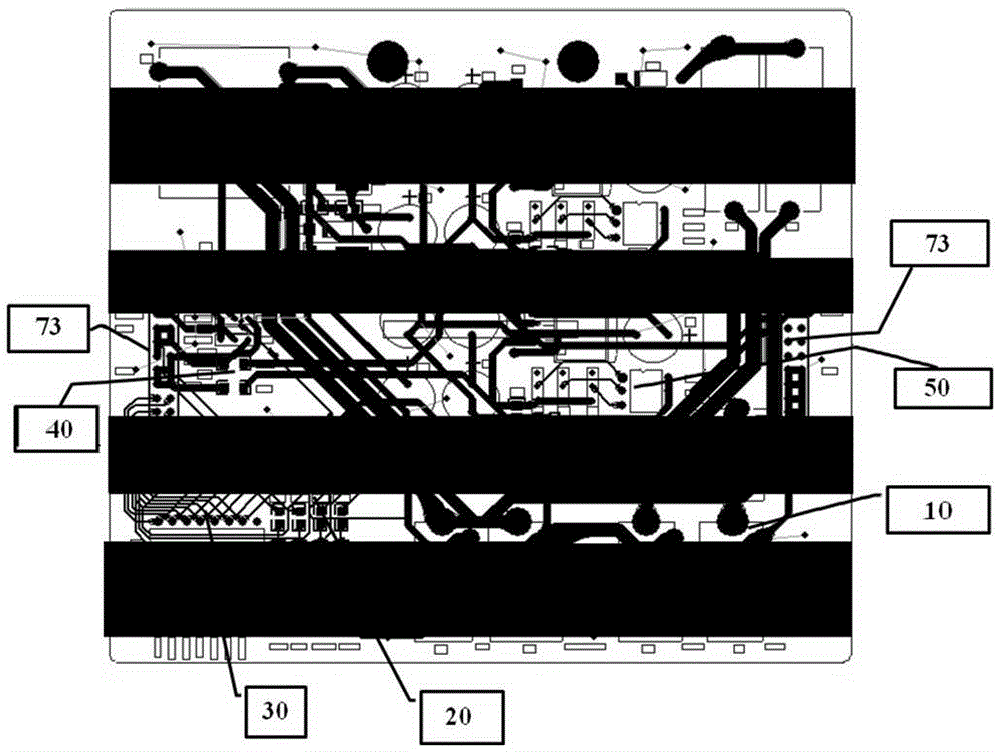

[0033] see figure 1 , figure 2 and image 3 , the discrete integrated circuit chip automatic endurance test device of the present invention comprises a total control board and a drive board for endurance testing, the total control board includes a power supply 10, a total control unit 20, a main control unit 30, a clock unit 40, and a reset unit 50 And communication pin module 73; Driver board includes communication control unit 70, test unit 60 and fixed connection hole 80; Wherein, power supply 10 is used for supplying power, dial code control switch 20 is used for selecting test voltage and switch test main control panel power supply, The single-chip microcomputer 30 is used to store the test OS and record the test results as the main control chip of the whole endurance test, the clock unit 40 is used to provide the clock signal for the whole test, the reset unit 50 is used to power on and send a reset signal, and the communication pin module 73 is used for The signal of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More