Semiconductor storage apparatus

A storage device and semiconductor technology, applied in information storage, static memory, read-only memory, etc., can solve problems such as uneven ion implantation, uneven pattern, and bit errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] Embodiments of the present invention will be described in detail below with reference to the drawings. The present invention can be applied to nonvolatile memories with various types of memory structures, so an ideal type of NAND flash memory is taken as an example for illustration. In addition, each part is emphasized in illustration for easy understanding, and attention should be paid to the difference in scale of an actual device.

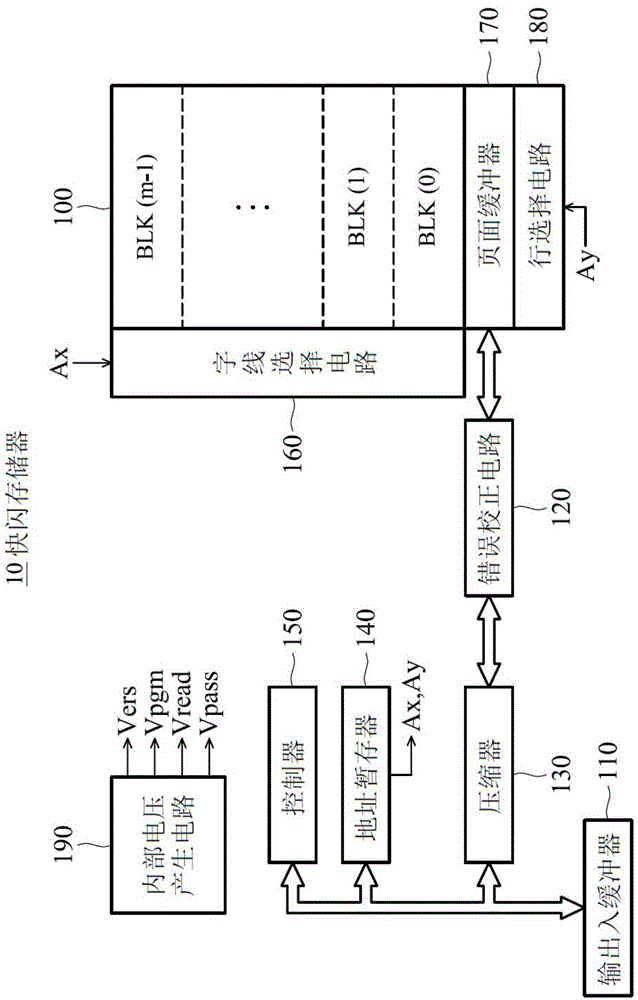

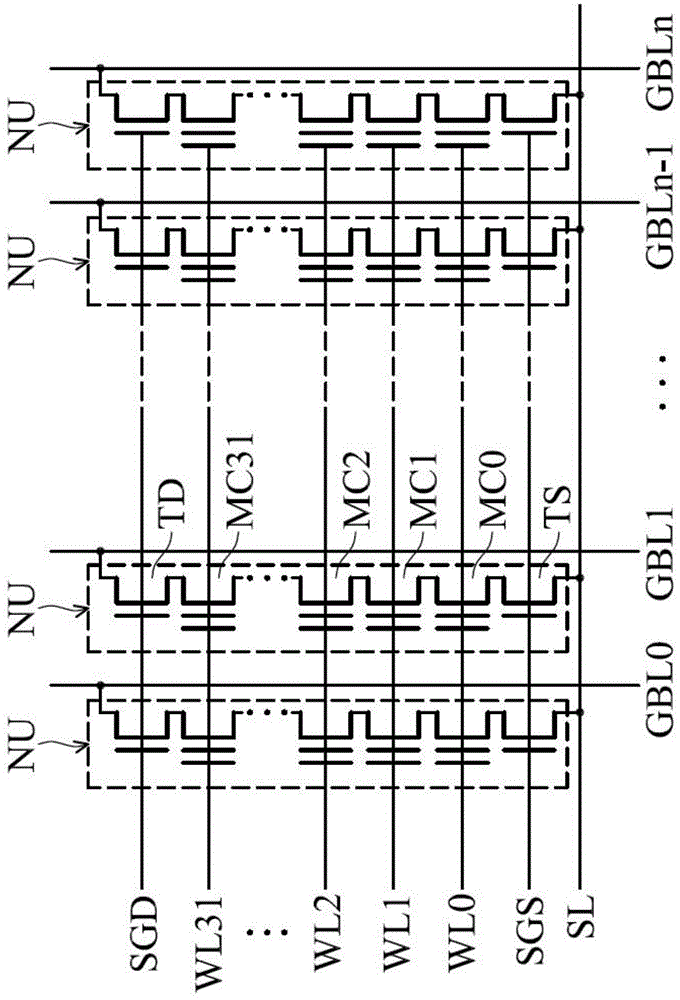

[0050] figure 1Shown is a schematic diagram of a typical flash memory pertaining to embodiments of the present invention. However, the flash memory shown here is only used as an example, and is not intended to limit the concept of the present invention. The flash memory 10 shown in this embodiment includes a memory array 100 in which a plurality of memory cells are arranged in rows and columns, an I / O buffer 110 that is connected to external I / O terminals and maintains I / O data, and reads out bit data and The error correction circuit 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More