Equivalent sampling device for time-delay amount automatic correction

A technology of equivalent sampling and automatic correction, which is applied in the direction of instruments, computer control, simulators, etc., can solve the problems of radar echo information loss, redundancy, equivalent sampling inhomogeneity, etc., and achieve high measurement accuracy and circuit structure Simple, real-time corrective effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

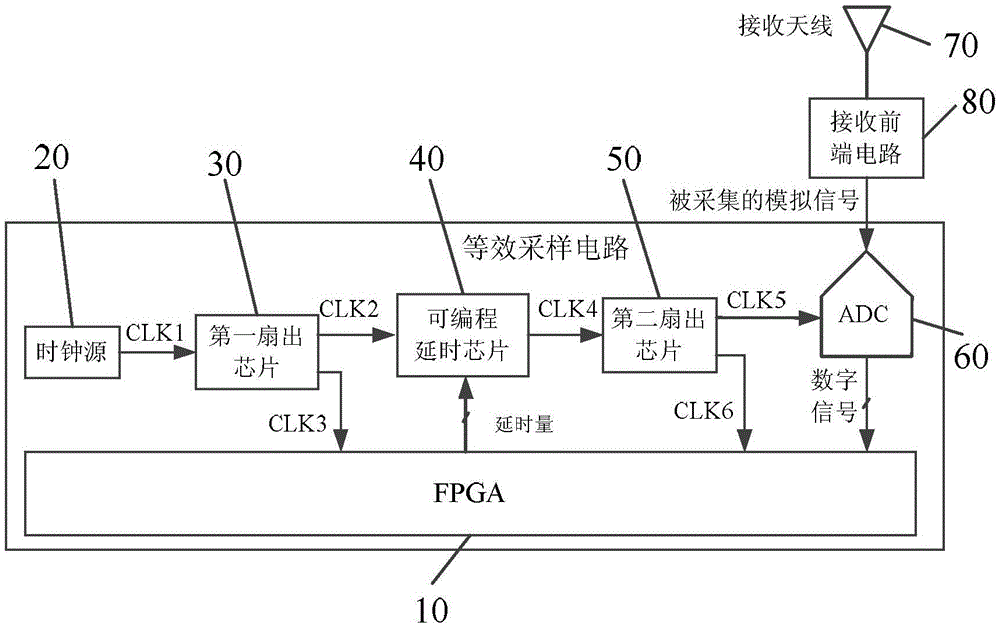

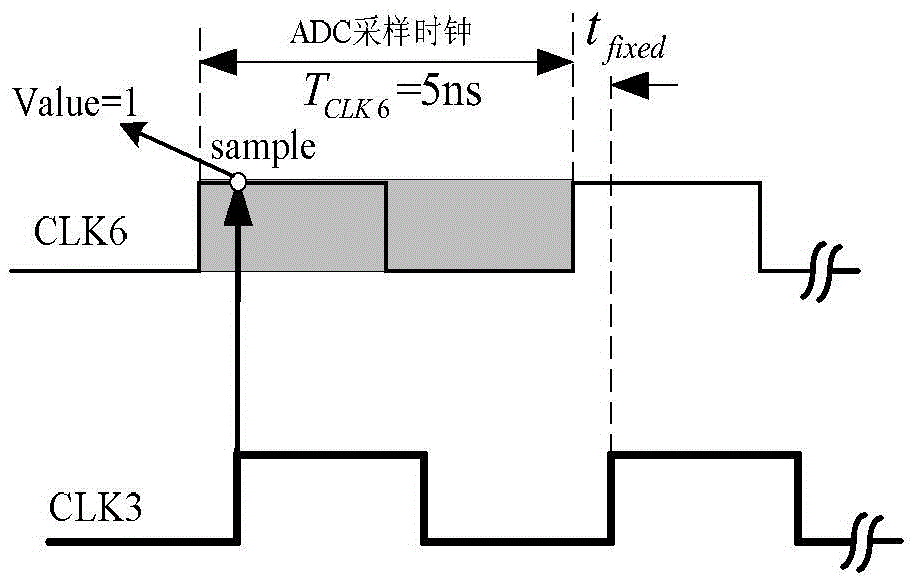

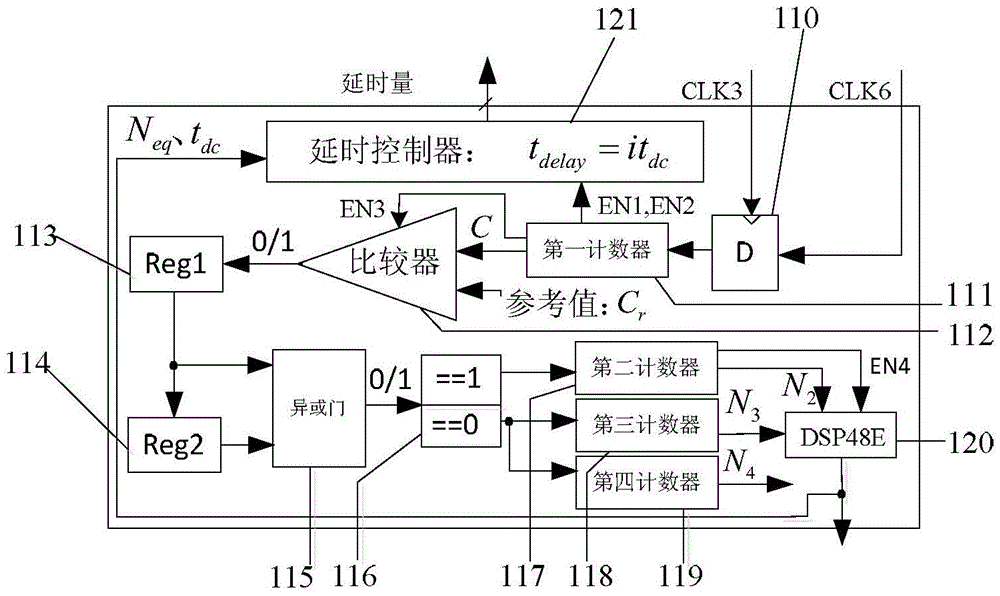

[0034] The equivalent sampling device for automatically correcting the delay amount of the present invention is based on a programmable delay chip and a programmable logic gate array FPGA, wherein the automatic correction process of the delay amount mainly includes: using the FPGA to measure the delay accuracy of the programmable delay chip in real time ; Then automatically adjust the delay amount in the equivalent sampling according to the delay accuracy of the delay circuit, so as to ensure equivalent sampling at equal intervals.

[0035] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0036] In an exemplary embodiment of the present invention, an equivalent sampling device for automatic correction of delay is provided. figure 1 It is a structural schematic diagram of an eq...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com