Global detection module method for node interconnection chip verification

A technology for detecting modules and nodes, which is used in error detection/correction, detection of faulty computer hardware, measurement of electricity, etc. limited and other problems, to achieve the effect of good promotion and use value, simple structure and excellent effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

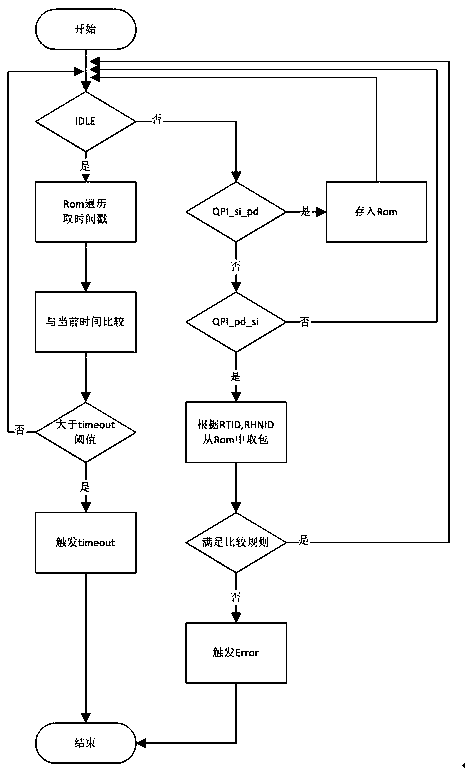

[0021] A global detection module method for node interconnection chip verification of the present invention, the steps are as follows:

[0022] (1) Embed the node interconnection chip logic in the form of an independent module, run simultaneously with the node interconnection logic, monitor the message information exchanged by each channel, perform error detection according to the corresponding protocol rules, and report timeout and message error information, all automatic running;

[0023] (2) Store the active QPI message sent by the CPU. When a QPI message is returned from the NC, compare it with the corresponding stored source QPI message to determine whether it is the desired message; at the same time, each A timestamp (Timestamp) is added to each message sent by a CPU to determine whether it times out.

[0024] Preferably, the modules in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More