Well isolation type anti-SEU multi-node overturning storage unit layout structure

A storage unit and layout structure technology, applied in electrical components, transistors, electric solid-state devices, etc., can solve the problems of ordinary DICE storage unit flipping, improve anti-SEU performance, reduce the probability of multi-node flipping, and increase the distance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

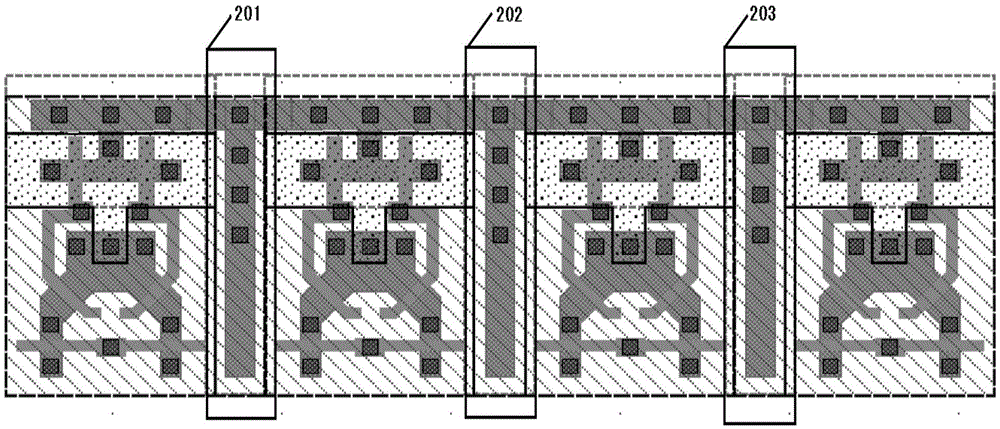

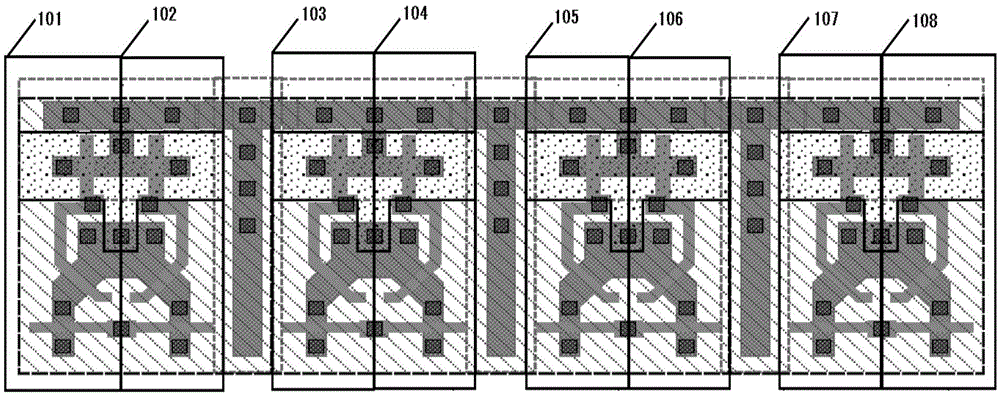

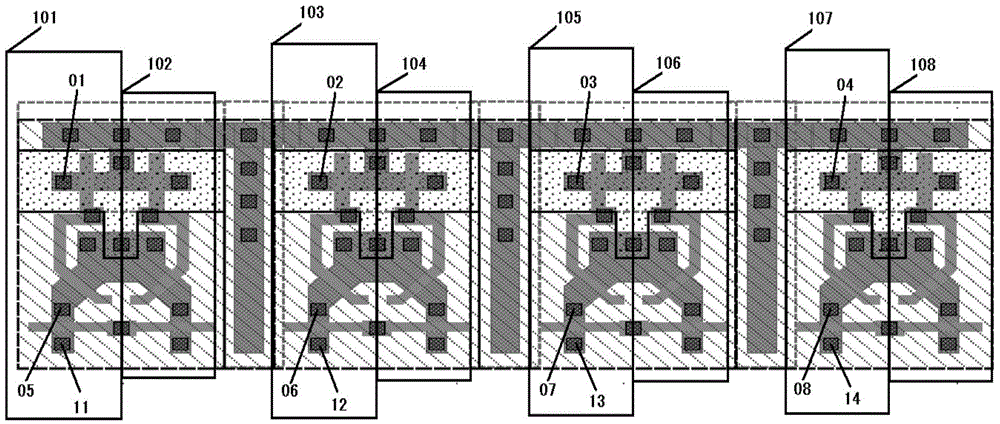

[0026] The invention overcomes the disadvantage that common DICE memory cells in the ultra-deep sub-micron process will cause multiple storage nodes in the unit to flip under the influence of SEU, and eventually lead to the flipping of common DICE memory cells, and proposes a new well-isolated anti-corrosion The SEU multi-node flip memory cell layout structure can effectively separate all sensitive node pairs in the common DICE memory cell structure and increase the distance between sensitive node pairs. Among them, for PMOS transistors, N-well isolation can effectively stabilize the N-well voltage. Reduces the chance of flipping multiple storage nodes due to parasitic bipolar transistor effects. For NMOS transistors, the N-well isolation effectively shunts the holes generated by incoming particles, reducing the occurrence of multiple storage nodes due to charge sharing effects. The probability of flipping, thereby suppressing the multi-node flipping caused by SEU in the DICE u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com