Patents

Literature

30results about How to "Reduce the probability of flipping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

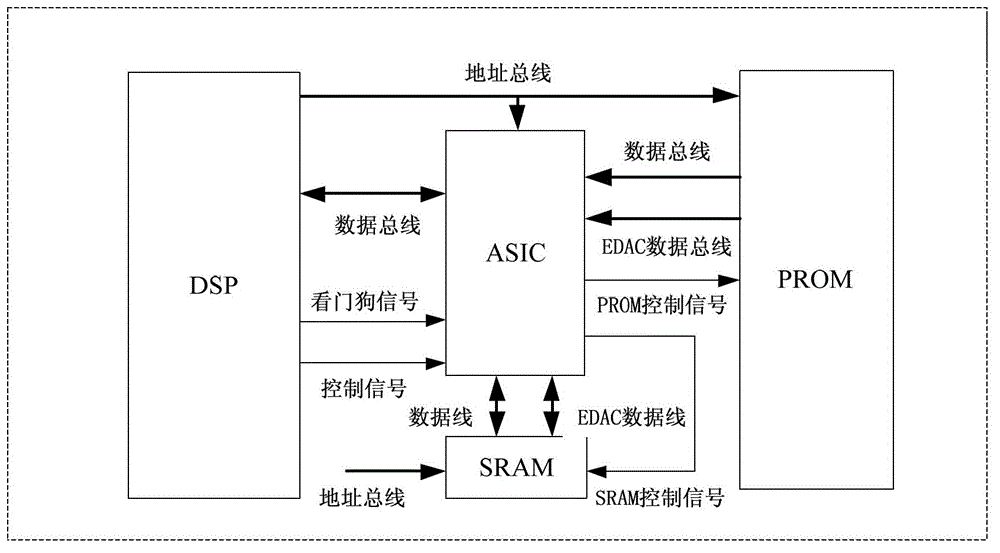

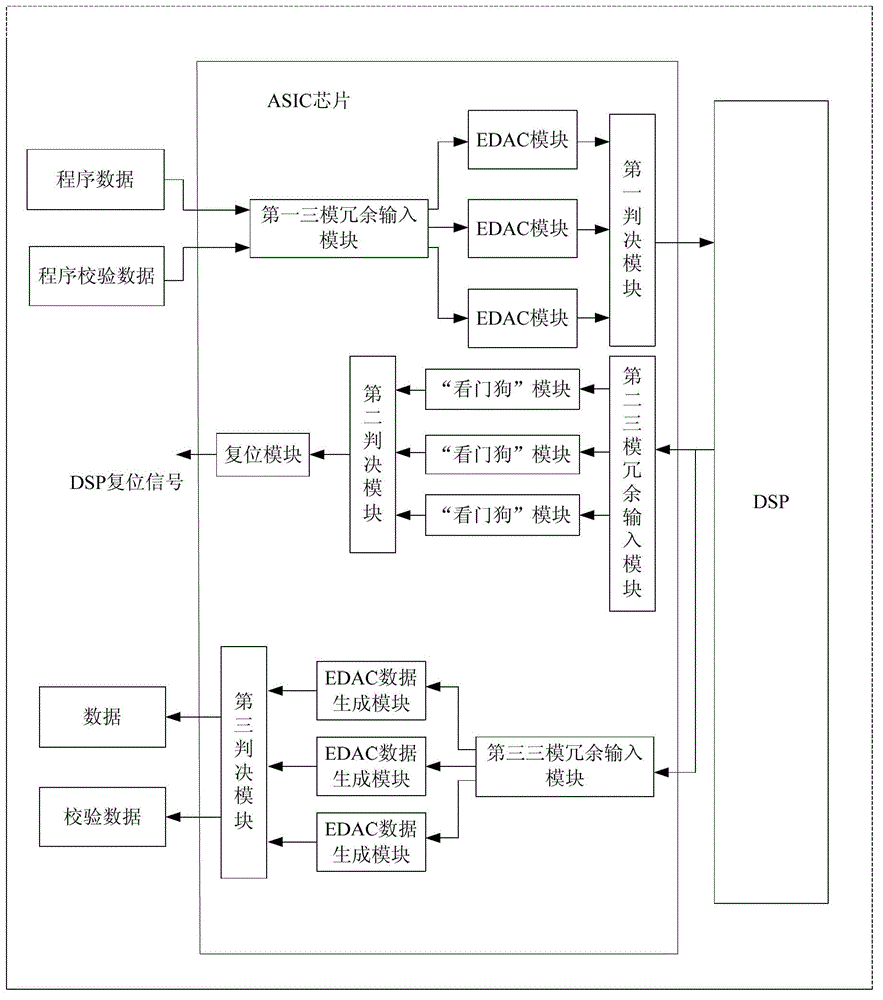

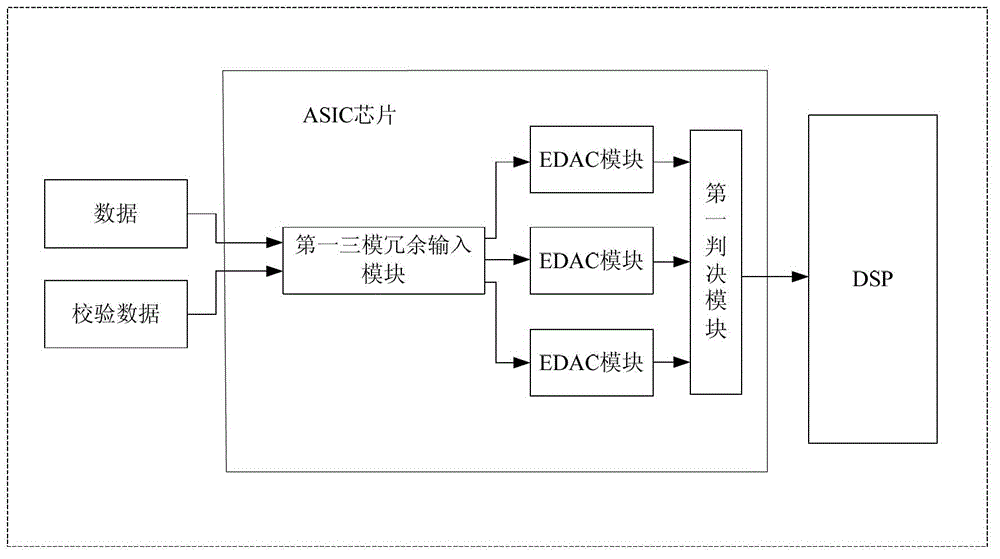

Spaceborne digital signal processor turning reinforcing method

ActiveCN103218272AImprove Inherent ReliabilityReduce the probability of single event eventsRedundant data error correctionStatic random-access memoryProgrammable read-only memory

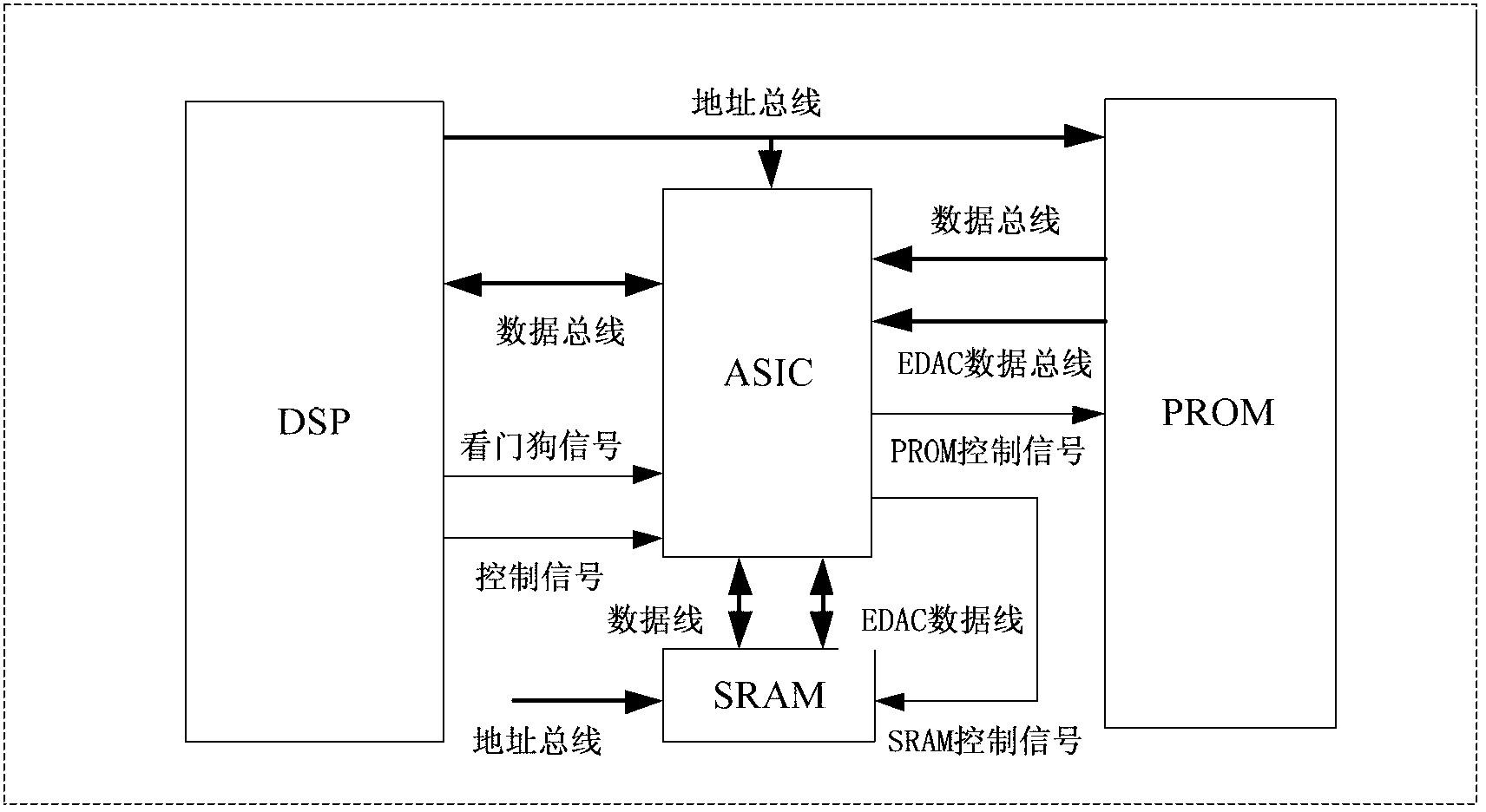

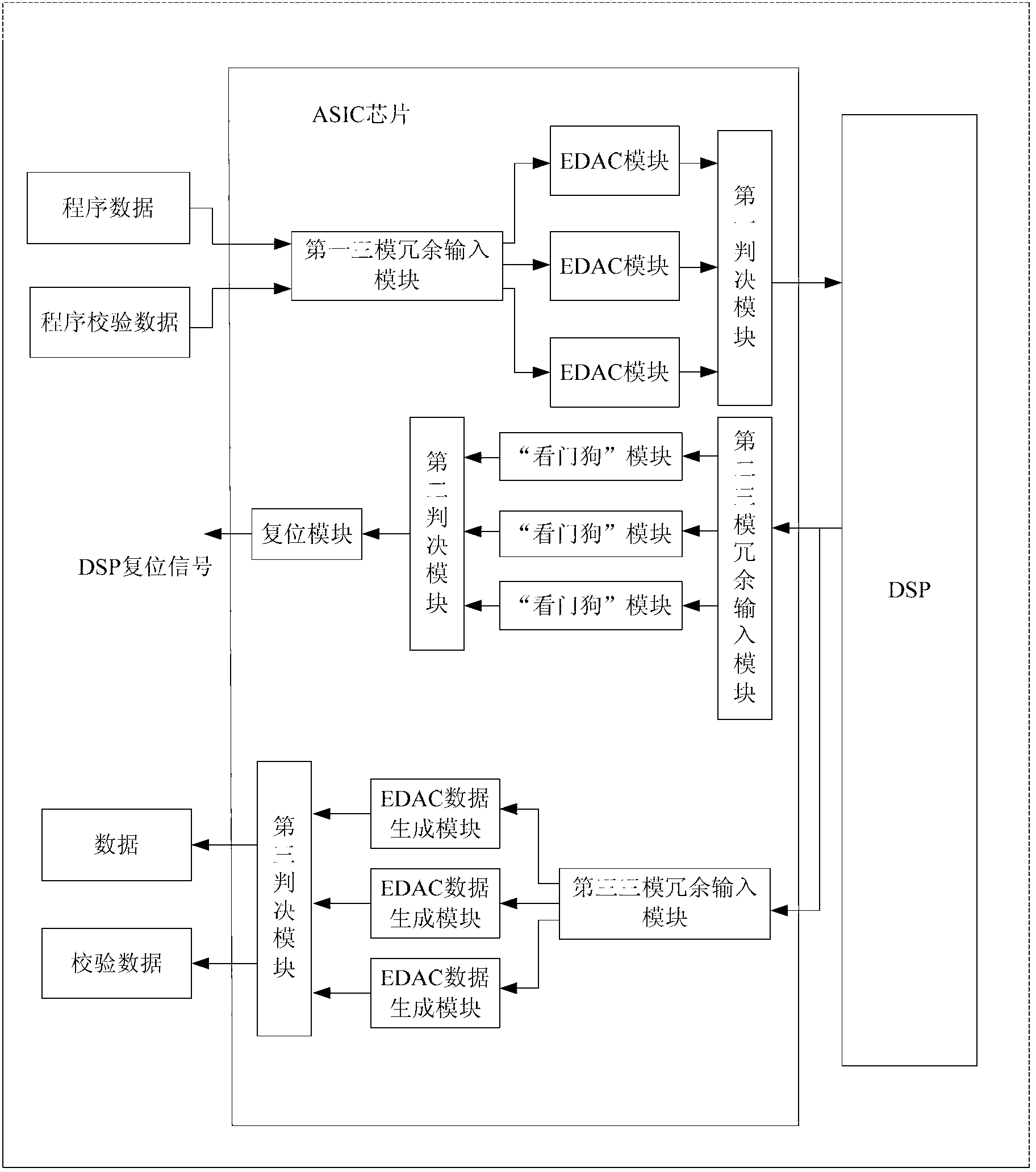

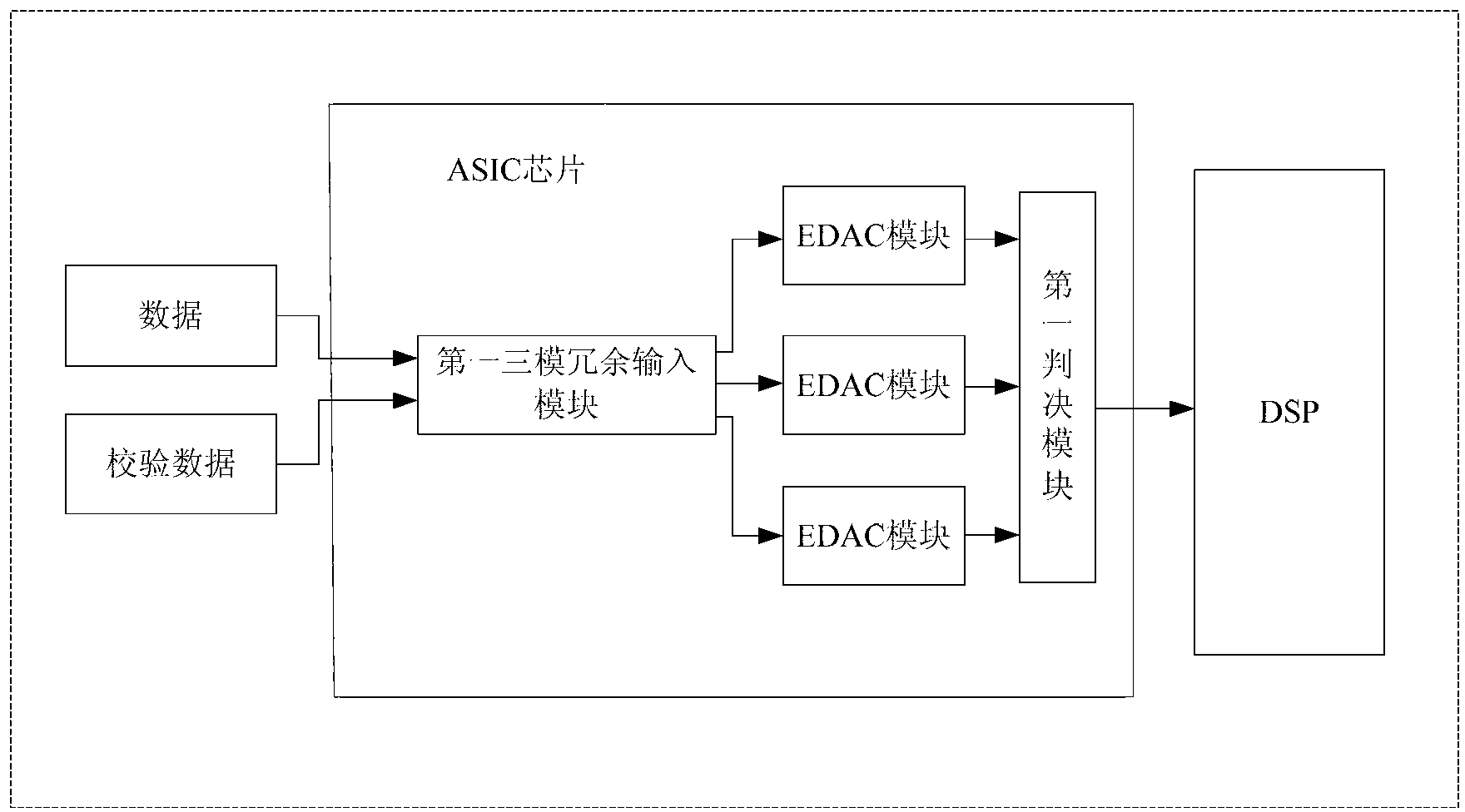

The invention relates to a spaceborne digital signal processor turning reinforcing method which is achieved through a spaceborne digital signal processor turning reinforcing system. The spaceborne digital signal processor turning reinforcing system comprises a digital signal processor (DSP) chip, an application specific integrated circuit (ASIC) chip, a programmable read only memory (PROM) and a static random access memory (SRAM). The method includes the steps of utilizing the design integrating outside slice running, error detection and correction (EDAC), an ASIC technology and a watchdog, meanwhile utilizing a radiation-proof ASIC technology to organically combine various anti-spatial-single-particle measures together, and to form a unique novel anti-single-particle reinforcing method. The spaceborne digital signal processor turning reinforcing method has the advantages of being capable of simplifying the system and improving inherent reliability, few in hardware resources, low in design complexity, simple in achieving, and capable of greatly reducing the rate of occurrence of single-particle events when the DSP chip runs in a bad radiation environment.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

Register circuit with radiation reinforcing design

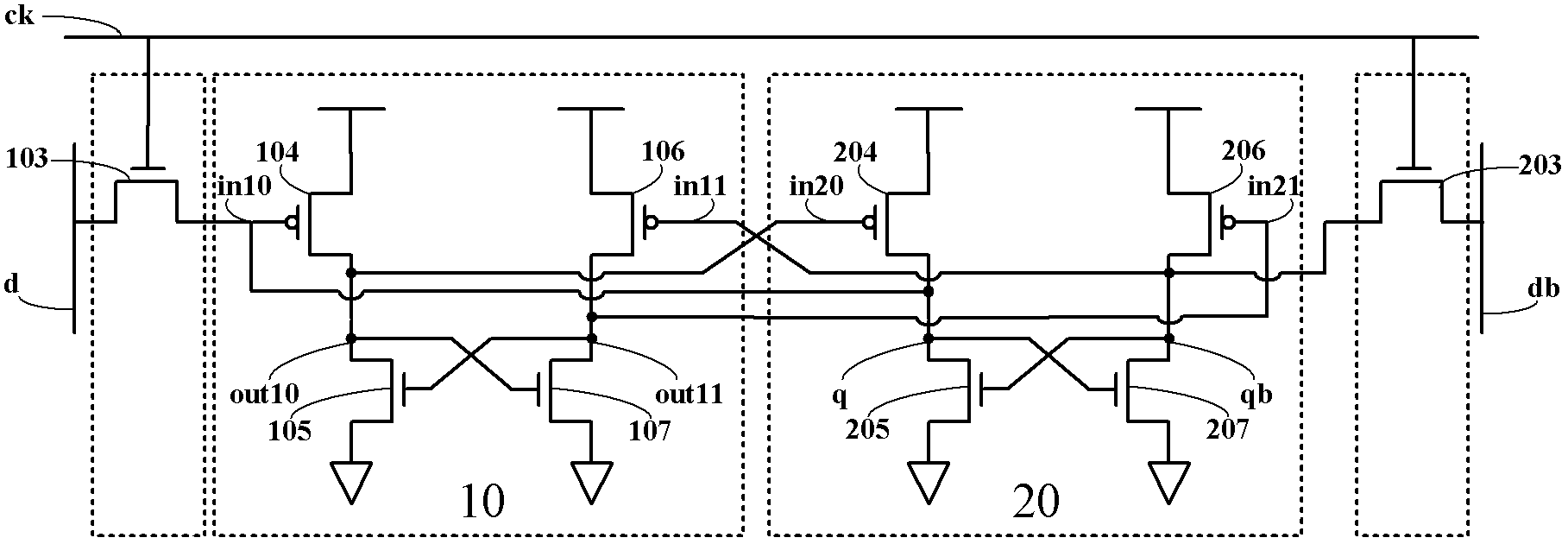

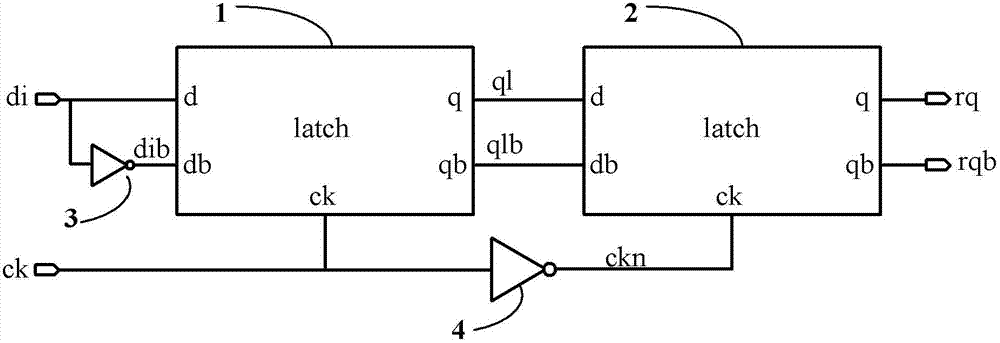

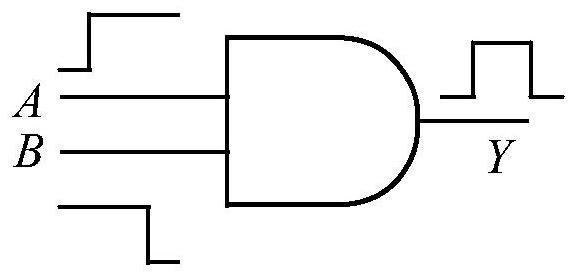

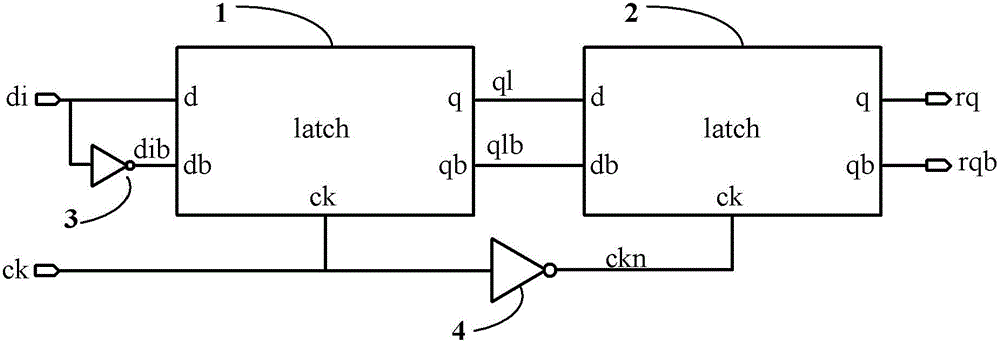

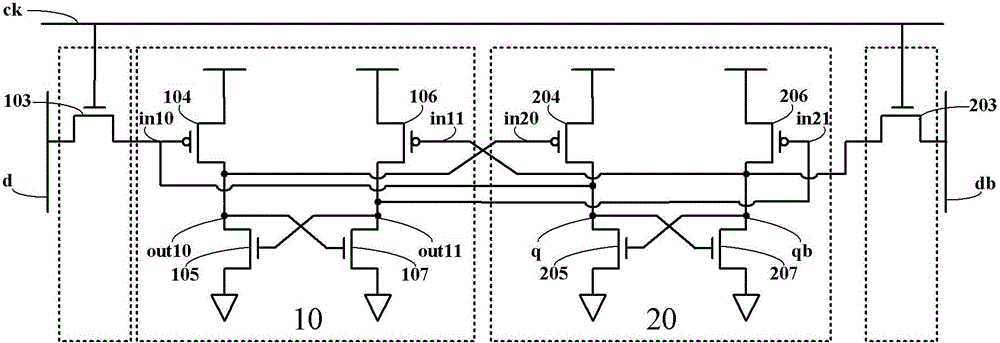

ActiveCN103077746AImprove radiation resistanceReduce the probability of flippingDigital storageProcessor registerEngineering

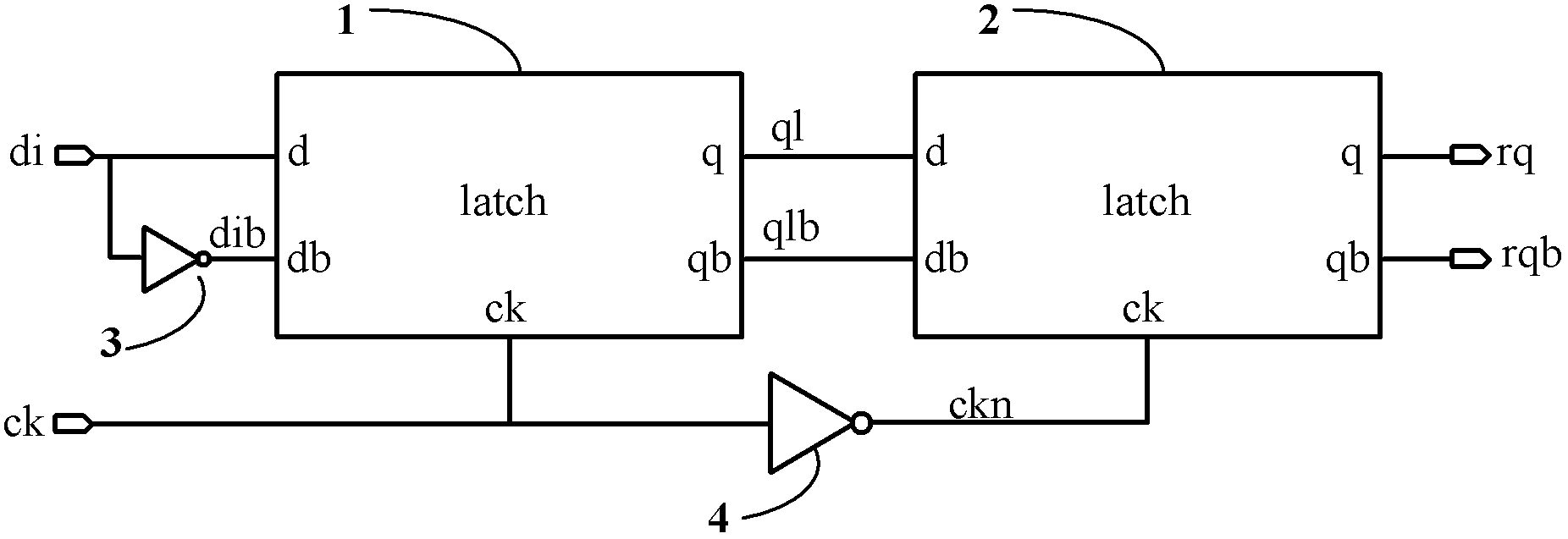

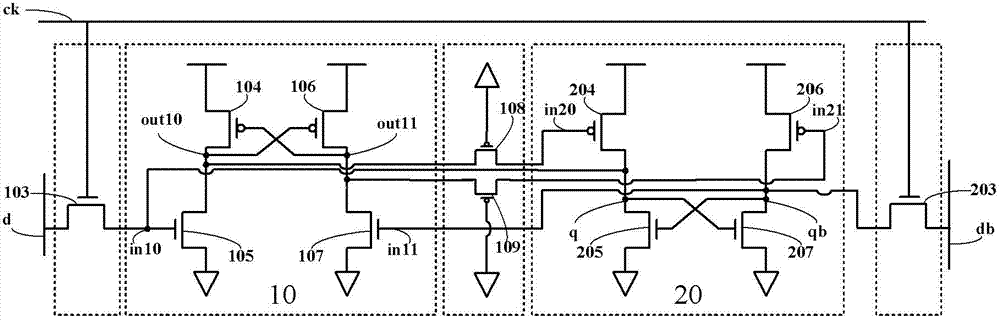

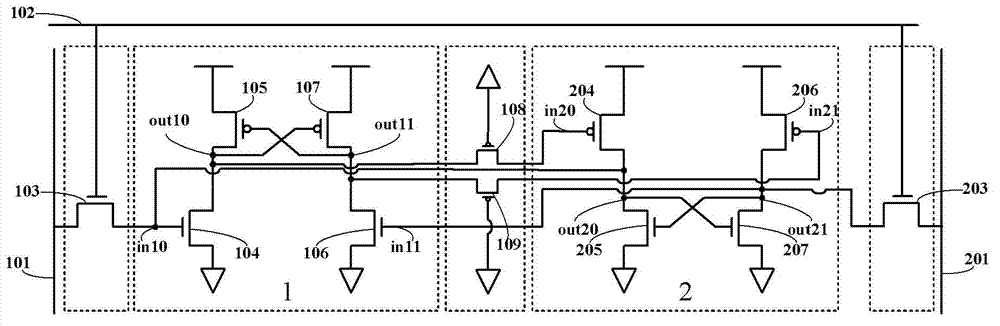

The invention discloses a register circuit with radiation reinforcing design, which comprises a first-stage master latch, a second-stage slave latch, a first phase inverter and a second phase inverter. The first-stage main latch is provided with two data inputs which are respectively from a data input di from a register and a complementary data input dib from the register; the first-stage main latch is provided with 1 clock input ck and two data outputs which are respectively a latch data ql and a complementary latch data qlb; the second-stage slave latch is provided with two data inputs which are respectively from the data output ql of the first-stage main latch and the complementary data output qlb of the first-stage main latch; the second-stage slave latch is provided one clock input ck and a complementary clock input ckn from the register; and the second-stage slave latch is provided with 2 data outputs which are respectively a register data rq of the register and a complementary register data rqb of the register. With the utilization of the register circuit with the radiation reinforcing design, the irradiation property of the register is enhanced, and no excessive area consumption is caused while the irradiation property of the register is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

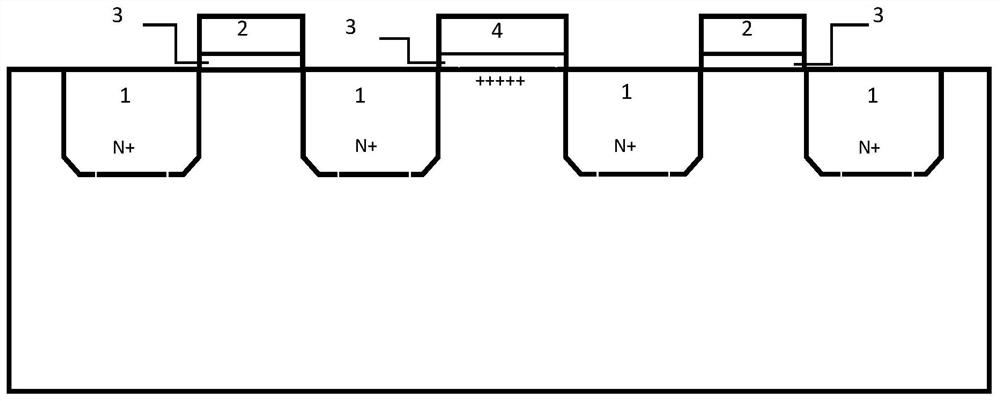

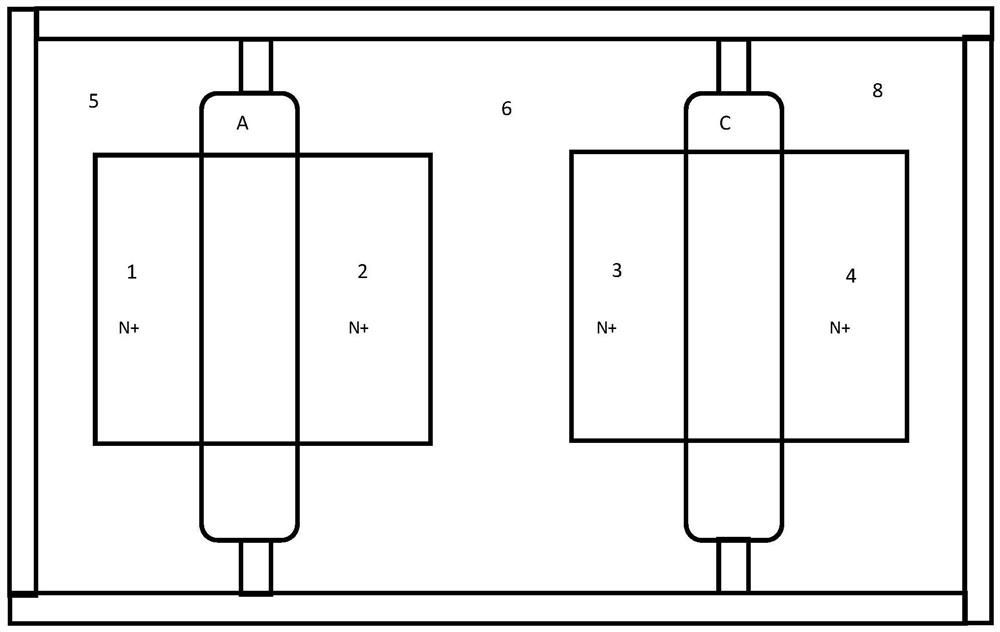

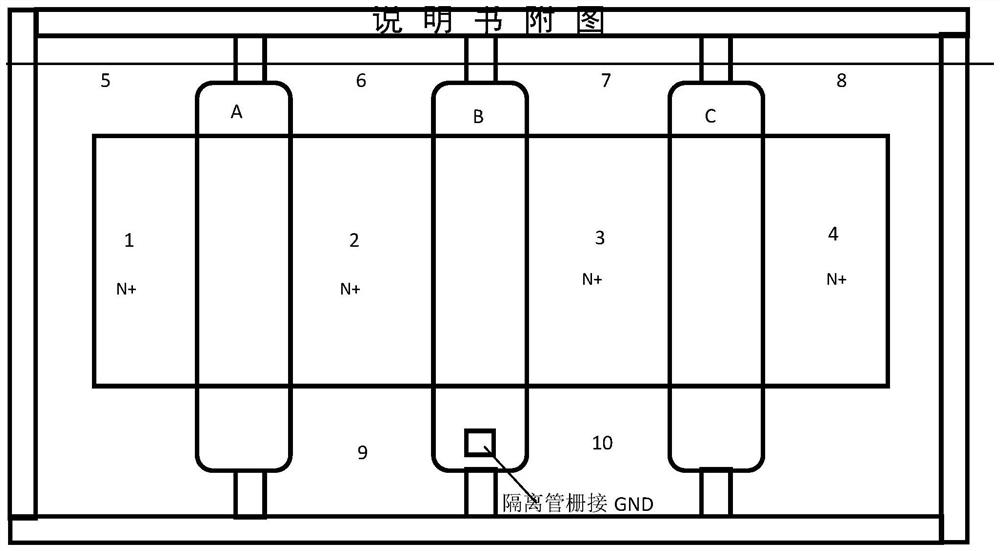

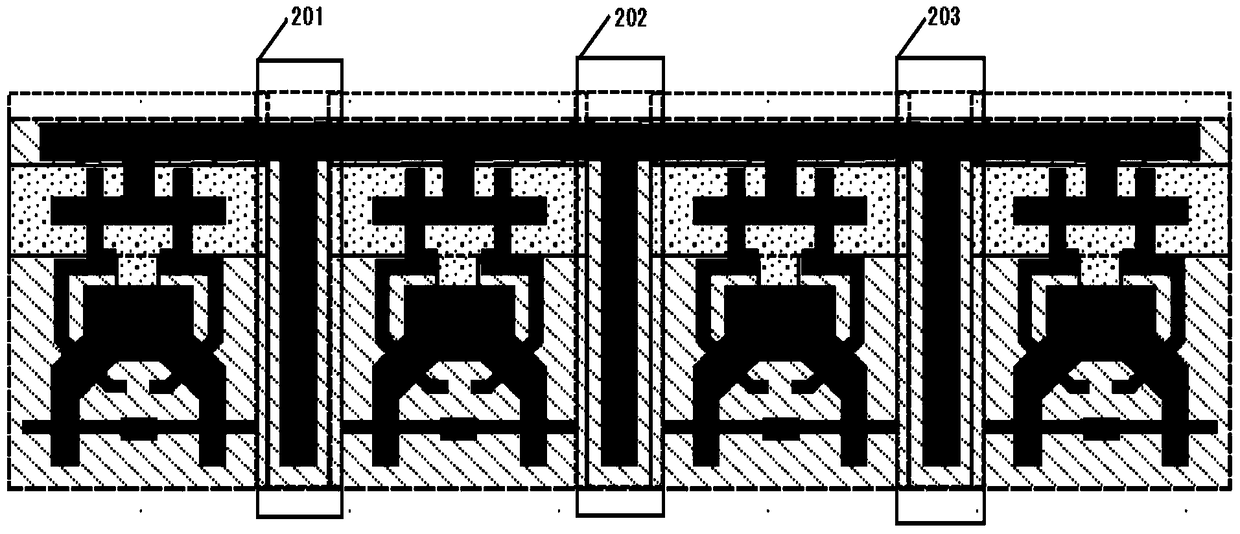

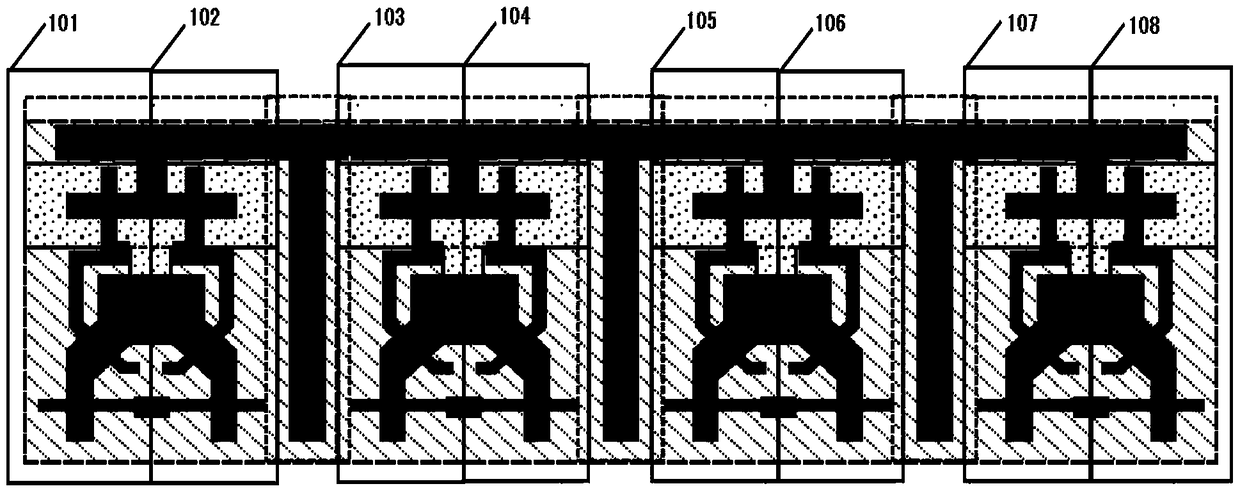

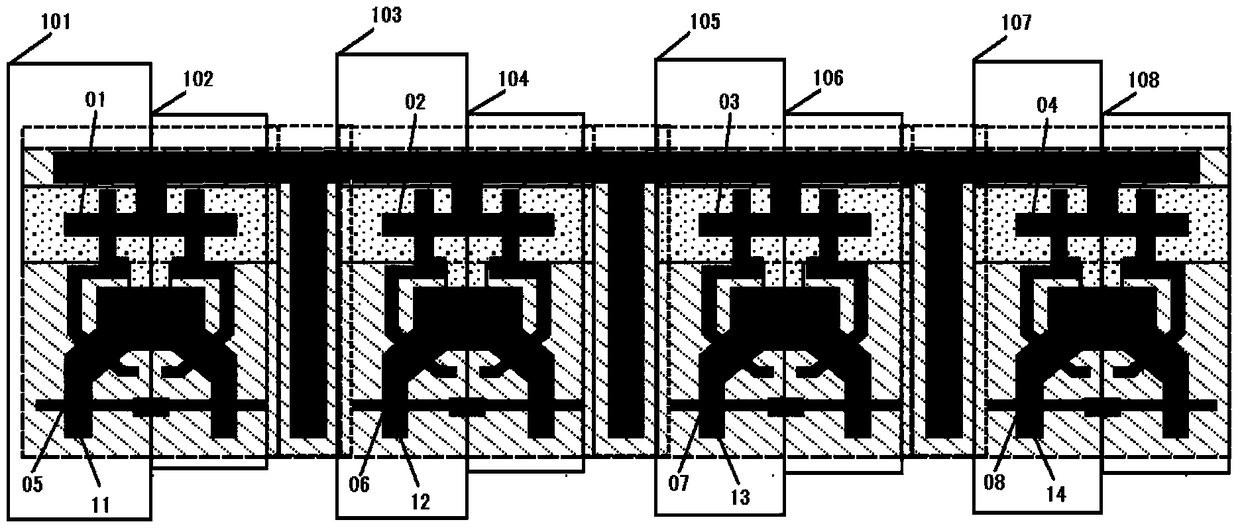

Well isolation type anti-SEU multi-node overturning storage unit layout structure

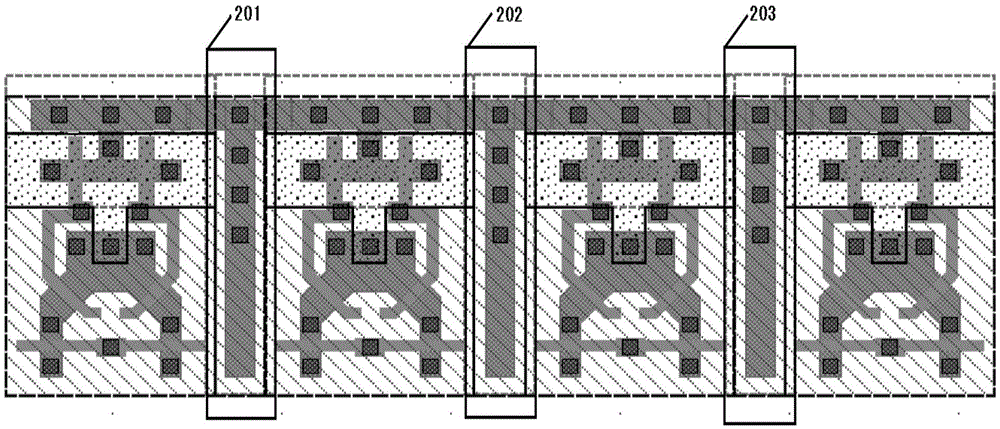

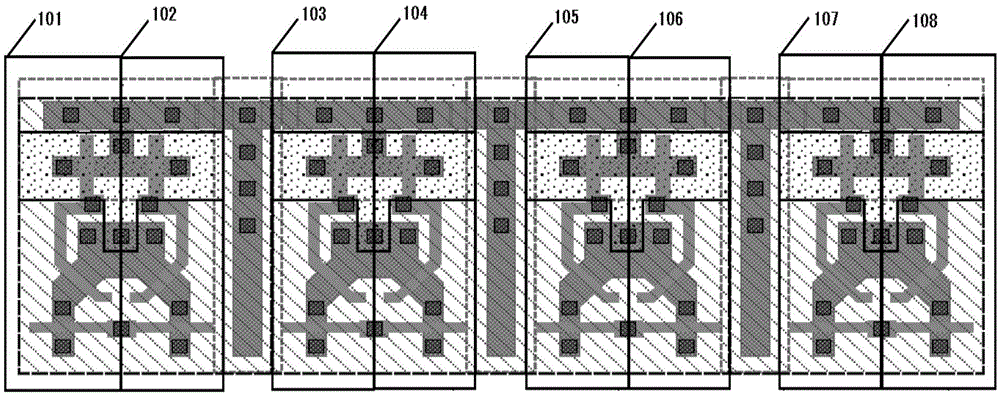

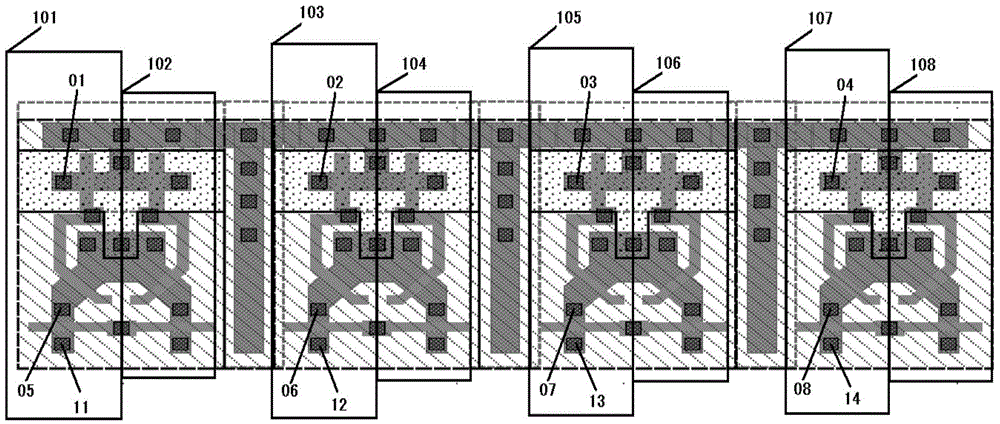

ActiveCN105609504AIncrease distanceSolve the problem of poor reliability of the flip effectSolid-state devicesSemiconductor devicesParasitic bipolar transistorEngineering

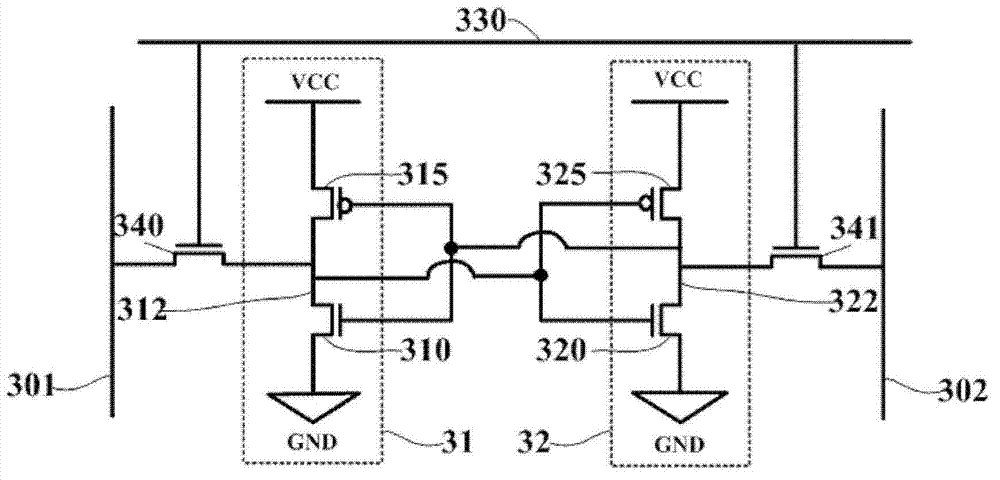

The invention relates to a well isolation type anti-SEU multi-node overturning storage unit layout structure. The well isolation type anti-SEU multi-node overturning storage unit layout structure comprises well isolation areas (201), (202), (203), DICE unit areas (101), (103), (105), (107) and DICE units (102), (104), (106), (108). The well isolation areas are arranged between two DICE unit areas in a crossed manner. According to the well isolation type anti-SEU multi-node overturning storage unit layout structure, compared with the prior art, the distance between sensitive node pairs is further increased while all the sensitive node pairs in a DICE storage unit structure are effectively separated; and the well isolation structure is also beneficial for reducing the parasitic bipolar transistor effect and charge sharing effect between the sensitive node pairs, so that multi-node overturning caused by SEU in the DICE units is greatly inhibited, and the anti-SEU performance of anti-radiation SRAM is greatly improved.

Owner:BEIJING MXTRONICS CORP +1

Method for reducing transient power consumption

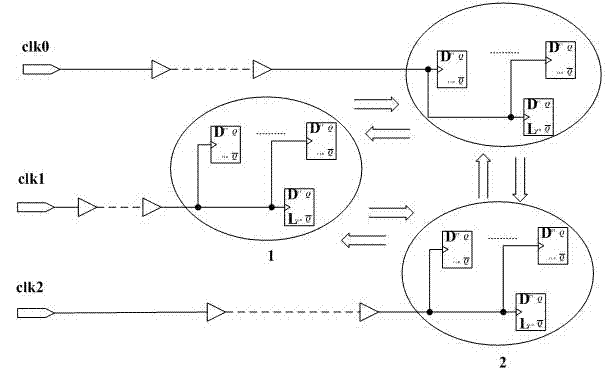

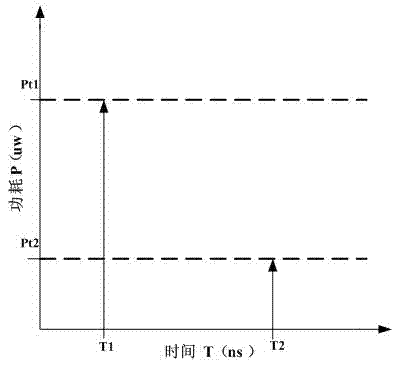

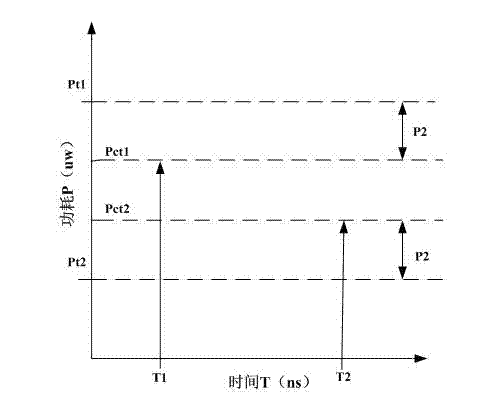

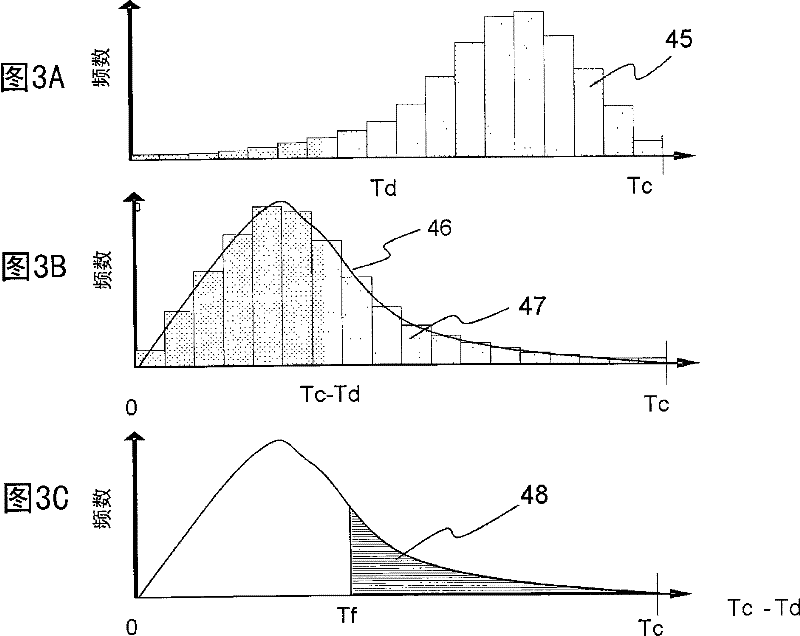

InactiveCN102479264AReduce transient power consumptionReduce the probability of flippingSpecial data processing applicationsEngineeringCircuit design

The invention relates to a method for reducing transient power consumption. The flip rate of a circuit in a peak period is reduced via interference to a clock path, so as to reduce the transient power consumption of the circuit. The implementation steps comprise analyzing the characteristics of distribution of the transient power consumption in the circuit, and determining the clock path branches; adding or removing buffers on the clock path branches to ensure that the delays of the clock path branches are different to avoid the flipping time; and repairing the time sequence resulting from the clock path delays under the interference. By adopting the method, the transient power consumption in the circuit design can be reduced effectively, and normal operation of the circuit can be ensured.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

Register circuit for preventing single particle from being overturned

InactiveCN103093824AImprove radiation resistanceReduce the probability of flippingDigital storageProcessor registerComputer science

The invention discloses a register circuit for preventing a single particle from being overturned. The register circuit comprises a first-grade main latch, a second-grade secondary latch, a first inverter and a second inverter. The first-grade main latch is provided with two data inputs which are respectively selected form a data input di of a register and a complementary data input dib of the register; the first-grade main latch is provided with one clock input ck; the first-grade main latch is provided with two data outputs which respectively comprise latching data ql and complementary latching data qlb; the second-grade secondary latch is provided with two data inputs which are respectively selected form a data output ql and a complementary data output qlb of the first-grade main latch; the second-grade secondary latch is provided with one clock input ck and is selected from a complementary clock input ckn of the register; and the second-grade secondary latch is provided with two data outputs which respectively comprise registering data rq and complementary registering data rqb of the register. With the adoption of the register circuit disclosed by the invention, the anti-radiation performance of the register is obviously enhanced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Static random access memory unit resisting single event upset

InactiveCN103093809AImprove radiation resistanceIncrease coupling timeDigital storageCouplingEngineering

The invention discloses a static random access memory unit resisting single event upset. The static random memory unit resisting the single event upset comprises a first differential series voltage switch logic unit, a second differential series voltage switch logic unit, a first PMOS (P-channel Metal Oxide Semiconductor) transistor resistor, a second PMOS transistor resistor, a first access NMOS (N-channel Metal Oxide Semiconductor) transistor and a second access NMOS transistor, wherein the first access NMOS transistor is connected with the first differential series voltage switch logic unit, the second access NMOS transistor is connected with the second differential series voltage switch logic unit, the first PMOS transistor resistor and the second PMOS transistor resistor are connected between the first differential series voltage switch logic unit and the second differential series voltage switch logic unit in parallel, and the first differential series voltage switch logic unit and the second differential series voltage switch logic unit constitute a cross-coupling latch.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

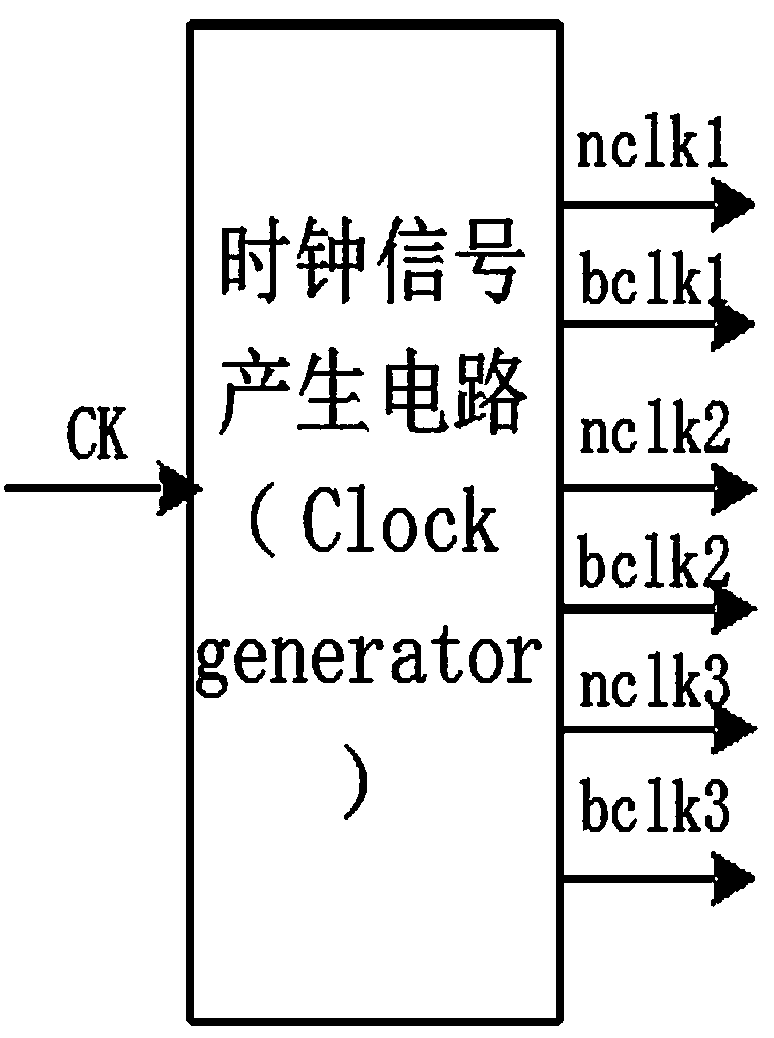

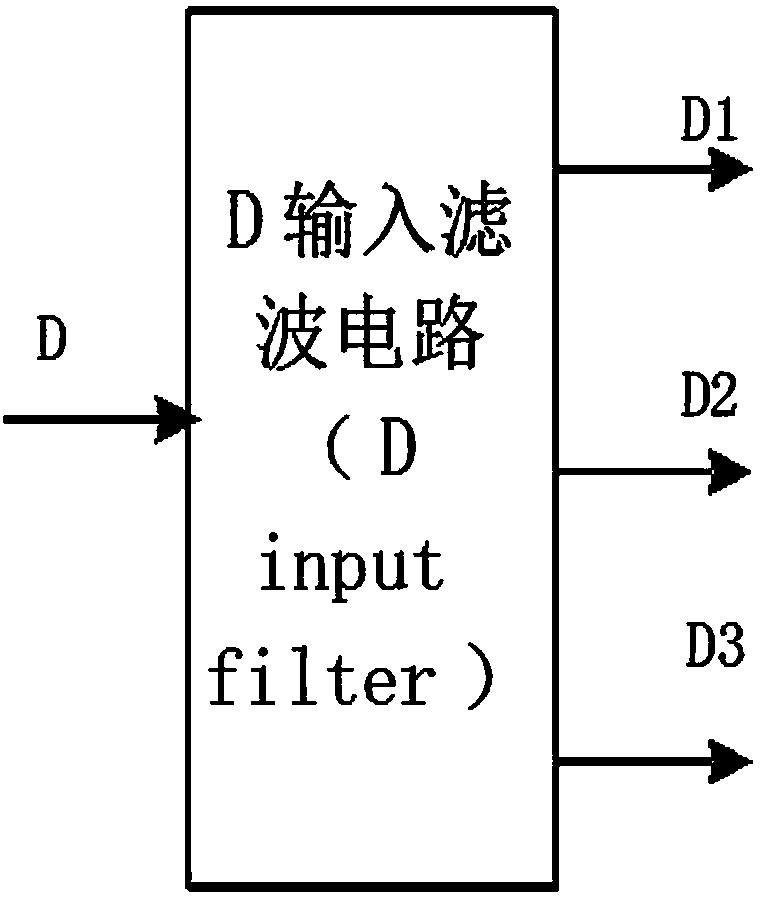

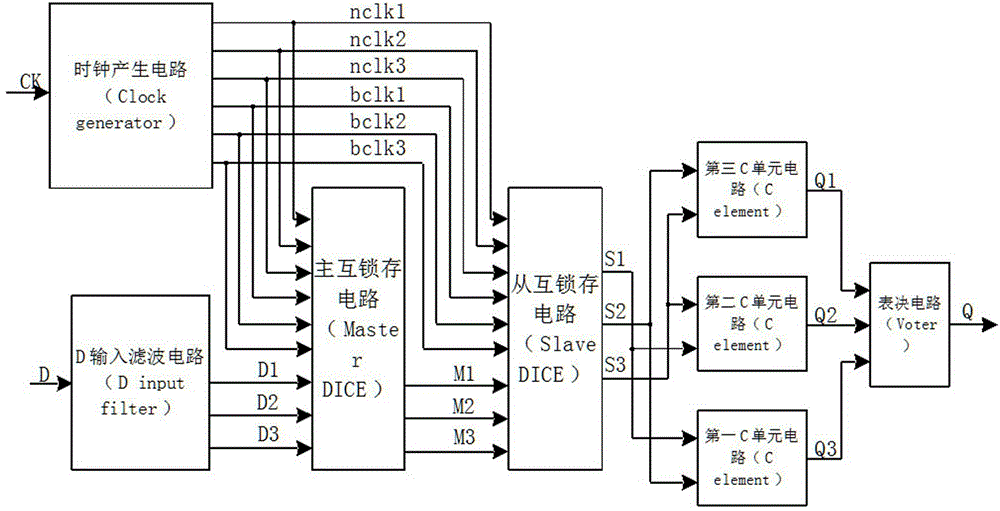

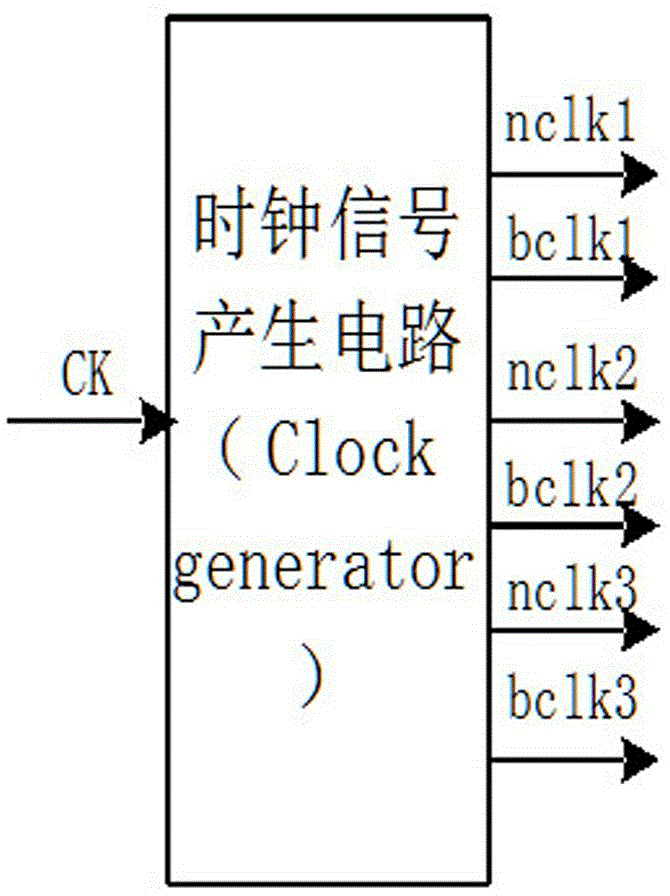

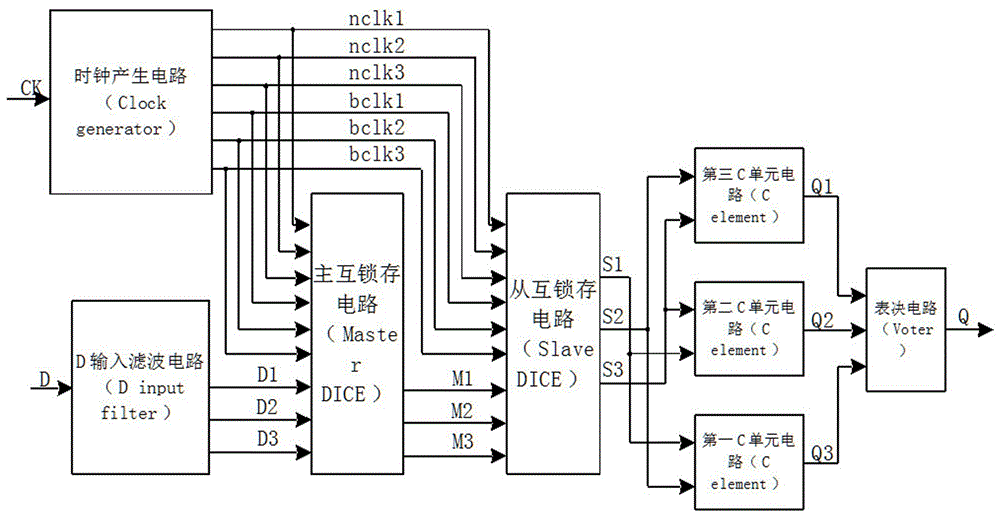

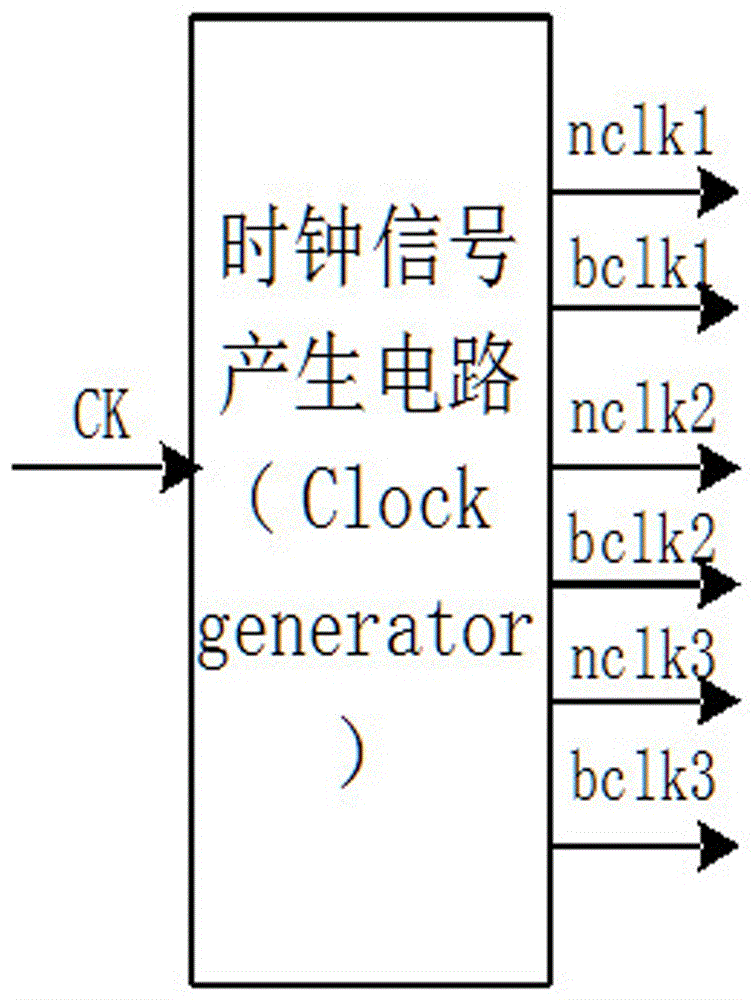

Anti-radiation D flip-flop circuit based on three mutual-latching units

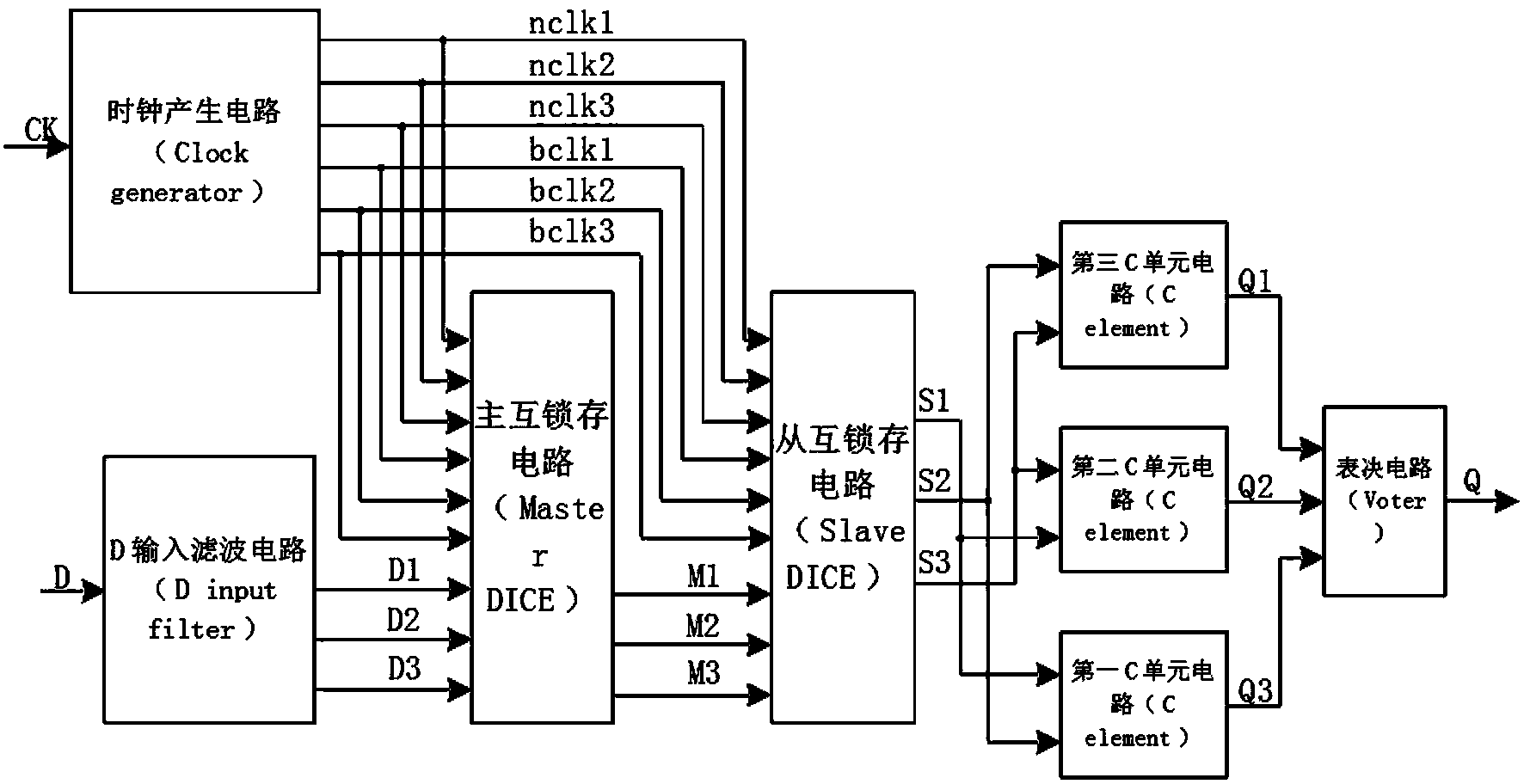

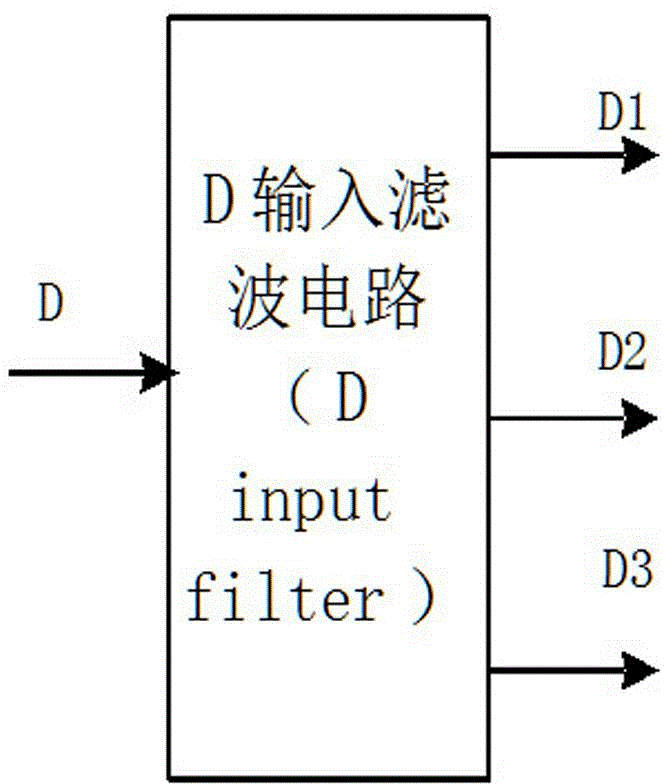

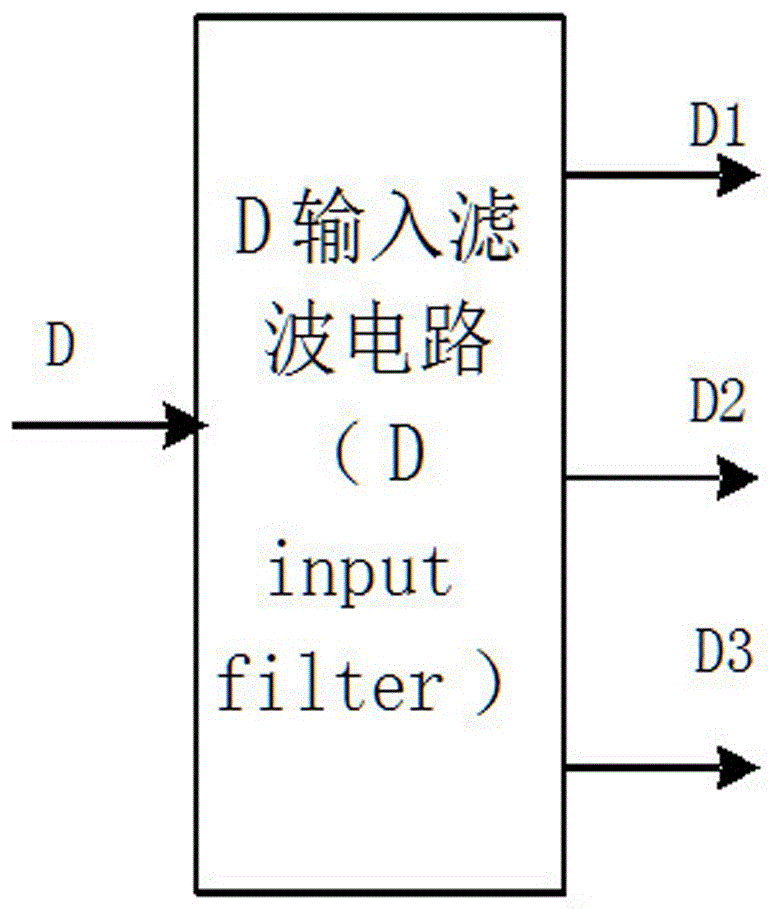

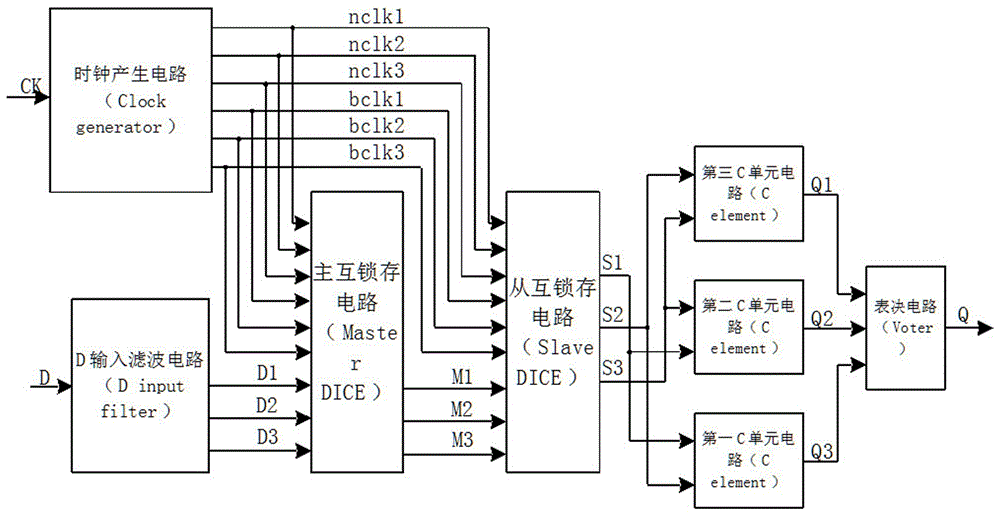

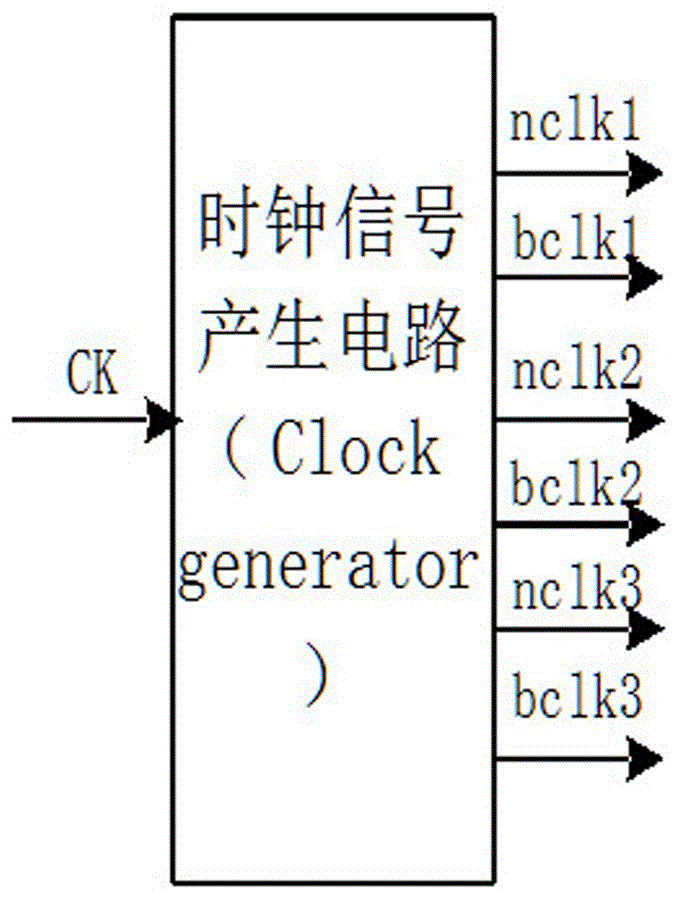

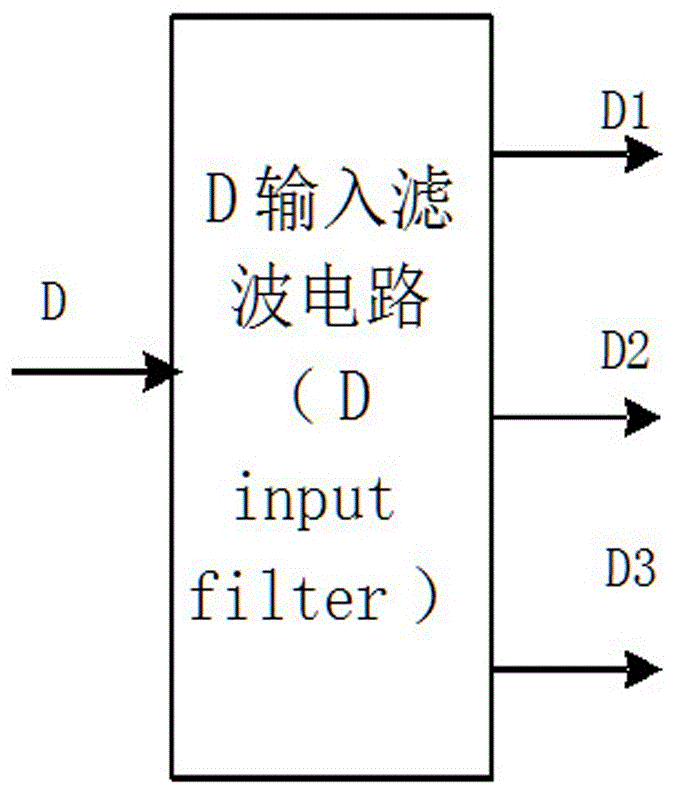

InactiveCN104363005AStable outputStable and reliable outputElectric pulse generator circuitsExternal dataData signal

The invention discloses an anti-radiation D flip-flop circuit based on three mutual-latching units. The anti-radiation D flip-flop circuit comprises a clock signal generation circuit, a D input filter circuit, C unit circuits, a voting circuit, a primary mutual-latching circuit and a secondary mutual-latching circuit. The C unit circuits include a first C unit circuit, a second C unit circuit and a third C unit circuit. Clock signals are generated after an external clock signal CK passes through the clock signal generation circuit, data signals are generated after an external data signal D passes through the D input filter circuit, data signals, output after the clock signals and the data signals pass through the primary mutual-latching circuit, the secondary mutual-latching circuit and the C unit circuits, passes through the voting circuit to output an output signal Q of a whole flip-flop. The anti-radiation D flip-flop circuit has the advantages that a three mutual-latching circuit reinforcement technology is adopted, output stability and reliability of the whole D flip-flop circuit can be guaranteed in case of overturning of the D flip-flop circuit due to interference such as radiation, and anti-radiation capability of the D flip-flop circuit is greatly improved.

Owner:ANQING NORMAL UNIV

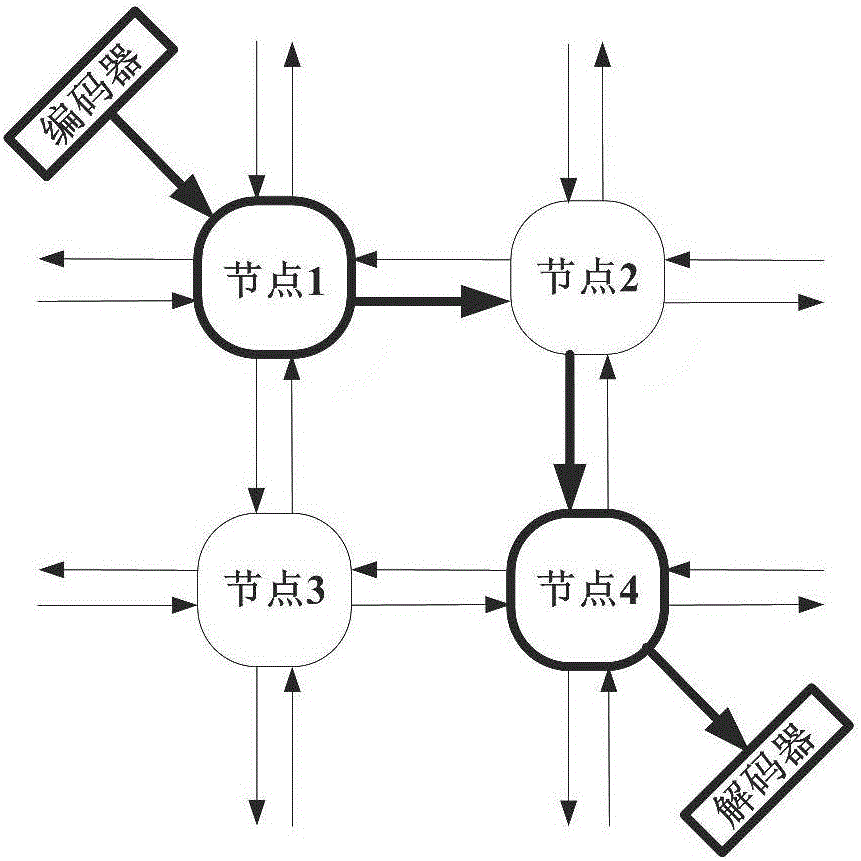

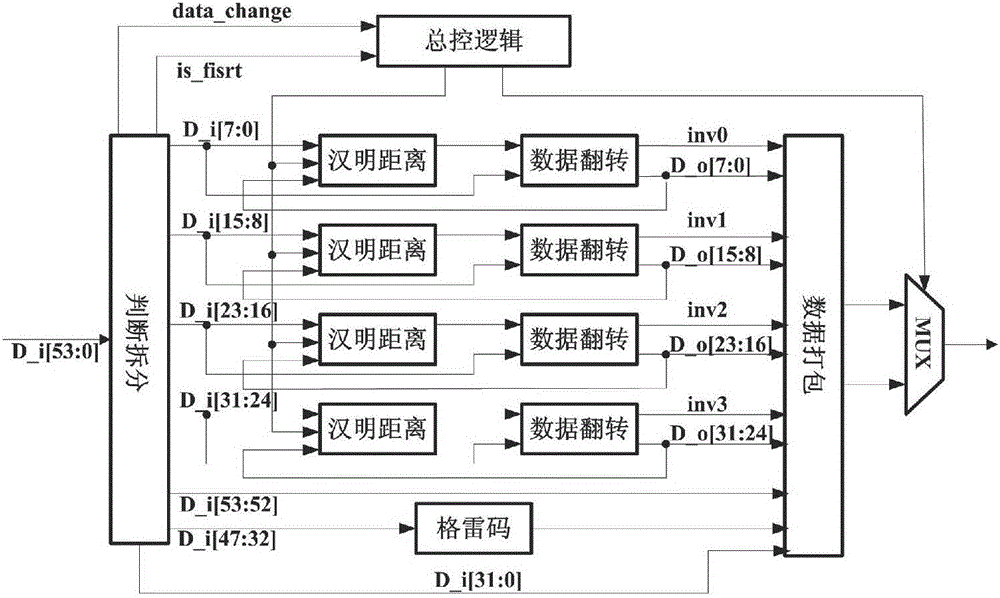

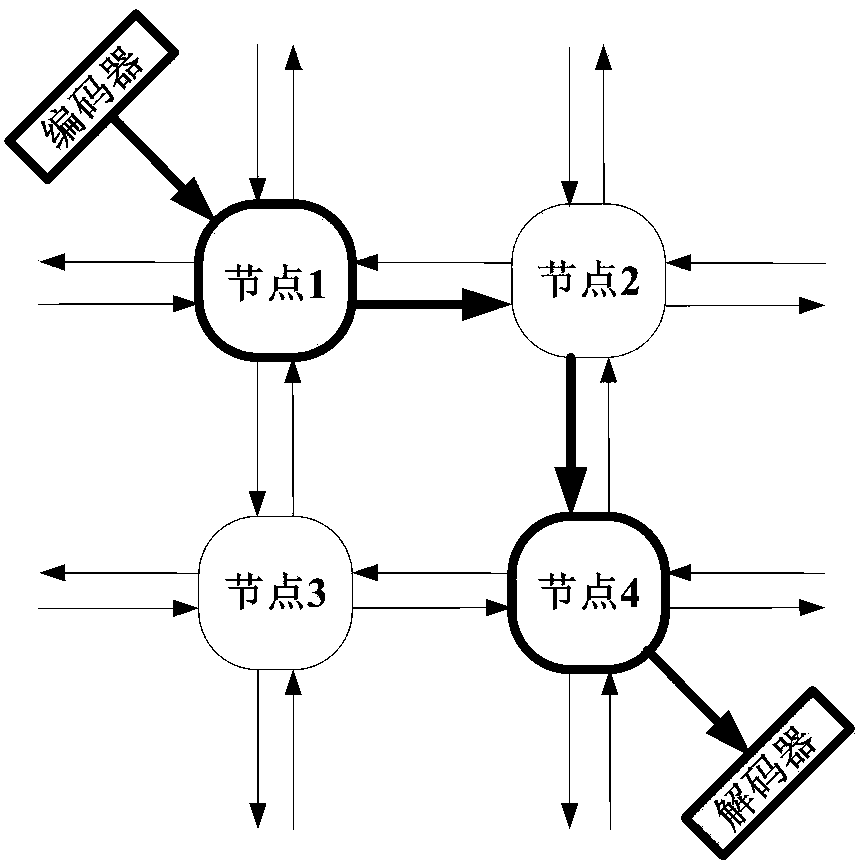

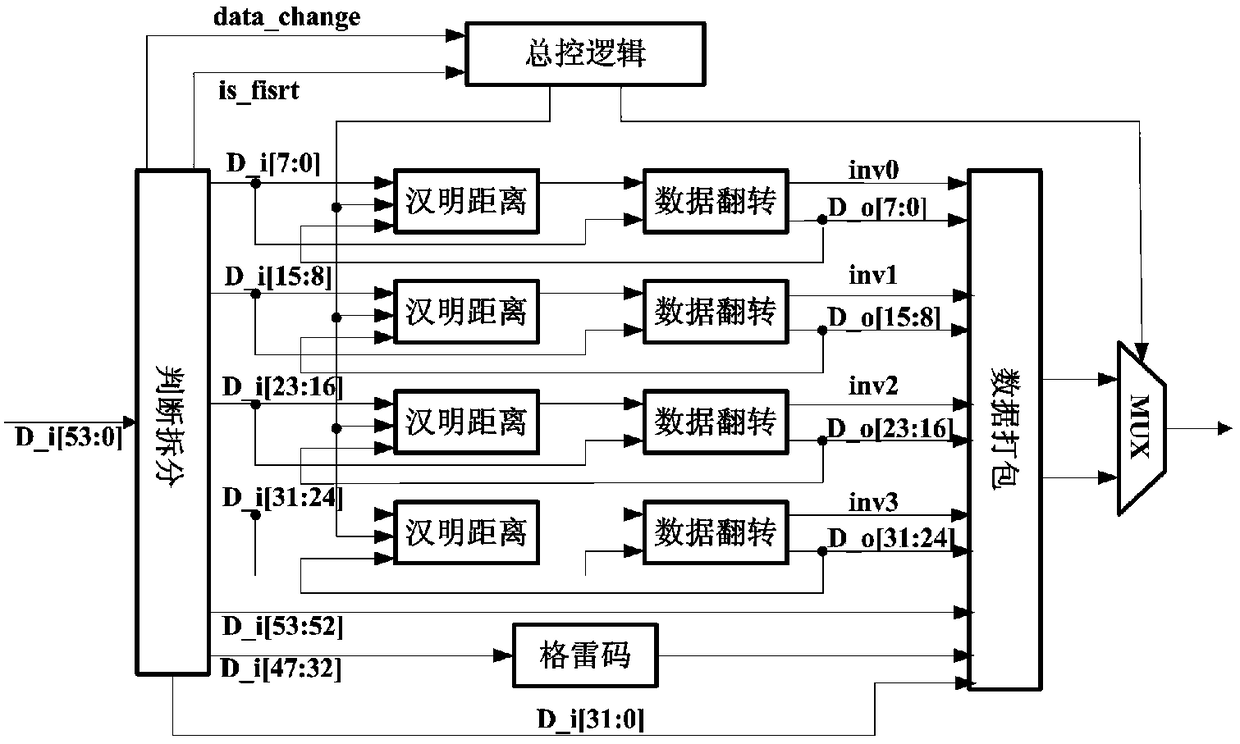

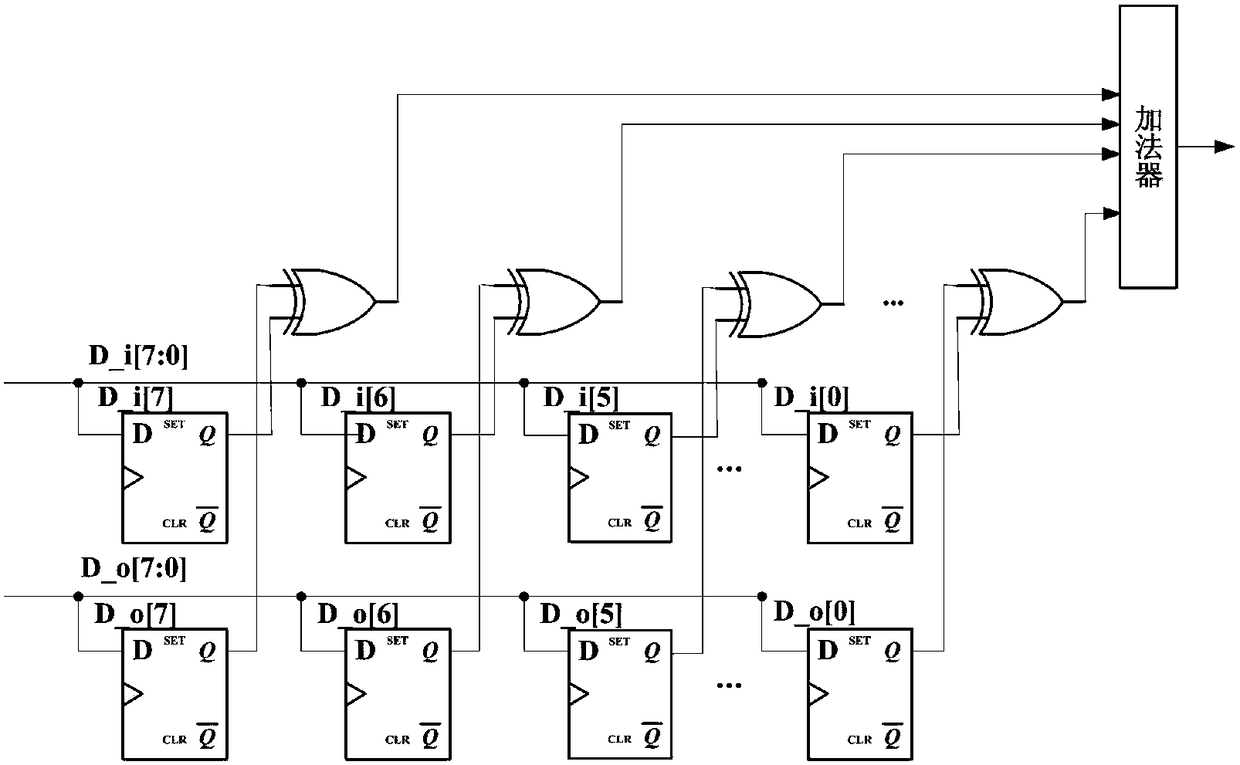

Encoding and decoding circuit based on low power consumption combination applied to network on chip and encoding and decoding method thereof

ActiveCN106059592AReduce power consumptionReduce the probability of flippingCode conversionData encodingHamming distance

The invention discloses an encoding and decoding circuit based on low power consumption combination applied to a network on chip and an encoding and decoding method thereof. The encoding and decoding circuit is characterized in that an encoding circuit is arranged at the input end of a source node, and a decoding circuit is arranged at the output end of a destination node; the encoding circuit comprises an encoding judgment splitting module, four Hamming distance calculating modules, four data turning modules, a gray code encoding module, and a data encoding packaging module; and the decoding circuit comprises a decoding judgment splitting module, four data anti-turning modules, a gray code decoding module, and a data decoding packaging module. The turning rate of transmitted data can be reduced, so that the power consumption of the whole network on chip is reduced, and correct data transmission is ensured.

Owner:黄山市开发投资集团有限公司

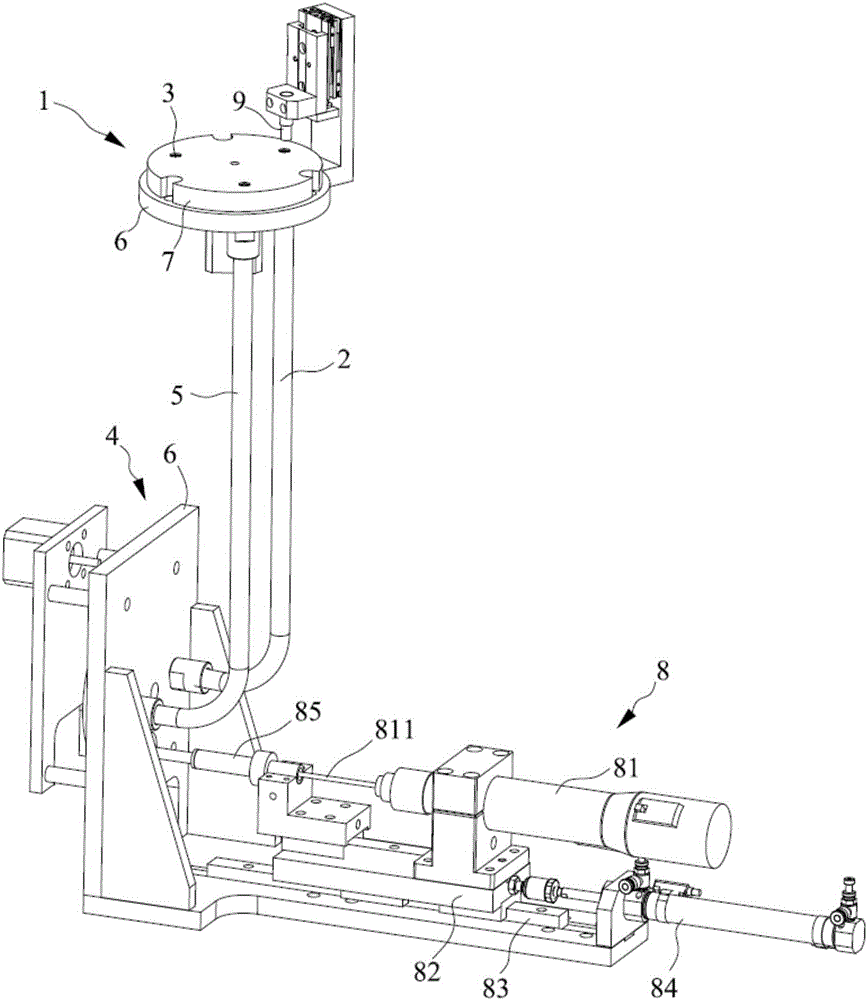

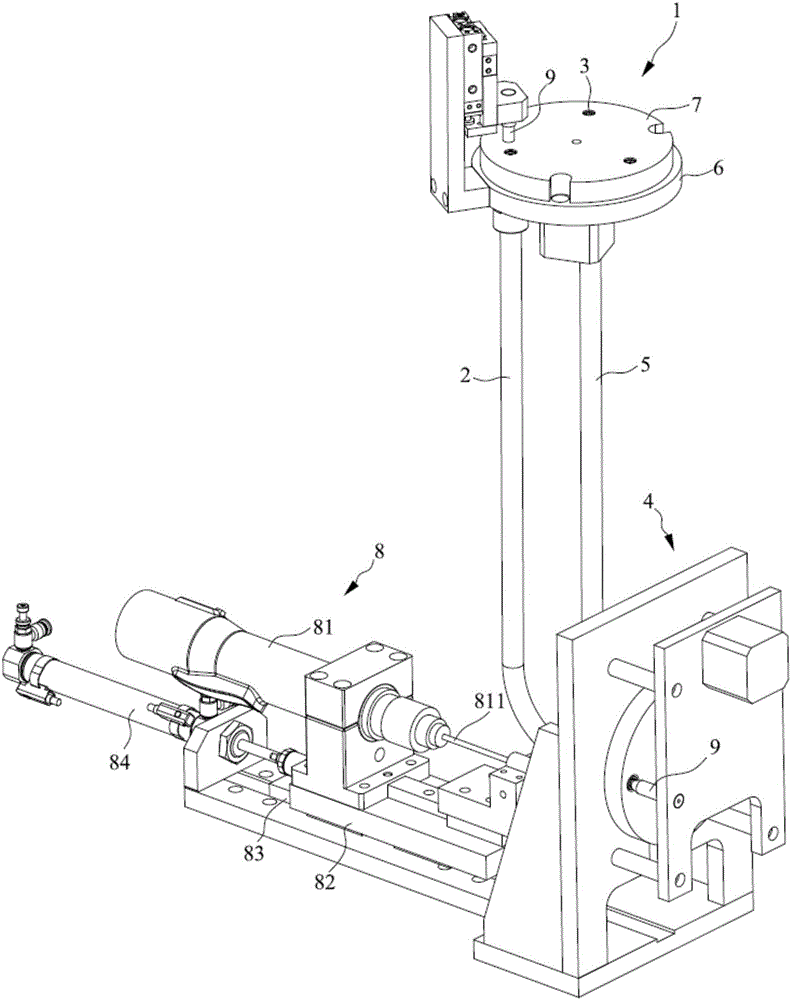

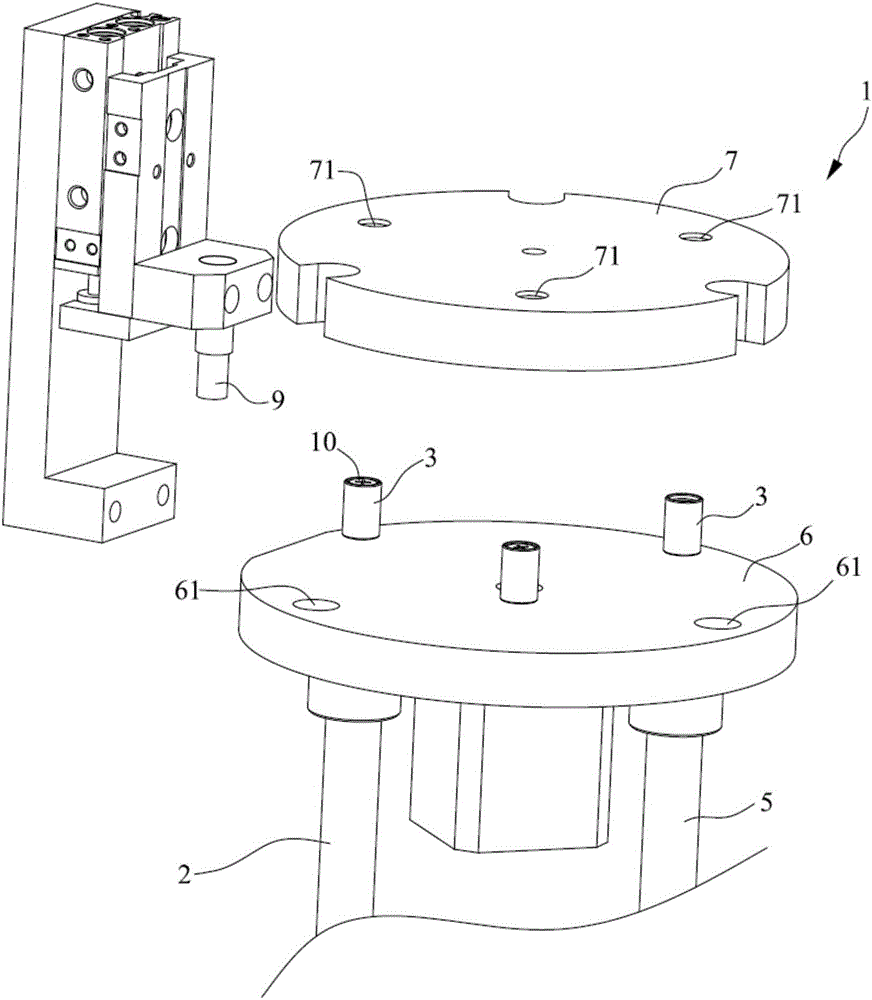

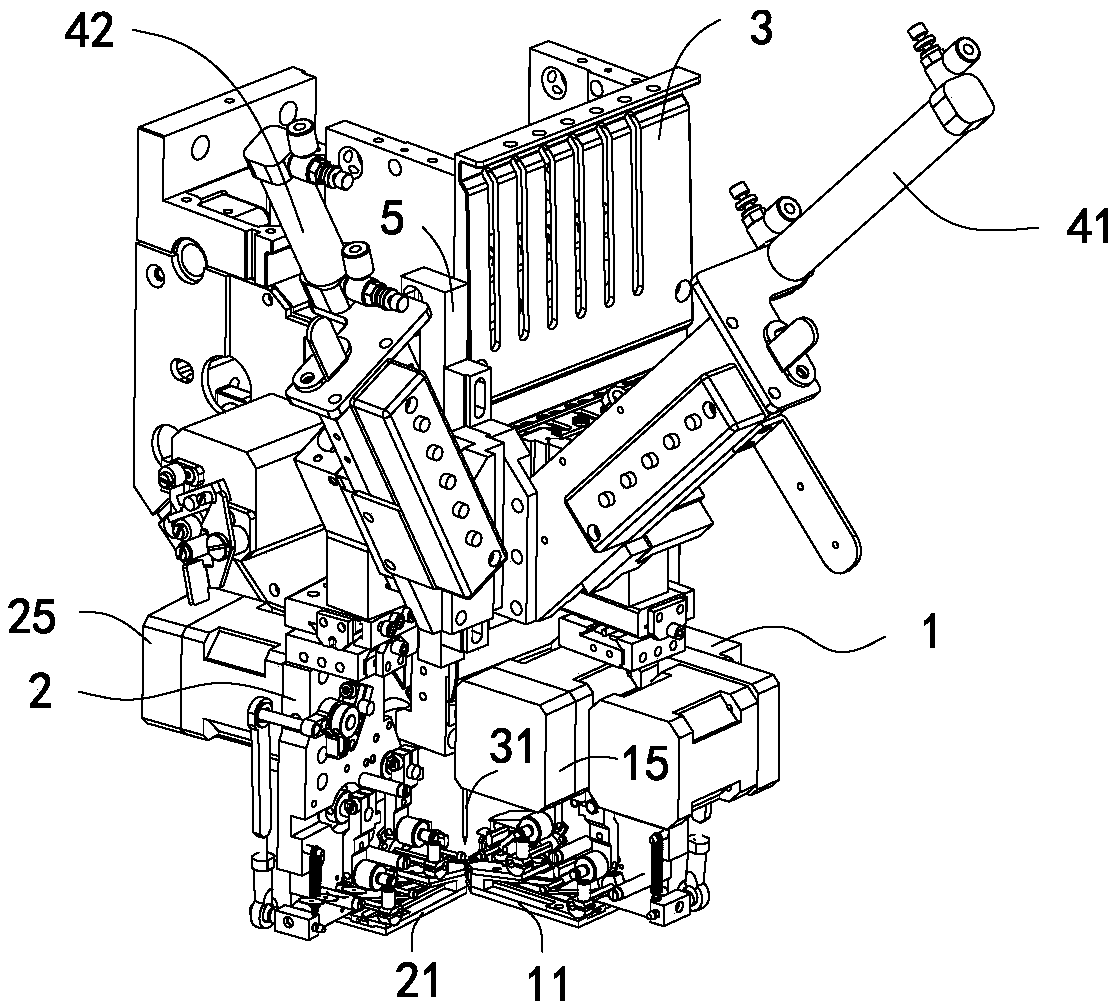

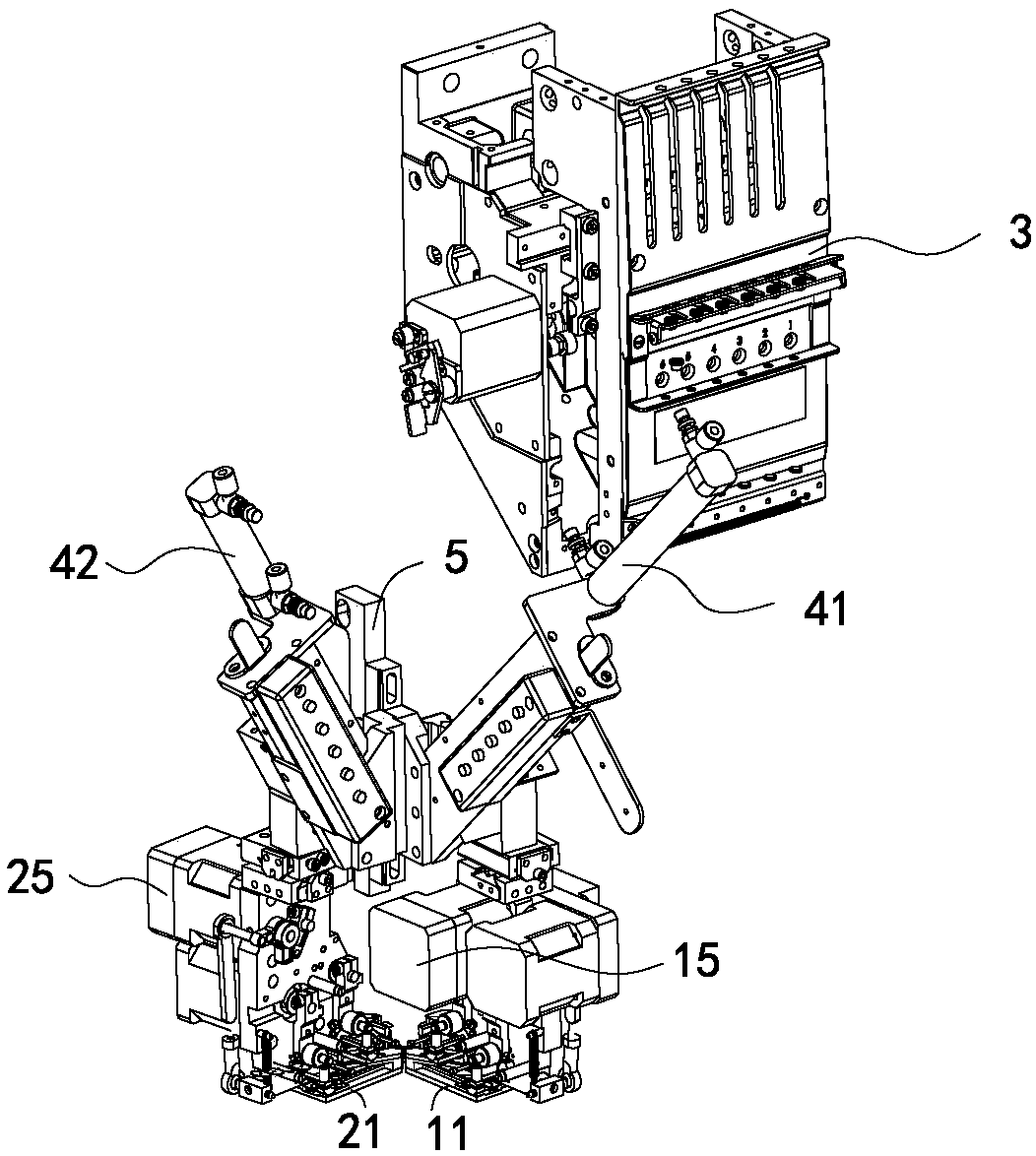

Screw conveying mechanism

ActiveCN106514189AReduce the probability of flippingLow failure rateMetal working apparatusEngineeringMechanical engineering

The invention discloses a screw conveying mechanism. The mechanism comprises a feeding device, a feeding pipe and conveying pieces for conveying screws; material plate holes communicating with the feeding pipe are formed in the feeding device; the conveying pieces can enter the feeding pipe via the material plate holes and can move along the feeding pipe; each conveying piece comprises an accommodating cavity; the screws are fixed in the accommodating cavities; and the conveying pieces cannot be turned over when moving in the feeding pipe due to the ratio of the longitudinal size to the transverse size of the conveying pieces. The conveying pieces can be conveyed in a fixed direction, and the screws are fixed in the conveying pieces, so that the screws can also be conveyed in the fixed direction. The screw conveying mechanism is suitable for conveying of the screws in any models, all that is required is to change the corresponding conveying pieces according to the screws, the conveying effect is good, and the universality is high.

Owner:SHENZHEN SKYWORTH RGB ELECTRONICS CO LTD +1

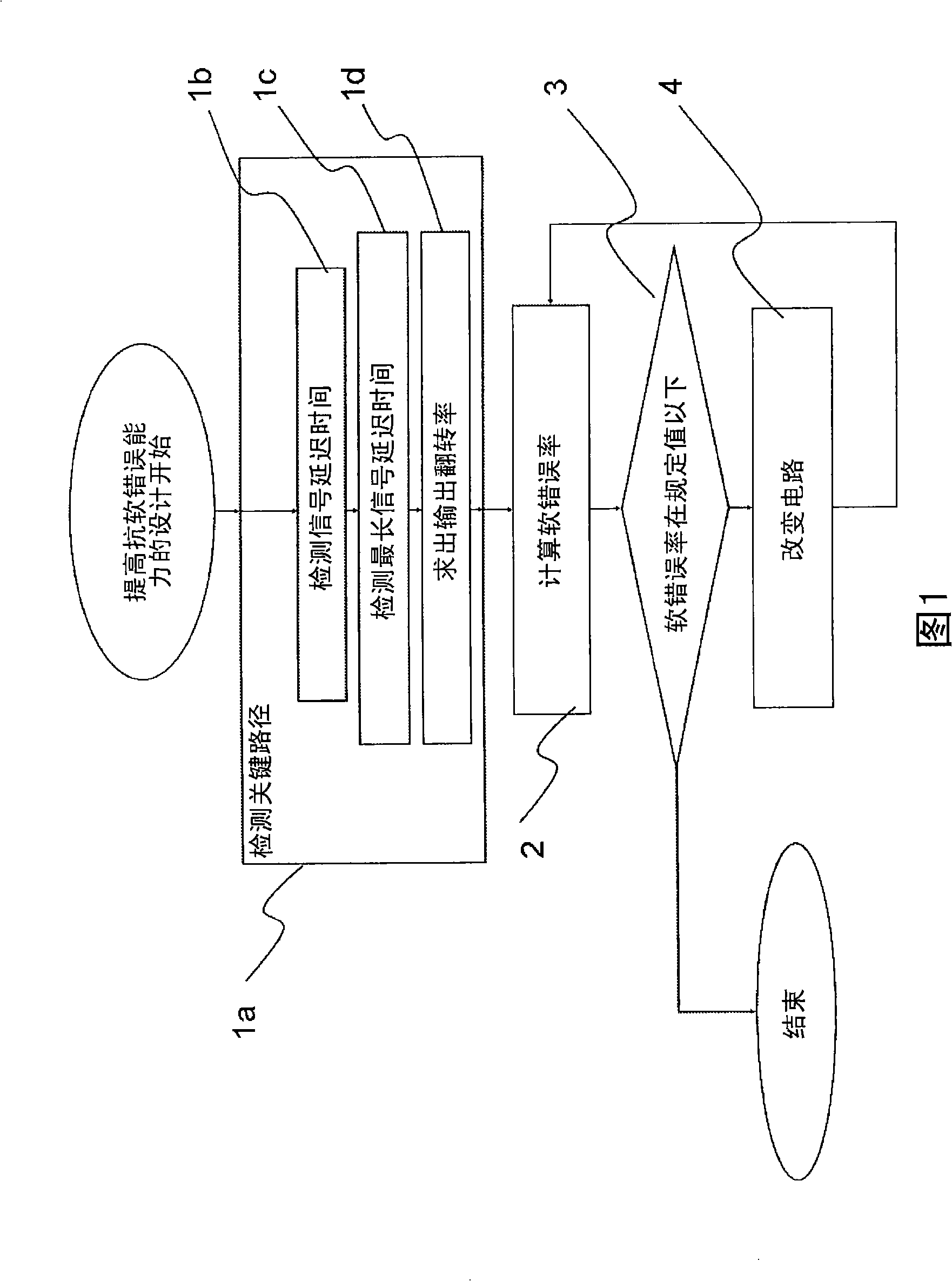

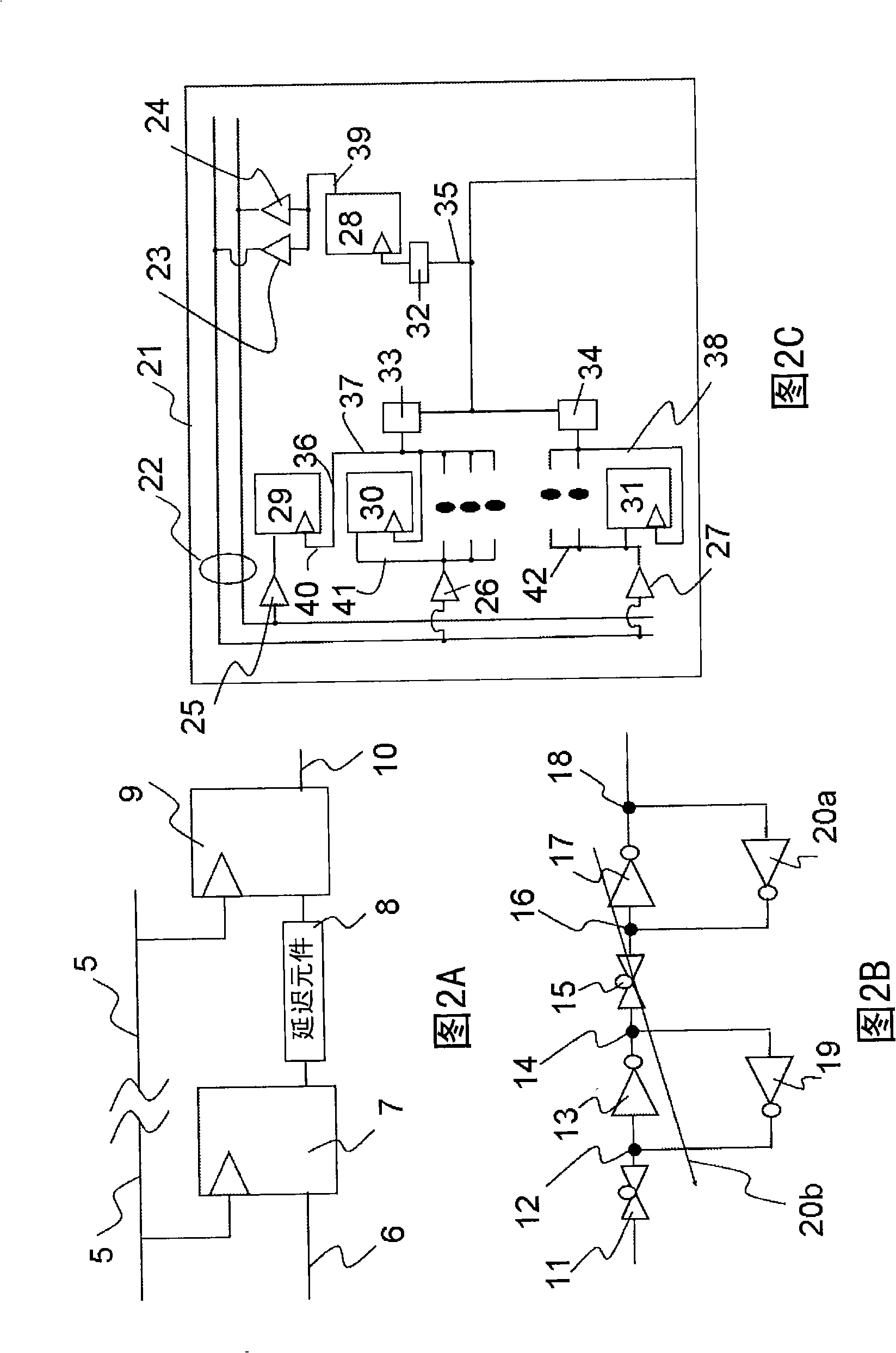

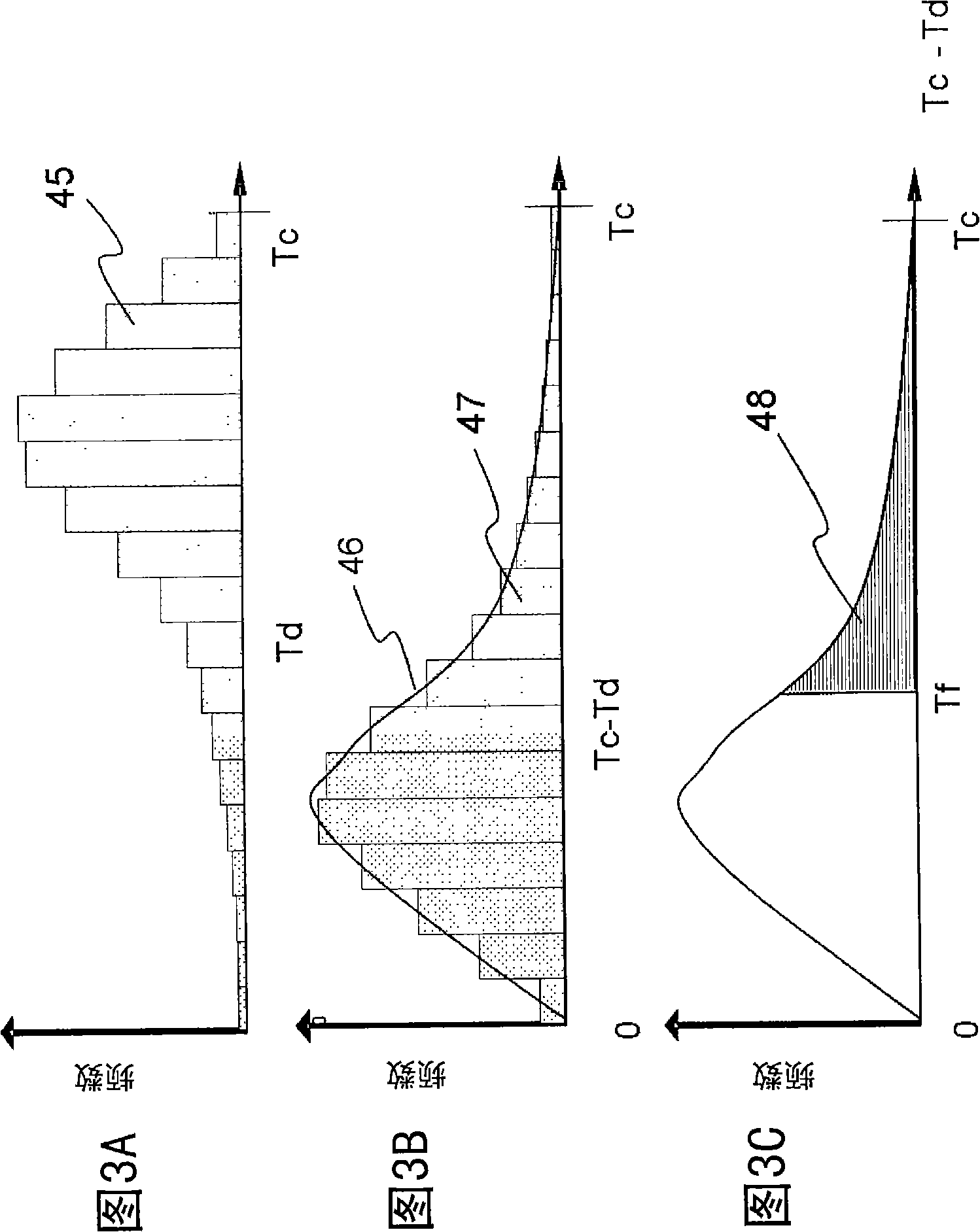

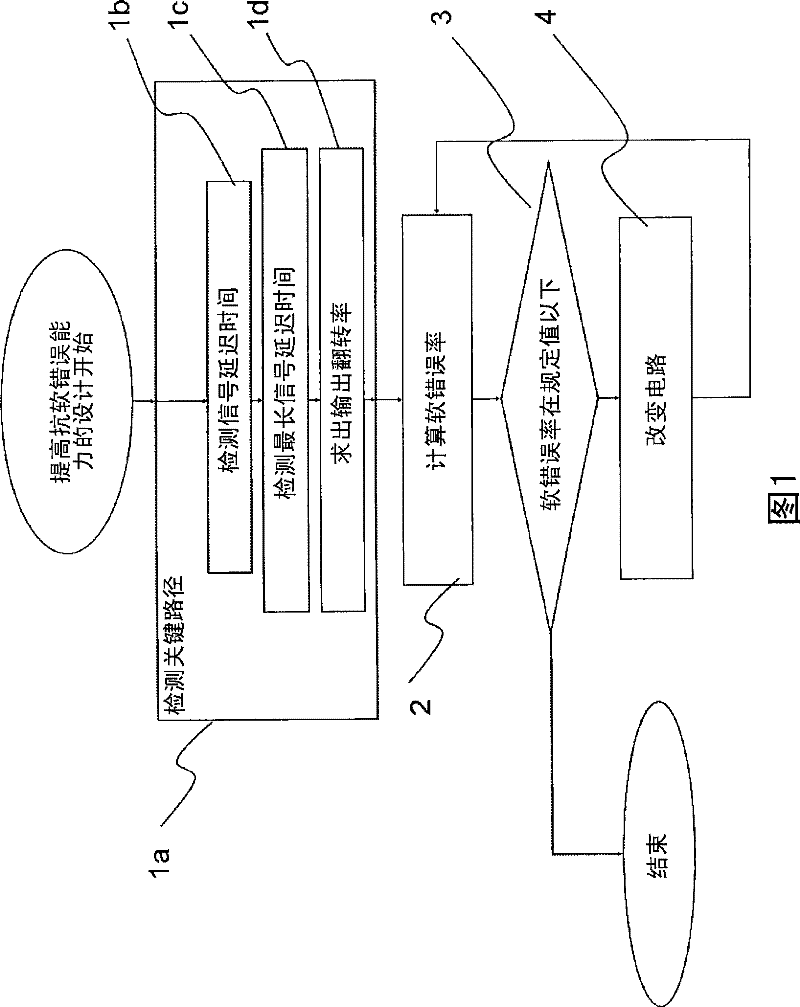

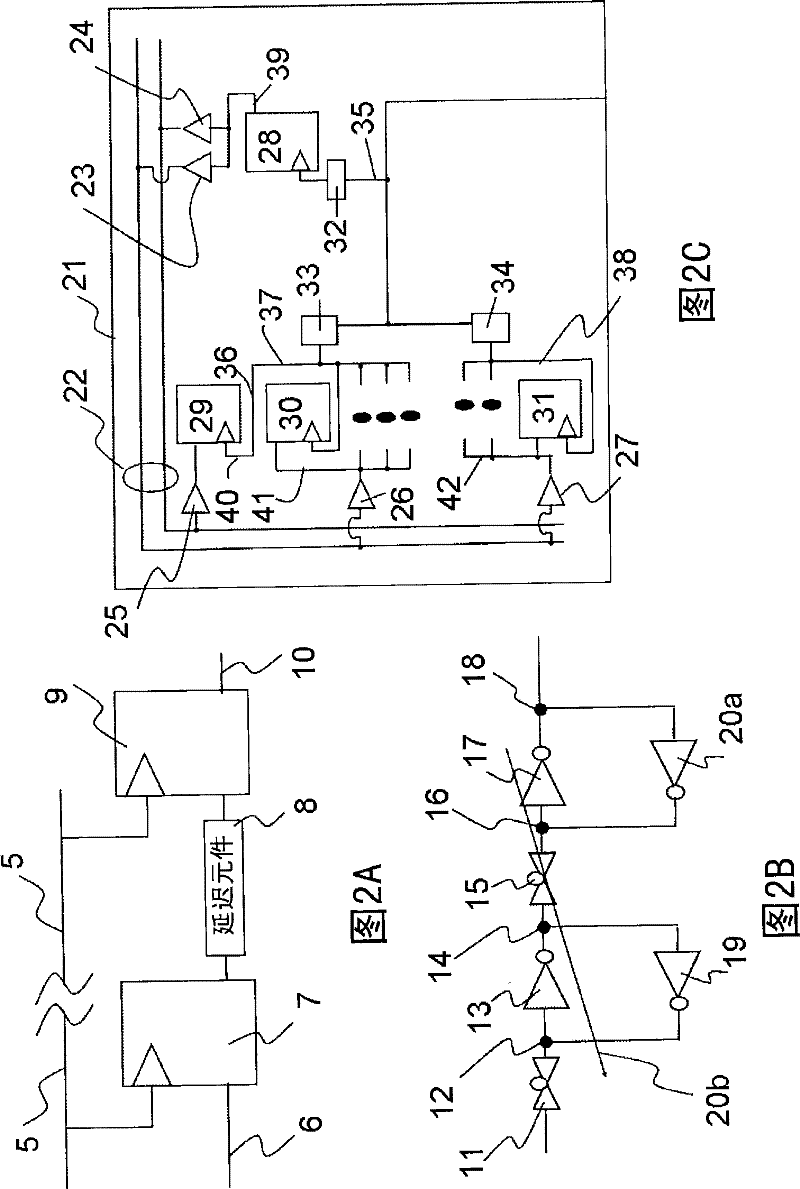

Signal transmission circuit, semiconductor element including the same, design method of the semiconductor circuit device and CAD device for implementing the method

InactiveCN101273357AImprove performanceImprove resistance to soft errorsReliability increasing modificationsSolid-state devicesEngineeringCritical path method

Provided is a semiconductor circuit device in which soft error resistance is enhanced while assuring the high-speed operation of an entire LSI circuit. A CAD device includes: means for identifying a signal transmission time of each signal transmission circuit of the LSI circuit; means for identifying an output inversion ratio upon radiation exposure of a flip-flop circuit of each signal transmission circuit; means for identifying a signal transmission circuit as a critical path; means for calculating a soft error ratio of the entire LSI circuit according to the signal transmission time, the output inversion ratio, and the clock cycle; and means for lowing the soft error ratio of the entire LSI circuit without changing the signal transmission time of the signal transmission circuit as the critical path when a predetermined soft error ratio is lower than the soft error ratio of the entire LSI circuit.

Owner:SOCIONEXT INC

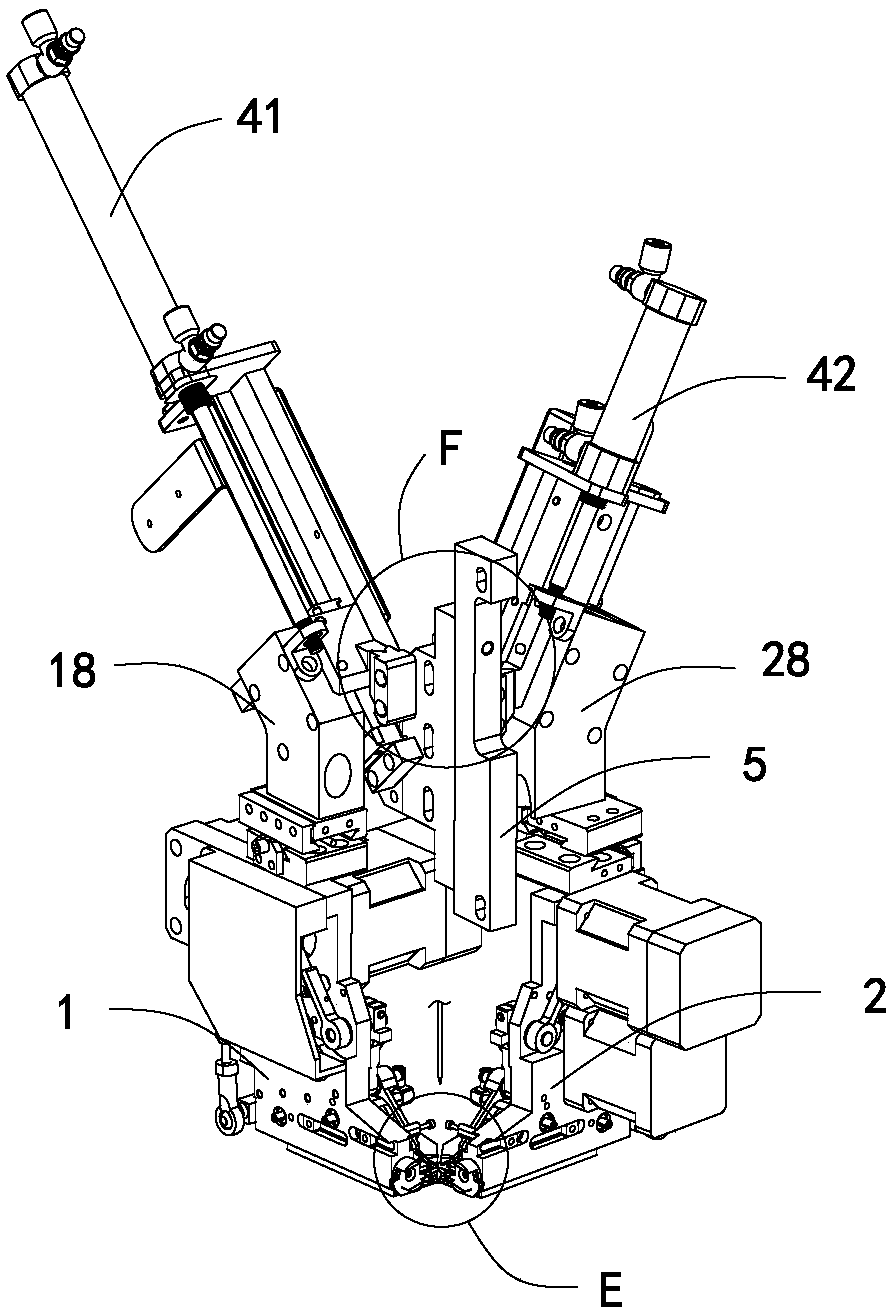

Multi-sequin conveying device and embroidery machine

PendingCN108411510AImprove efficiencyOmit rise timeAutomatic machinesAuxillary devicesEngineeringMechanical engineering

The invention discloses a multi-sequin conveying device and belongs to the field of embroidery technical equipment. The multi-sequin conveying device comprises two sequin conveyors, wherein each sequin conveyor comprises a conveying passage for conveying sequins, each conveying passage comprises a sequin outlet, and movement positions of each sequin conveyor comprise a working position and a lifting position; in a working state of sequin embroidery, the sequin conveyors are in working positions to convey the sequins to a needle bar; when the multi-sequin conveying device is in the working state of sequin embroidery, the two sequin conveyors are simultaneously in the working positions corresponding to the same needle bar, and The corresponding sequin outlet of the corresponding conveying passage of each sequin conveyor is located below the same needle bar. In addition, the invention further discloses an embroidery machine adopting the multi-sequin conveying device. The multi-sequin conveying device and the embroidery machine have the advantage that the embroidery efficiency of sequin embroidery can be remarkably increased. The multi-sequin conveying device and the embroidery machineare mainly applied to a sequin embroidery process in a embroidery process.

Owner:HUZHOU GUANJIONG MECHANICAL & ELECTRICAL TECH CO LTD

Radiation-resistant hardened trigger circuit based on complex three-interacting latch unit

InactiveCN104410389AStable outputImprove reliabilityElectric pulse generator circuitsRadiation resistantExternal data

The invention discloses a radiation-resistant hardened trigger circuit based on a complex three-interacting latch unit; the radiation-resistant hardened trigger circuit is composed of a clock signal generation circuit, a D input filter circuit, a C unit circuit, a voting circuit, a main interlocking latch circuit and a slave interlocking latch circuit; the C unit circuit comprises a first C unit circuit, a second C unit circuit and a third C unit circuit; a clock signal, generated from an external clock signal CK through the clock signal generation circuit, and a data signal, generated from an external data signal D through the D input filter circuit, pass through the main interlocking latch circuit, the slave interlocking latch circuit and the C unit circuit; and then, an output signal Q of a whole trigger is output through the voting circuit. According to the technical scheme provided by the invention, by adopting a technology for hardening a trigger using a complex three-interacting latch circuit, output of the whole trigger circuit can be ensured to be steady when the trigger circuit is turned due to the fact that the trigger circuit is subjected to interferences, such as radiation; therefore, the reliability is increased; and the radiation-resistance capability of the trigger circuit is greatly increased.

Owner:ANQING NORMAL UNIV

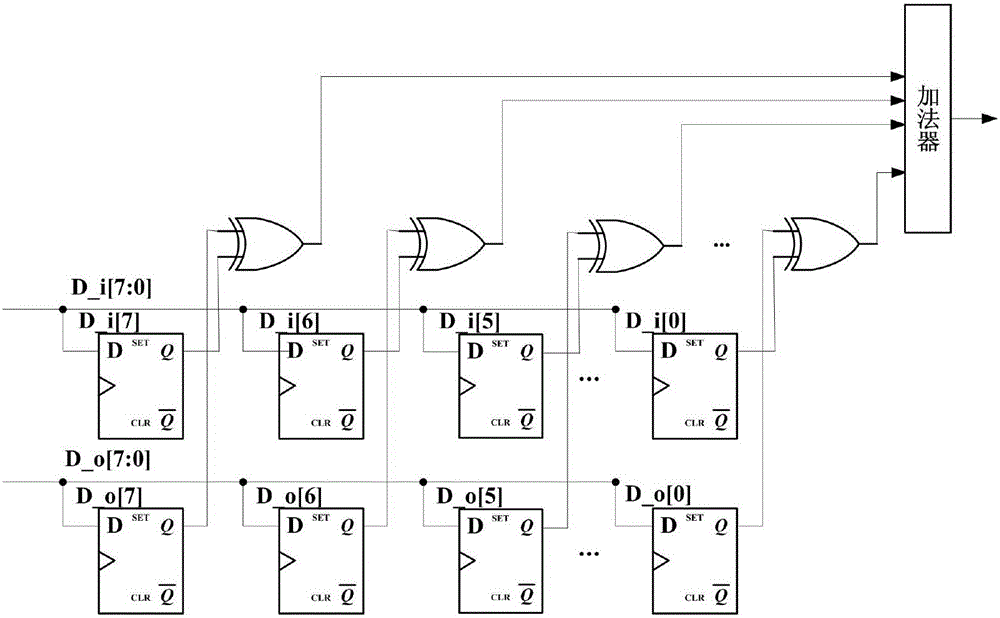

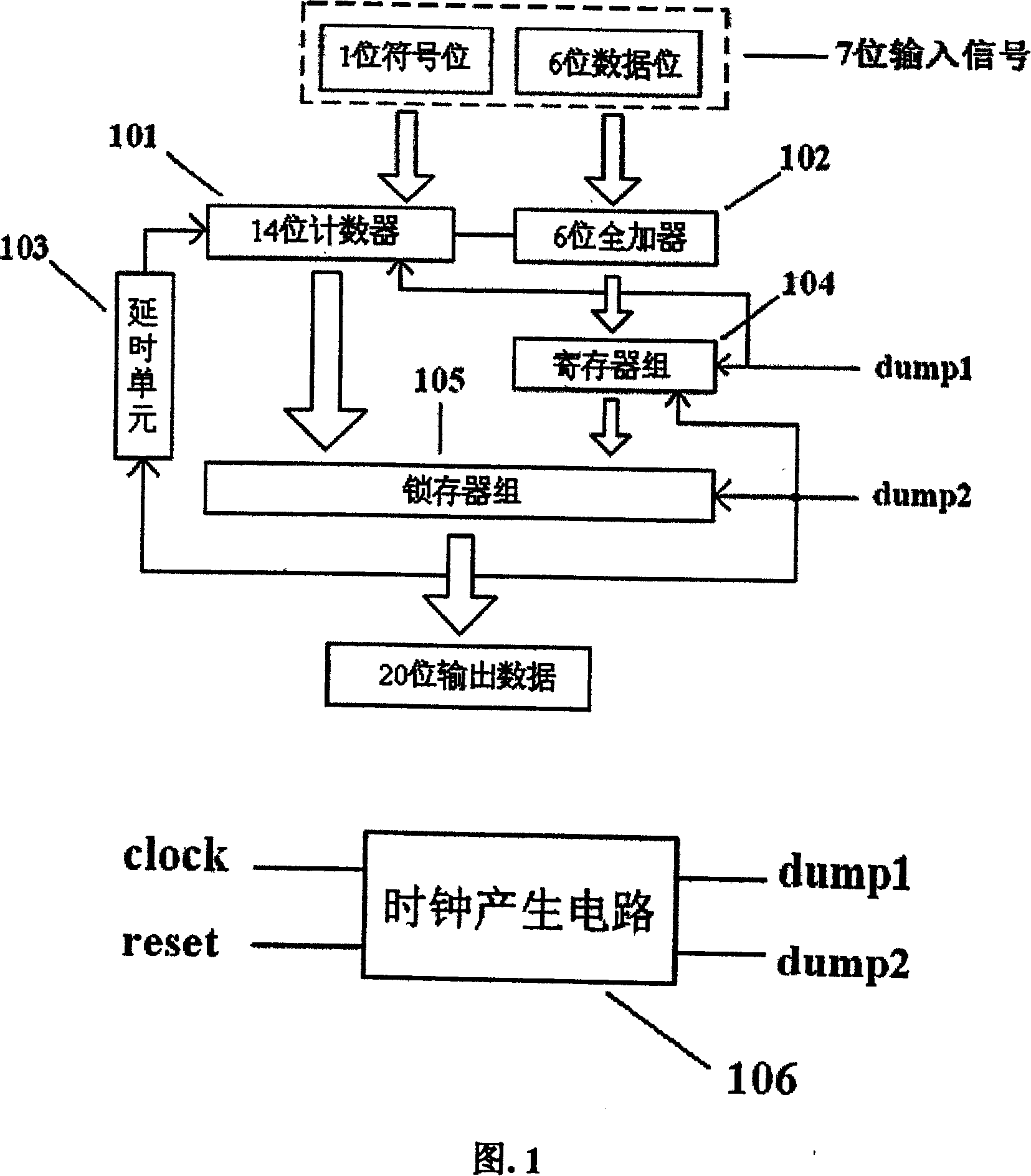

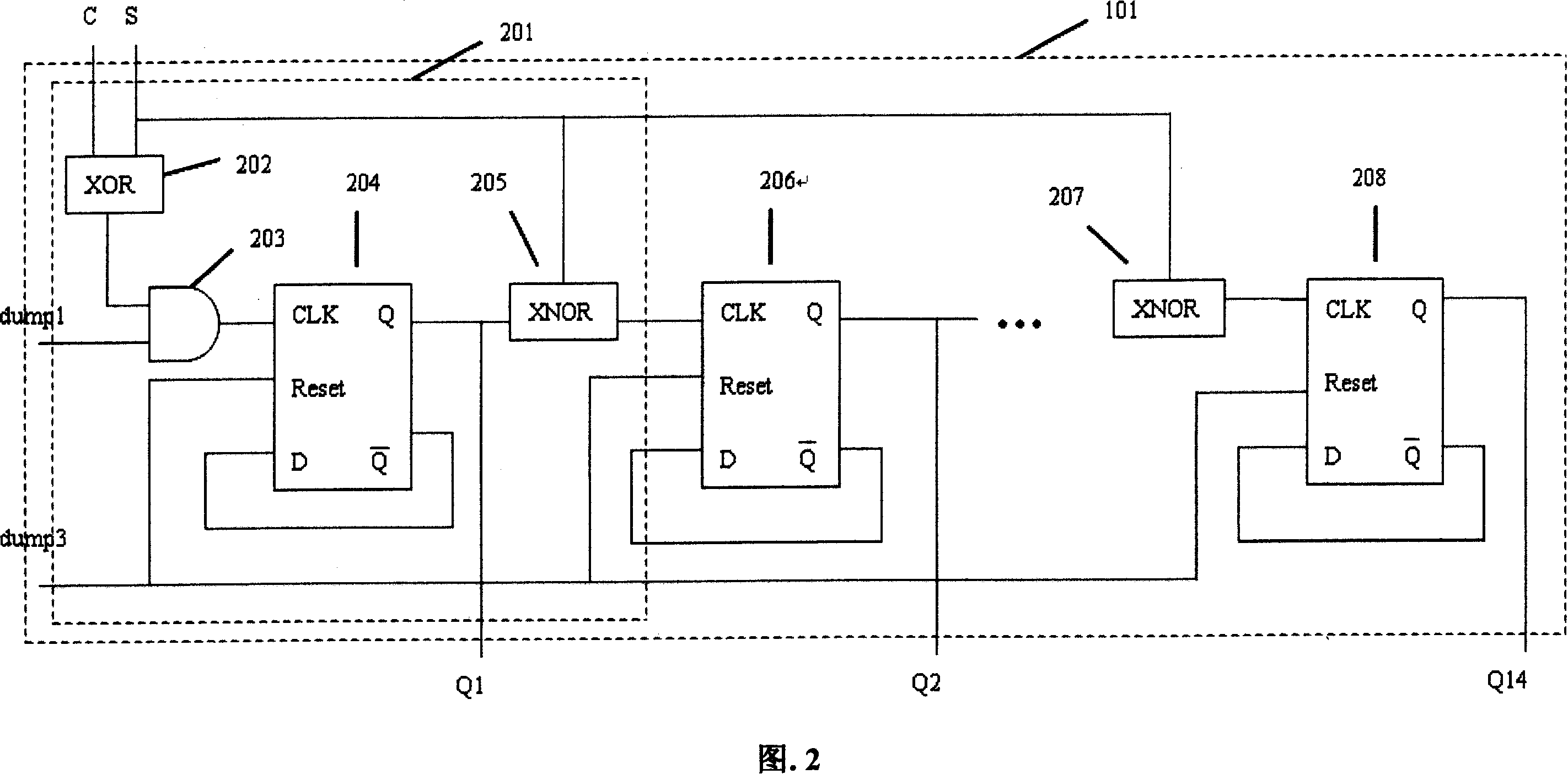

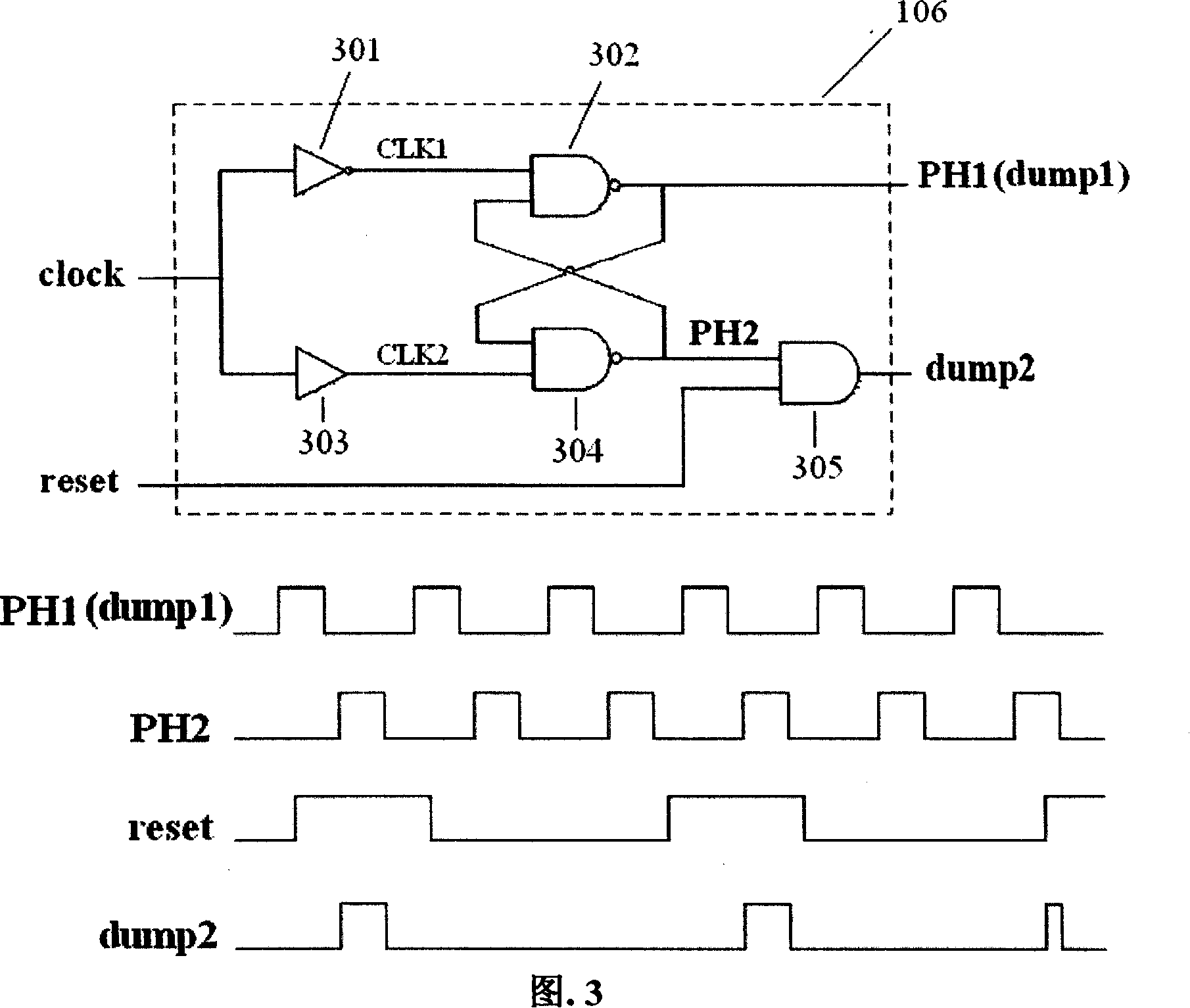

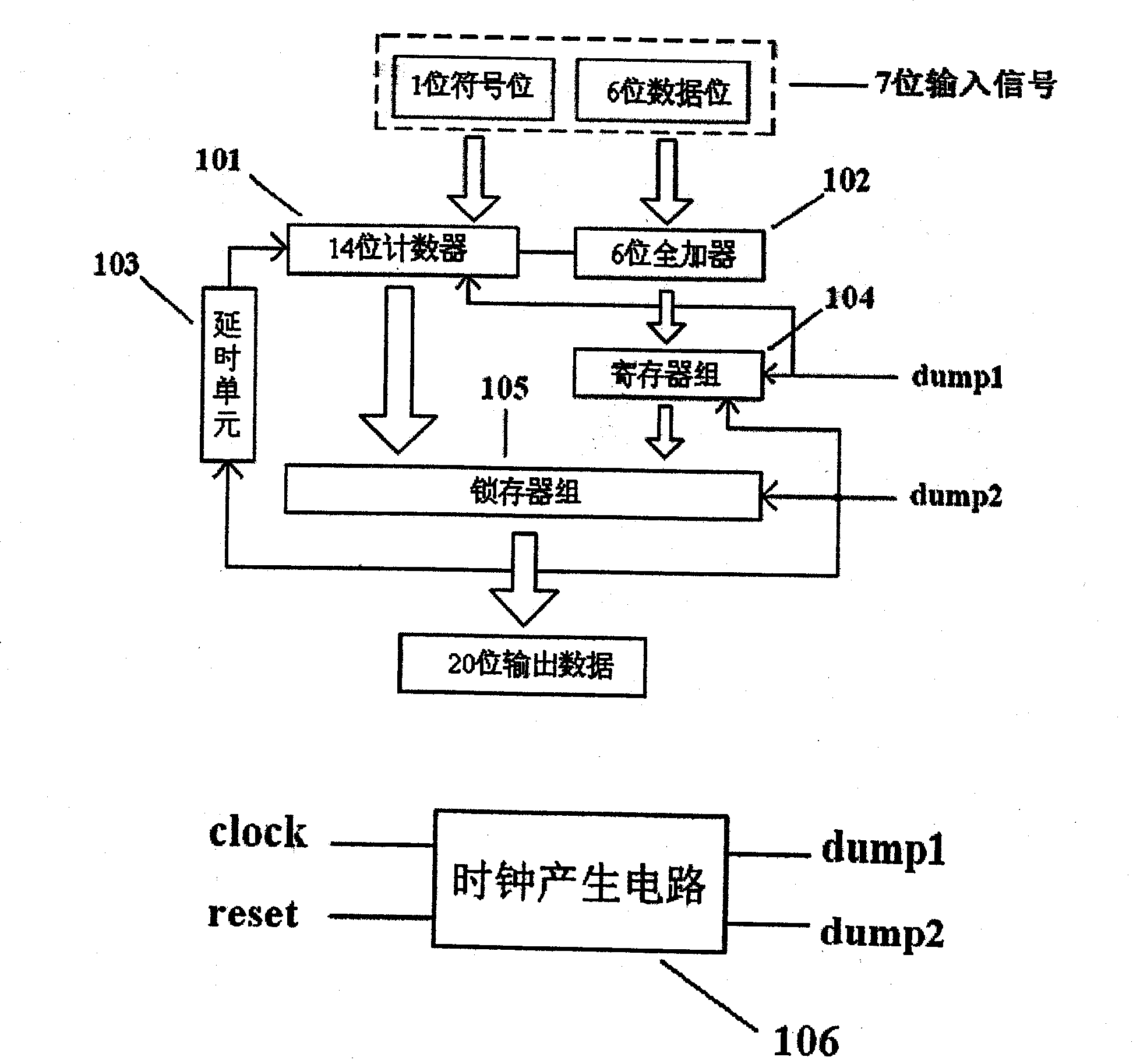

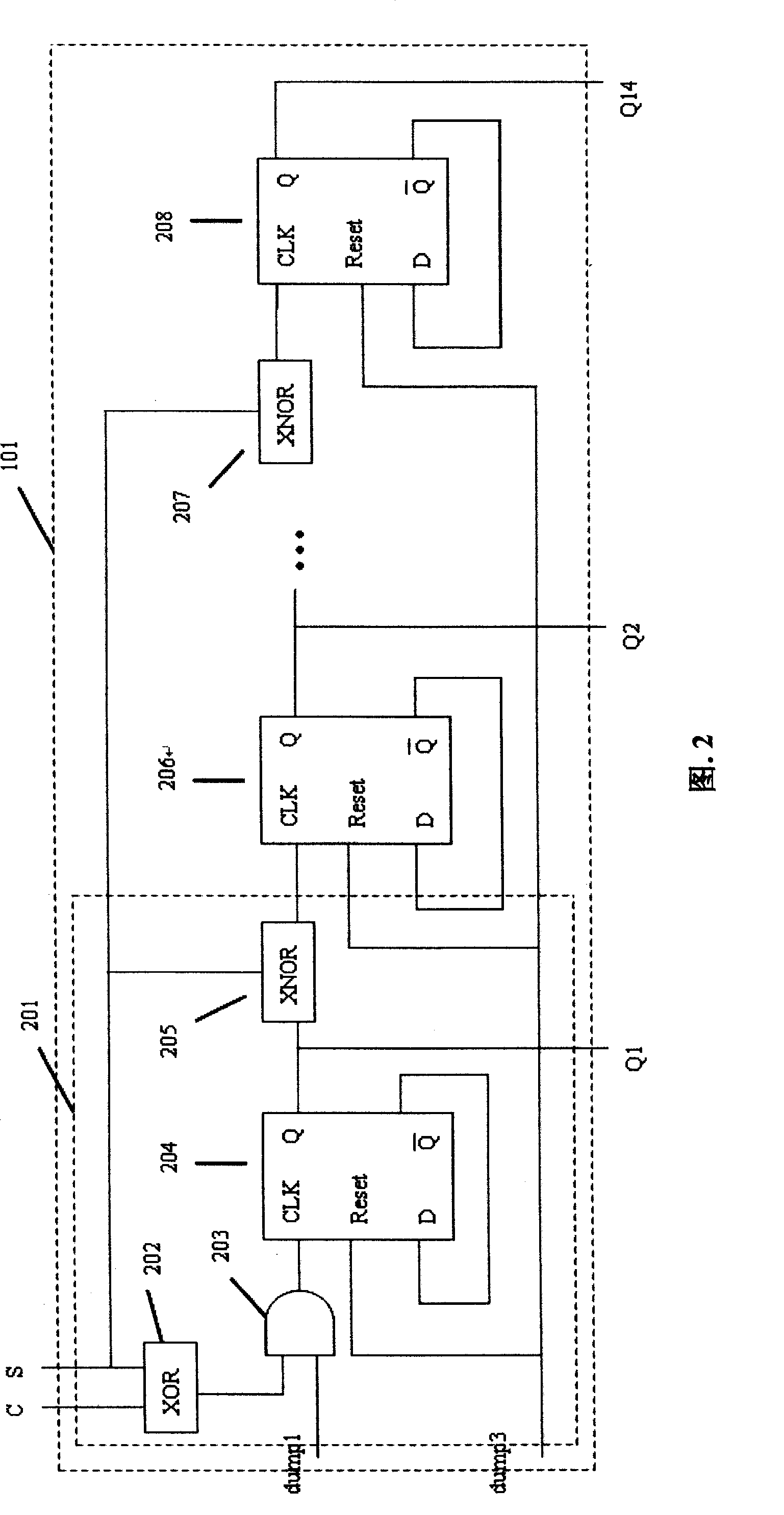

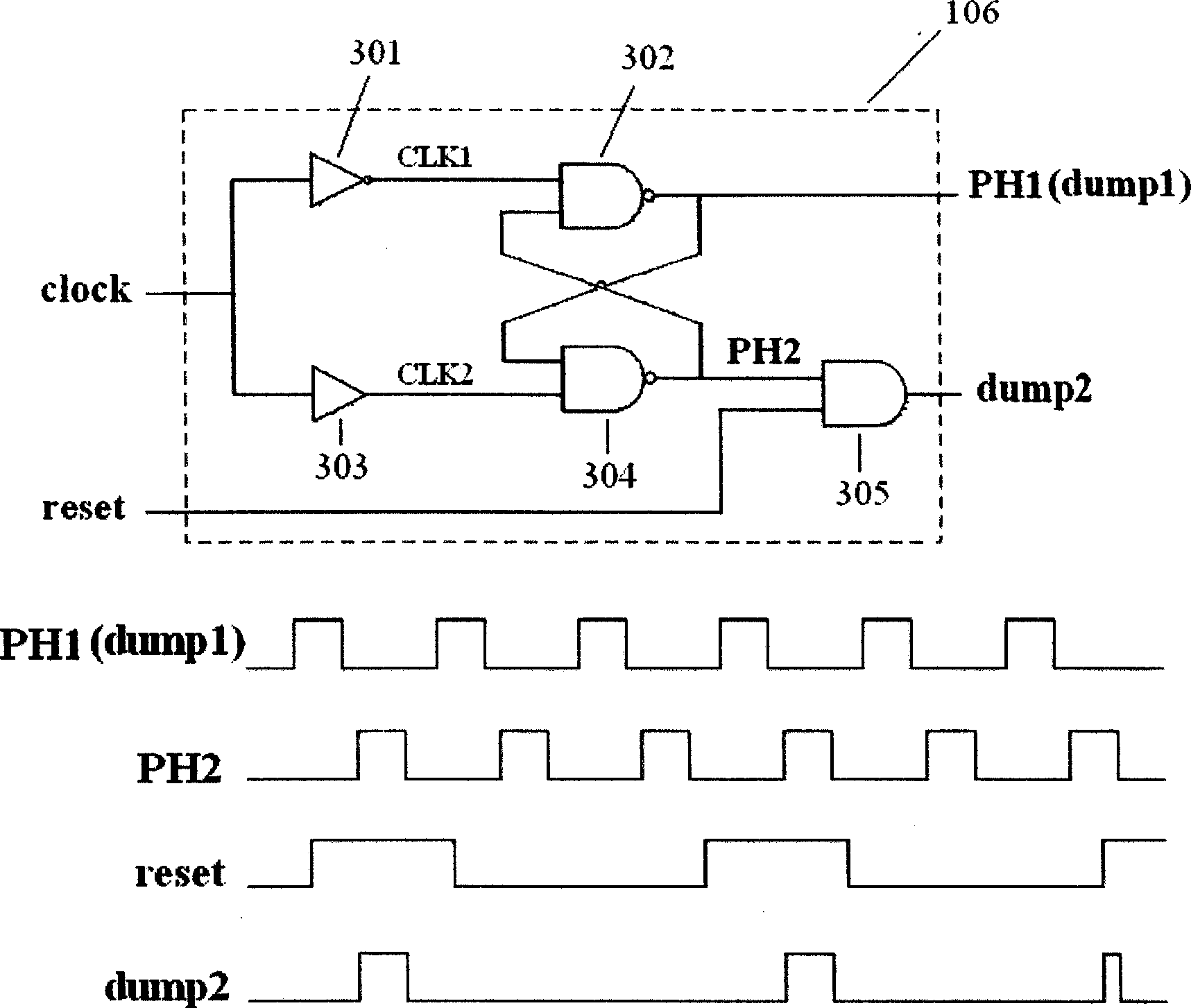

Correlator circuit for global positioning system

ActiveCN101109801AReduce consumptionReduce areaPosition fixationSatellite radio beaconingControl signalProcessor register

The invention discloses a circuit for a correlator of a global positioning system, which comprises a 6-bit full adder, a register set, a latch set and a clock generating circuit. The 6-bit full adder is connected with the register set, which is connected with the latch set. The first clock signal from the clock generating circuit is taken as the switch controlling signal of the register set, the second clock signal from the clock generating circuit is taken as the reset signal of the register set and the switch controlling signal of the latch set. Between the 6-bit full adder and the latch set, a 14-bit counter is provided. The function control end C of the 14-bit counter is connected with the carry-over signal end of the highest place of the 6-bit full adder; the 14 output ends of the 14-bit counter are correspondingly connected with the 7th to 20th input end of the latch set. The first clock signal from the clock generating circuit is also used as the clock signal of the 14-bit counter, the second clock signal from the clock generating circuit forms a third clock signal after delaying by the delay unit, and the third clock signal is used as the reset signal of the 14-bit counter.

Owner:NANJING LOW POWER IC TECH INST CO LTD

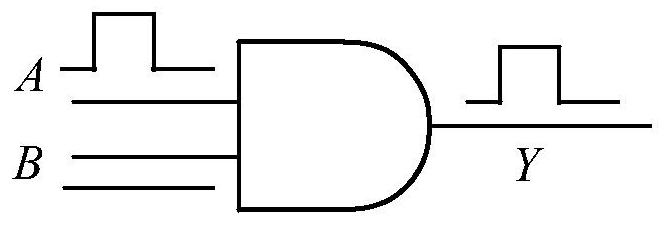

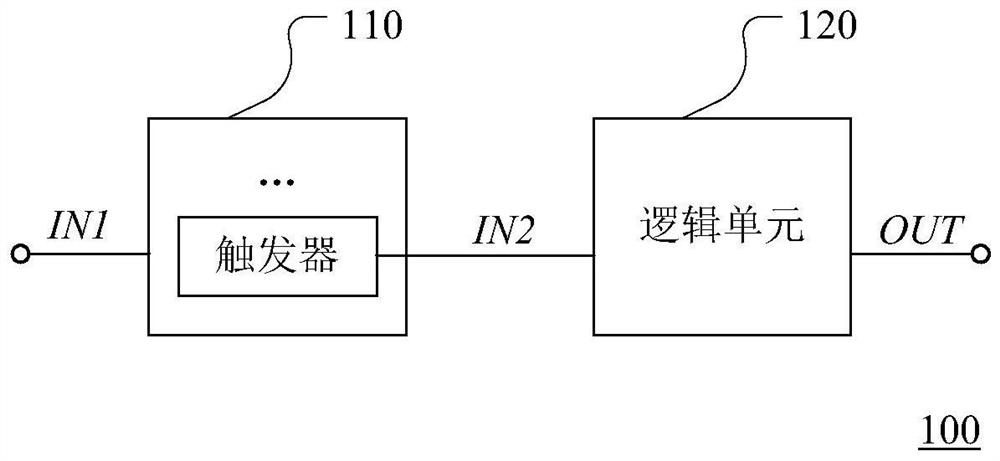

Digital processing circuit

PendingCN114448416AReduce dynamic power consumptionReduce Logic PowerPower consumption reductionVoltage/current interference eliminationSignal onHemt circuits

The invention discloses a digital processing circuit, comprising a logic unit comprising at least one combinational logic device, the combinational logic device comprising at least one input end; and the filtering unit is used for dividing the waveform of the received initial input signal into at least two sections of waveforms in one period of the clock signal of the combinational logic device and preventing burrs contained in at least one section of waveform from spreading backwards so as to provide a filtered input signal to the input end of the combinational logic device. According to the invention, the filtering unit prevents the burrs contained in at least one waveform in the initial input signal from spreading backwards, and can eliminate the influence of the burrs in the signal on the power consumption of the whole circuit in time, thereby effectively reducing the extra power consumption caused by the burrs.

Owner:MAXIO TECH (HANGZHOU) CO LTD

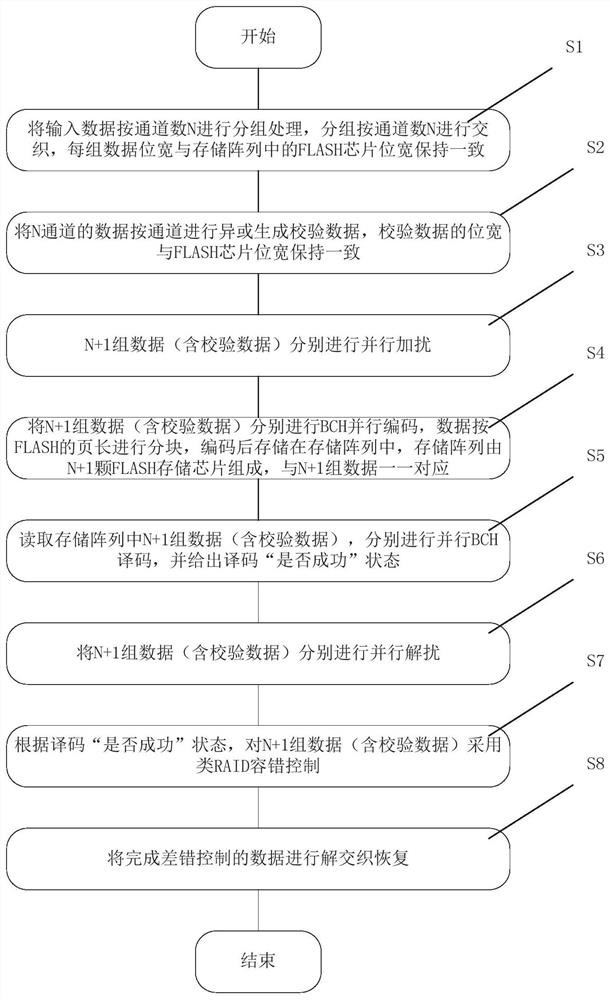

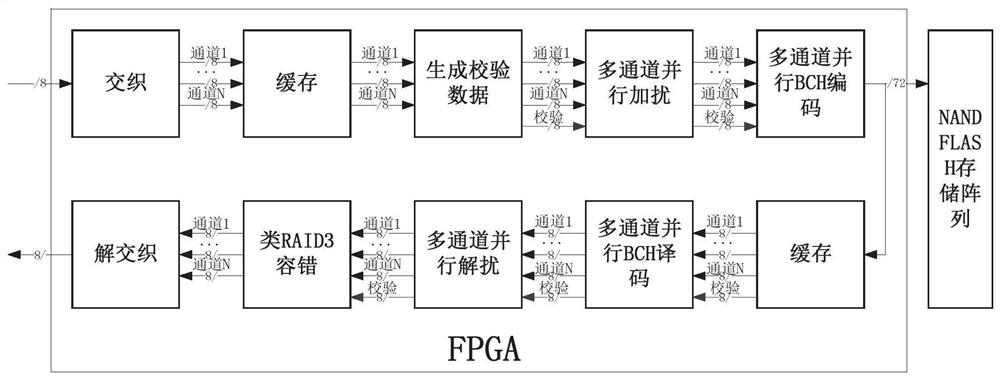

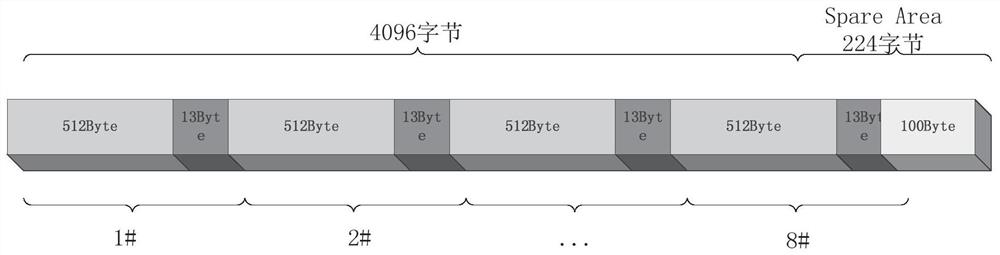

Multi-channel NAND FLASH error control method

PendingCN113241110AReduce the effect of coupling voltageReduce the probability of flippingRead-only memoriesData subjectChannel data

The invention provides a multi-channel NAND FLASH error control method based on the BCH and RAID-like technology. The method comprises the following steps: grouping input data according to a channel number N and then interleaving; performing XOR on the data of the N channels according to the channels to generate verification data; the check data and the N groups of channel data form N + 1 groups of channel data, and parallel scrambling is carried out on the N + 1 groups of channel data; BCH parallel coding is carried out on N + 1 groups of data, the data are partitioned according to the page length of FLASH, the coded data are stored in a storage array, and the storage array is composed of N + 1 FLASH storage chips and is in one-to-one correspondence with the N + 1 groups of data; the number of N + 1 groups in the storage array is read, parallel BCH decoding is carried out respectively, and a state of whether decoding is successful or not is given; performing parallel descrambling on the N + 1 groups of data; fault-tolerant control is carried out on N + 1 groups of data according to the state of whether decoding is successful or not; and carrying out de-interleaving recovery on the data subjected to error control. According to the method, design measures are taken from three dimensions of suppression, error correction and replacement, so that the bit error rate of the NAND FLASH is reduced.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM

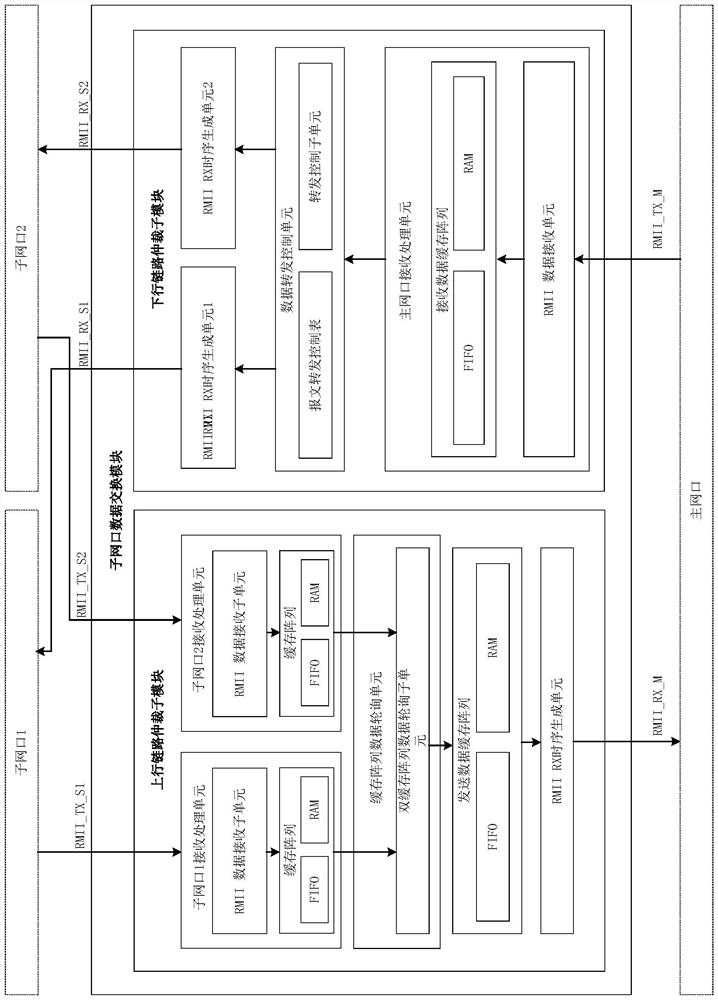

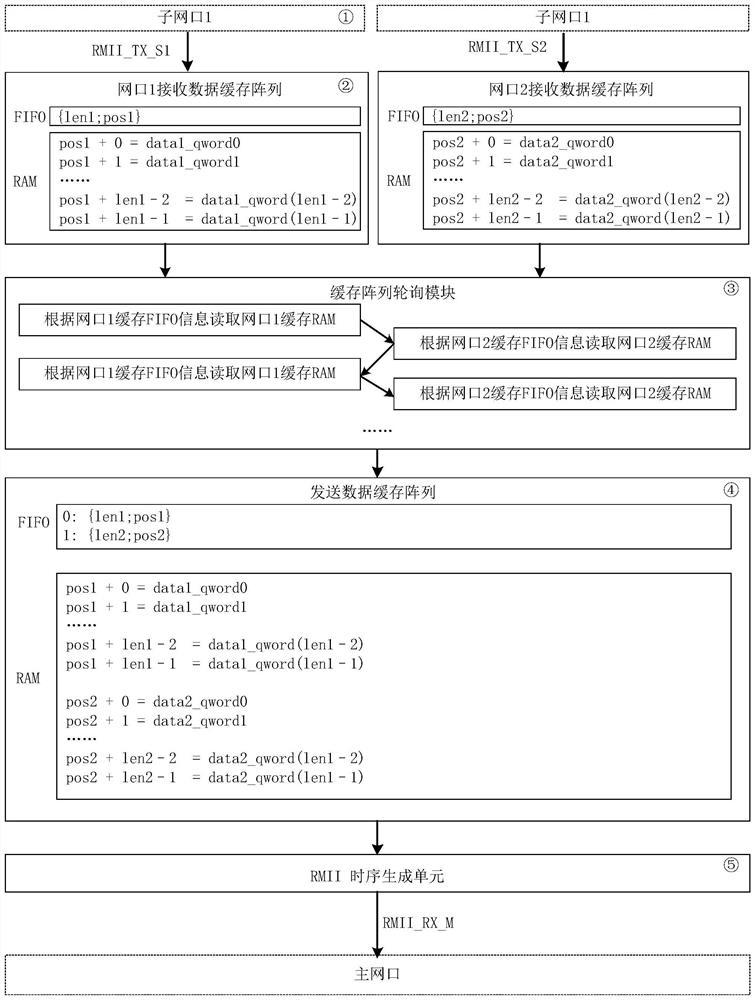

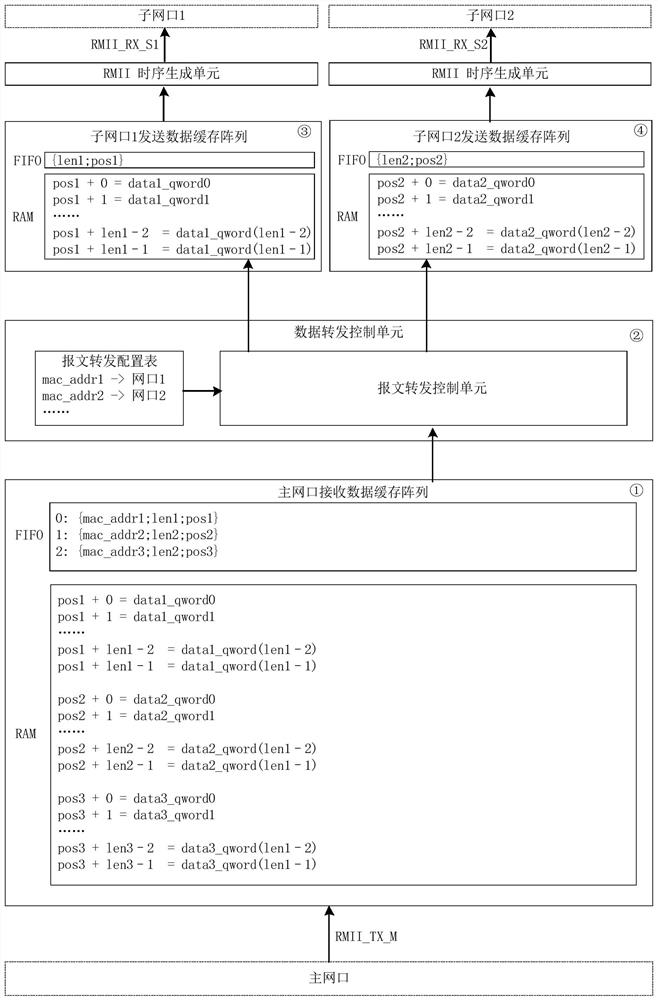

Data forwarding system and method, computing equipment and programmable logic device

PendingCN114500411AAccurate forwardingReduce the probability of flippingTransmissionProgrammable logic deviceComputer network technology

The embodiment of the invention is applicable to the technical field of computer networks, and provides a data forwarding system and method, computing equipment and a programmable logic device.The system comprises a main network port, at least one sub-network port and a sub-network port switching module, and the sub-network port switching module comprises an uplink arbitration sub-module and a downlink arbitration sub-module; the uplink arbitration sub-module comprises a sub-network port receiving and processing unit, a cache array data polling unit and a sending data cache array; the downlink arbitration sub-module comprises a data forwarding control unit and a main network port receiving and processing unit; the uplink arbitration sub-module is adopted to forward an uplink datagram received by the sub-network port to the main network port; a downlink datagram received by the main network port can be forwarded to the corresponding sub-network port by adopting the downlink sub-module. The system can flexibly control network ports corresponding to data forwarding, and accurately forward datagrams, so that the energy consumption of the system is reduced.

Owner:长园深瑞继保自动化有限公司

A low-power combined encoding and decoding circuit and encoding and decoding method applied to a network on chip

ActiveCN106059592BReduce power consumptionReduce the probability of flippingCode conversionComputer moduleData encoding

The invention discloses an encoding and decoding circuit based on low power consumption combination applied to a network on chip and an encoding and decoding method thereof. The encoding and decoding circuit is characterized in that an encoding circuit is arranged at the input end of a source node, and a decoding circuit is arranged at the output end of a destination node; the encoding circuit comprises an encoding judgment splitting module, four Hamming distance calculating modules, four data turning modules, a gray code encoding module, and a data encoding packaging module; and the decoding circuit comprises a decoding judgment splitting module, four data anti-turning modules, a gray code decoding module, and a data decoding packaging module. The turning rate of transmitted data can be reduced, so that the power consumption of the whole network on chip is reduced, and correct data transmission is ensured.

Owner:黄山市开发投资集团有限公司

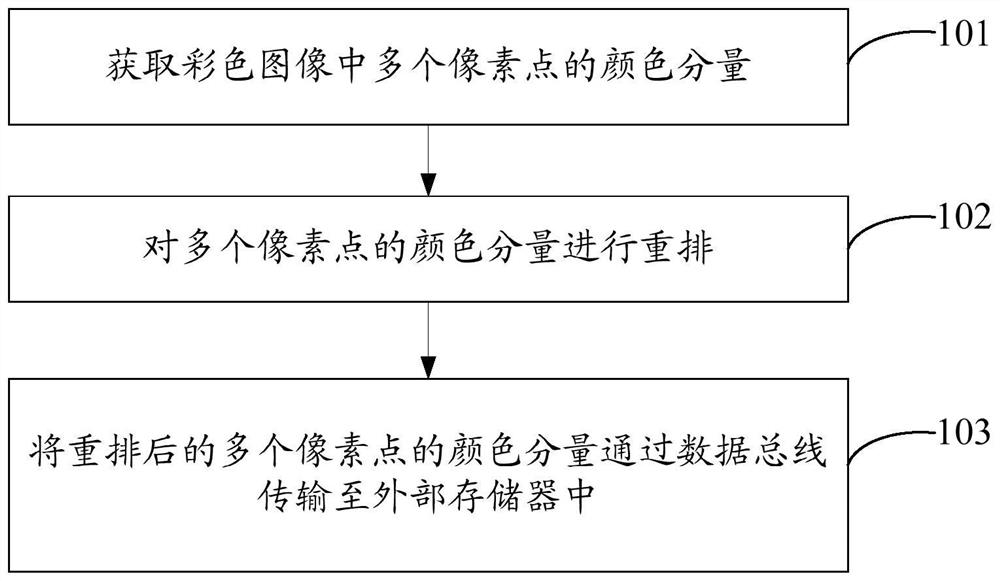

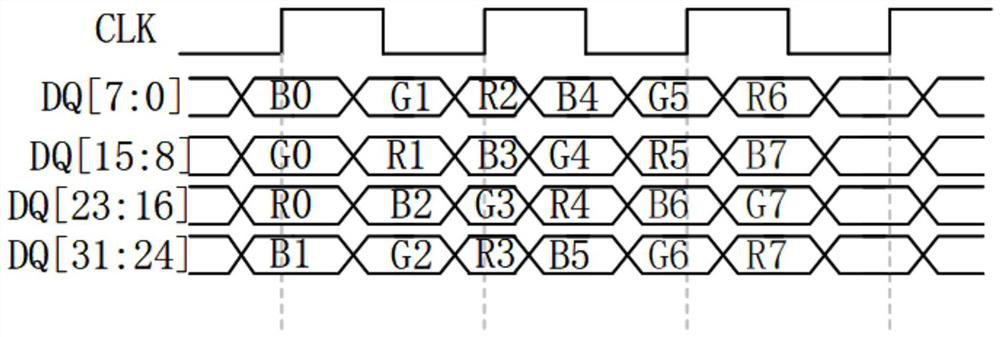

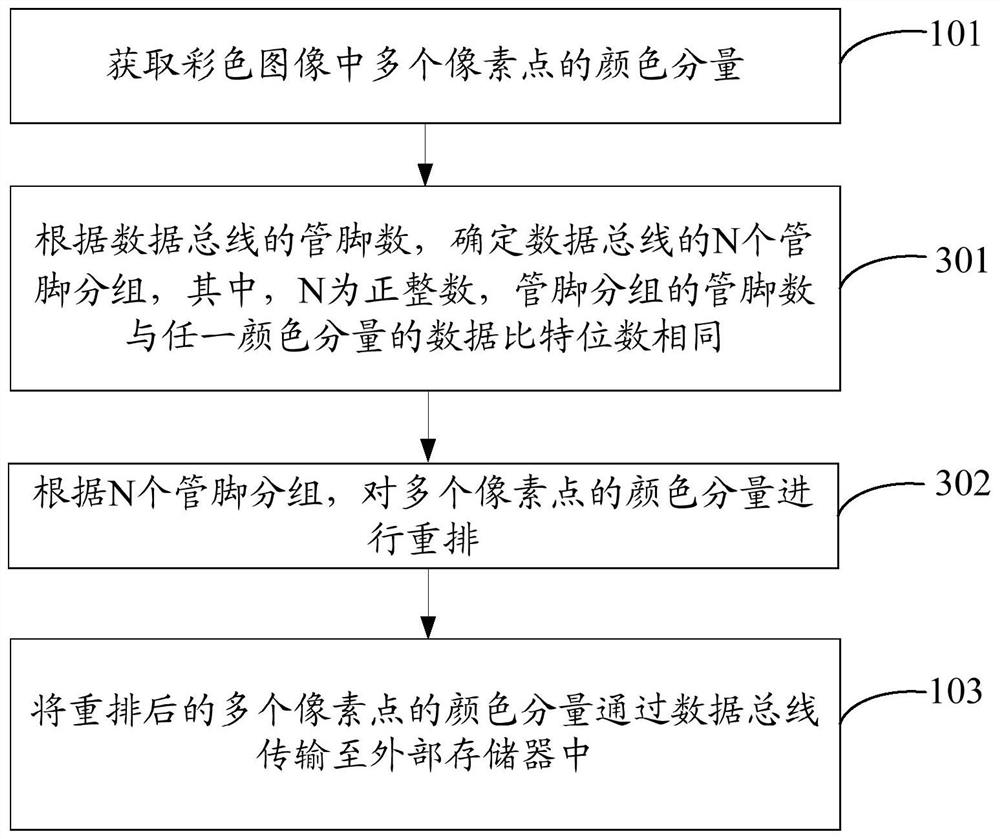

Color image transmission method and device, electronic equipment and storage medium

ActiveCN112181876AReduce the probability of flippingReduce power consumptionImage memory managementProcessor architectures/configurationColor imageImaging processing

The invention discloses a color image transmission method and device, electronic equipment and a storage medium, and belongs to the technical field of image processing. The method comprises the following steps: acquiring color components of a plurality of pixel points in a color image; rearranging the color components of the plurality of pixel points; and sending the color components of the rearranged pixel points to an external memory through a data bus, and in the transmission process, using at least one pin group of the data bus for transmitting the color components of the same type. Therefore, the transmission sequence of the color components on each pin group is changed by changing the arrangement sequence of the color components in each pixel point in the color image, and the color components of the same type are transmitted through at least one same pin group, so that the turnover rate of the data bus pins is reduced, and the transmission power consumption is reduced.

Owner:LYNXI TECH CO LTD

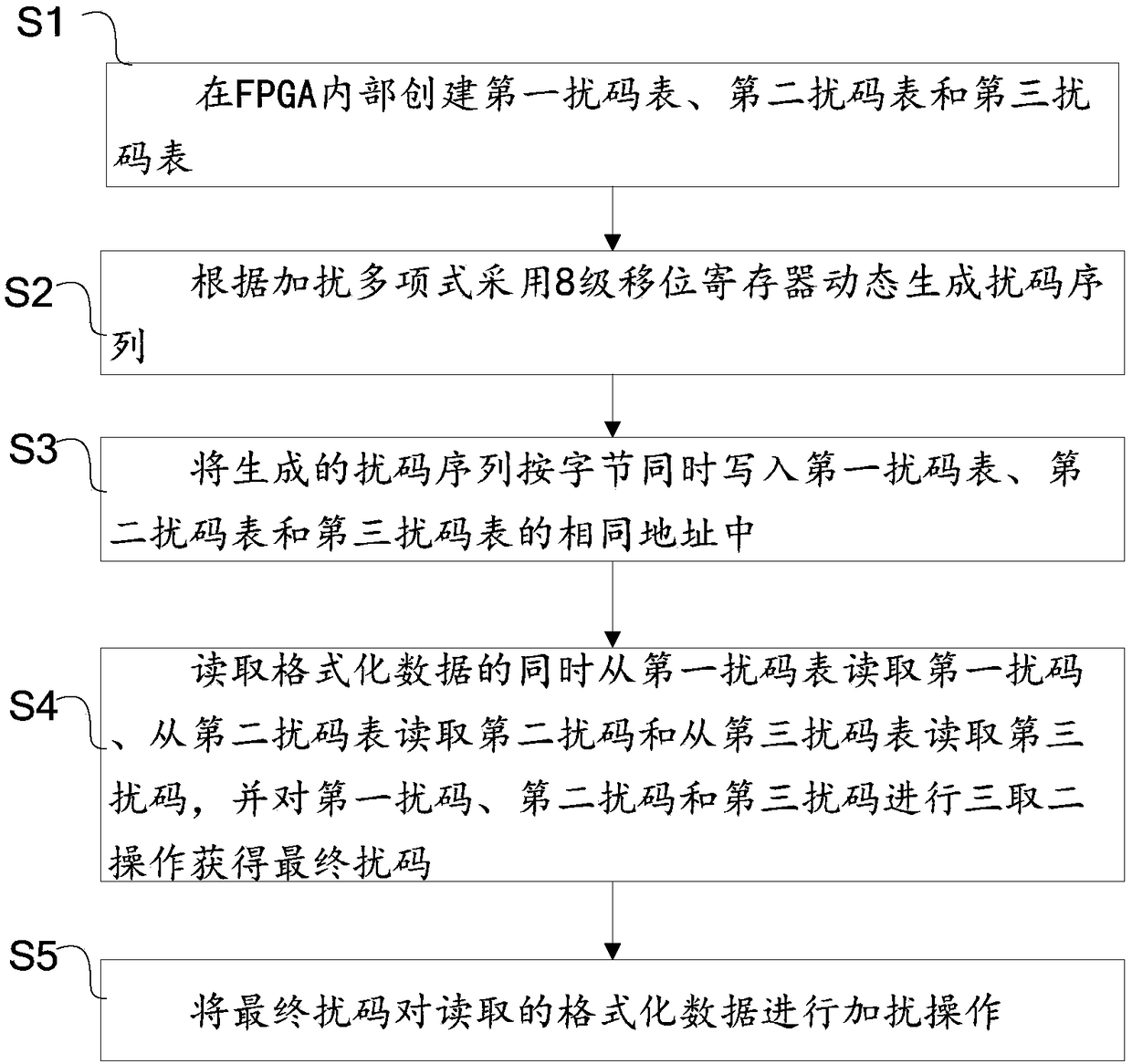

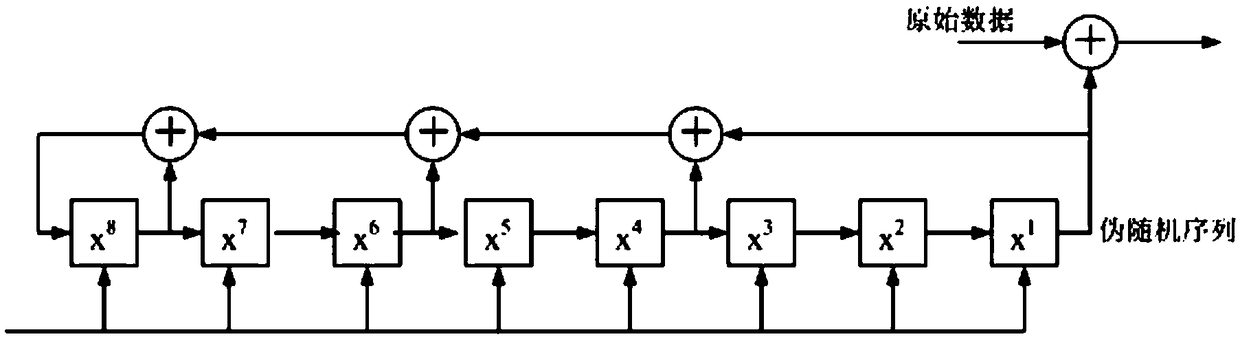

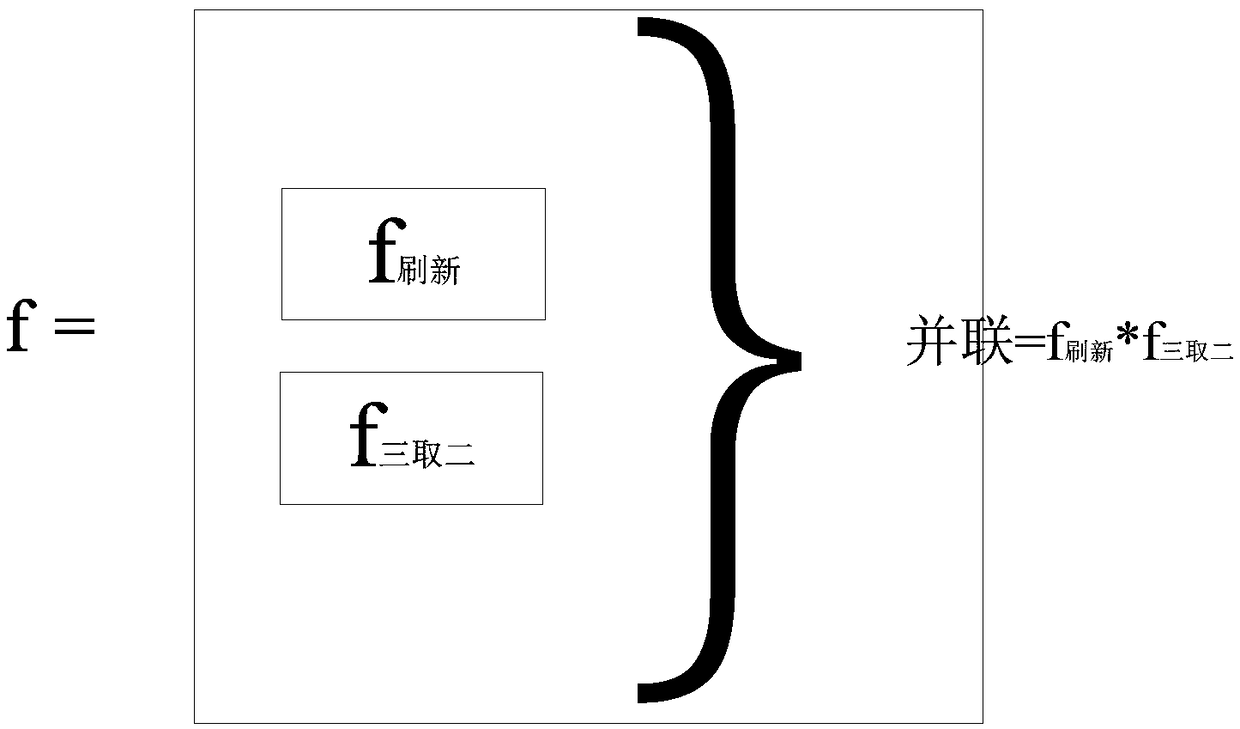

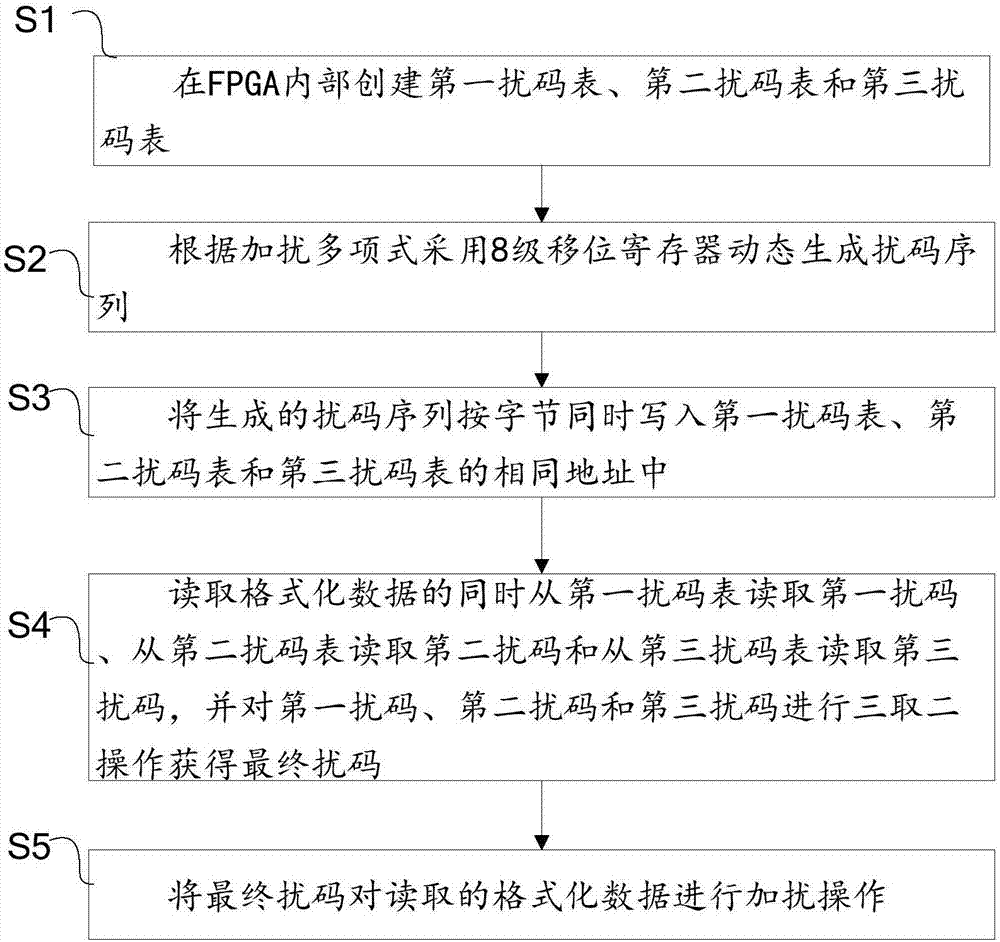

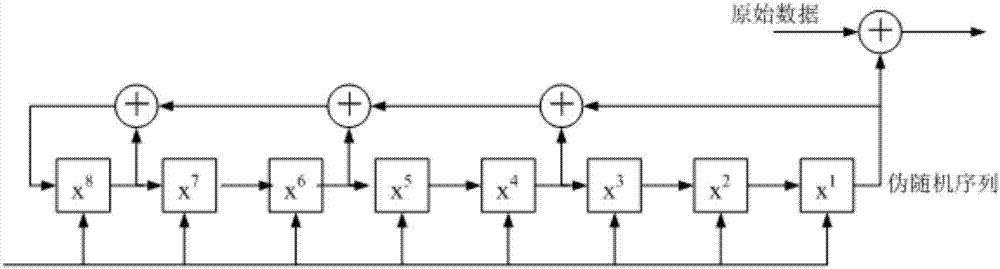

A Parallel Scrambling Method Against Spatial Single Event Flip

ActiveCN107547162BGuaranteed correctnessReduce the probability of flippingExclusive-OR circuitsTime-division multiplexShift registerParallel computing

Disclosed is a parallel scrambling method for preventing single event upset in space. The method comprises the steps of creating a first scrambling code table, a second scrambling code table and a third scrambling code table in an FPGA; adopting an 8-level shift register to dynamically generate a scrambling code sequence according to scrambling polynomial; writing the generated scrambling code sequence into the same addresses of the first scrambling code table, the second scrambling code table and the third scrambling code table according to bytes at the same time; reading formatted data, reading a first scrambling code from the first scrambling code table, reading a second scrambling code from the second scrambling table and reading a third scrambling code from the third scrambling code table at the same time, and conducting two-out-of-three operation on the first scrambling code, the second scrambling code and the third scrambling code to obtain a final scrambling code; using the final scrambling code to conduct scrambling operation on the read formatted data. Because the three identical scrambling code tables are created in the FPGA and the final scrambling code is obtained by the two-out-of-three operation, the probability of the single event upset simultaneously occurring at the same locations of the three scrambling tables is extremely low, and therefore the capability and reliability of preventing the single event upset in parallel scrambling design are improved.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM

Design method of the semiconductor circuit device and CAD device

InactiveCN101273357BImprove performanceImprove resistance to soft errorsReliability increasing modificationsSolid-state devicesHemt circuitsRadiation exposure

Provided is a semiconductor circuit device in which soft error resistance is enhanced while assuring the high-speed operation of an entire LSI circuit. A CAD device includes: means for identifying a signal transmission time of each signal transmission circuit of the LSI circuit; means for identifying an output inversion ratio upon radiation exposure of a flip-flop circuit of each signal transmission circuit; means for identifying a signal transmission circuit as a critical path; means for calculating a soft error ratio of the entire LSI circuit according to the signal transmission time, the output inversion ratio, and the clock cycle; and means for lowing the soft error ratio of the entire LSI circuit without changing the signal transmission time of the signal transmission circuit as the critical path when a predetermined soft error ratio is lower than the soft error ratio of the entire LSI circuit.

Owner:SOCIONEXT INC

A register circuit designed for radiation hardening

ActiveCN103077746BImprove radiation resistanceReduce the probability of flippingDigital storageProcessor registerEngineering

The invention discloses a register circuit with radiation reinforcing design, which comprises a first-stage master latch, a second-stage slave latch, a first phase inverter and a second phase inverter. The first-stage main latch is provided with two data inputs which are respectively from a data input di from a register and a complementary data input dib from the register; the first-stage main latch is provided with 1 clock input ck and two data outputs which are respectively a latch data ql and a complementary latch data qlb; the second-stage slave latch is provided with two data inputs which are respectively from the data output ql of the first-stage main latch and the complementary data output qlb of the first-stage main latch; the second-stage slave latch is provided one clock input ck and a complementary clock input ckn from the register; and the second-stage slave latch is provided with 2 data outputs which are respectively a register data rq of the register and a complementary register data rqb of the register. With the utilization of the register circuit with the radiation reinforcing design, the irradiation property of the register is enhanced, and no excessive area consumption is caused while the irradiation property of the register is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Parallel scrambling method for preventing single event upset in space

ActiveCN107547162AGuaranteed correctnessReduce the probability of flippingExclusive-OR circuitsTime-division multiplexShift registerByte

Disclosed is a parallel scrambling method for preventing single event upset in space. The method comprises the steps of creating a first scrambling code table, a second scrambling code table and a third scrambling code table in an FPGA; adopting an 8-level shift register to dynamically generate a scrambling code sequence according to scrambling polynomial; writing the generated scrambling code sequence into the same addresses of the first scrambling code table, the second scrambling code table and the third scrambling code table according to bytes at the same time; reading formatted data, reading a first scrambling code from the first scrambling code table, reading a second scrambling code from the second scrambling table and reading a third scrambling code from the third scrambling code table at the same time, and conducting two-out-of-three operation on the first scrambling code, the second scrambling code and the third scrambling code to obtain a final scrambling code; using the final scrambling code to conduct scrambling operation on the read formatted data. Because the three identical scrambling code tables are created in the FPGA and the final scrambling code is obtained by the two-out-of-three operation, the probability of the single event upset simultaneously occurring at the same locations of the three scrambling tables is extremely low, and therefore the capability and reliability of preventing the single event upset in parallel scrambling design are improved.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM

A radiation-resistant d-flip-flop circuit based on triple-interlock unit

InactiveCN104363005BStable outputStable and reliable outputElectric pulse generator circuitsExternal dataData signal

The invention discloses an anti-radiation D flip-flop circuit based on three mutual-latching units. The anti-radiation D flip-flop circuit comprises a clock signal generation circuit, a D input filter circuit, C unit circuits, a voting circuit, a primary mutual-latching circuit and a secondary mutual-latching circuit. The C unit circuits include a first C unit circuit, a second C unit circuit and a third C unit circuit. Clock signals are generated after an external clock signal CK passes through the clock signal generation circuit, data signals are generated after an external data signal D passes through the D input filter circuit, data signals, output after the clock signals and the data signals pass through the primary mutual-latching circuit, the secondary mutual-latching circuit and the C unit circuits, passes through the voting circuit to output an output signal Q of a whole flip-flop. The anti-radiation D flip-flop circuit has the advantages that a three mutual-latching circuit reinforcement technology is adopted, output stability and reliability of the whole D flip-flop circuit can be guaranteed in case of overturning of the D flip-flop circuit due to interference such as radiation, and anti-radiation capability of the D flip-flop circuit is greatly improved.

Owner:ANQING NORMAL UNIV

A Radiation Hardened Flip-Flop Circuit Based on Complex Triple Interlock Unit

InactiveCN104410389BStable outputImprove reliabilityElectric pulse generator circuitsRadiation resistantExternal data

The invention discloses a radiation-hardening trigger circuit based on a complex three-interlocking unit. The radiation-hardening trigger circuit is composed of a clock signal generating circuit, a D input filtering circuit, a C unit circuit, a voting circuit, and a main interlock. It consists of a storage circuit and a slave interlock circuit; the C unit circuit includes a first C unit circuit, a second C unit circuit and a third C unit circuit; the external clock signal CK generates the clock signal and external data through the clock signal generating circuit The signal D is input to the filter circuit through the D input filter circuit to generate the data signal after the master interlock circuit, the slave interlock circuit and the C unit circuit, the output data signal outputs the output signal Q of the entire flip-flop through the voting circuit. The technical scheme of the present invention adopts the complex three-interlock circuit to reinforce the flip-flop technology, which can ensure the stability of the output of the entire flip-flop circuit when the flip-flop circuit is disturbed by radiation and other interference and causes the circuit to flip, enhances its reliability, and greatly improves the flip-flop. Radiation resistance of the circuit.

Owner:ANQING NORMAL UNIV

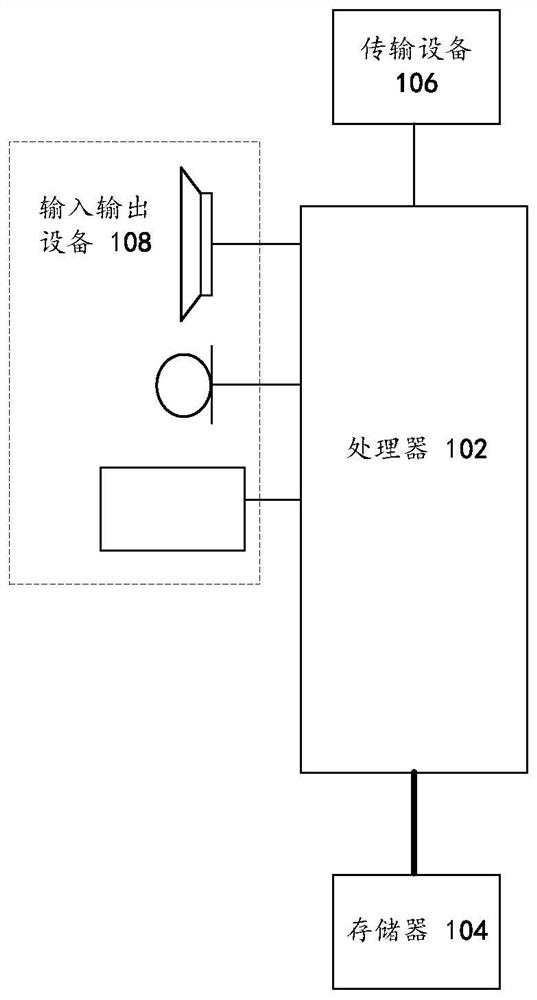

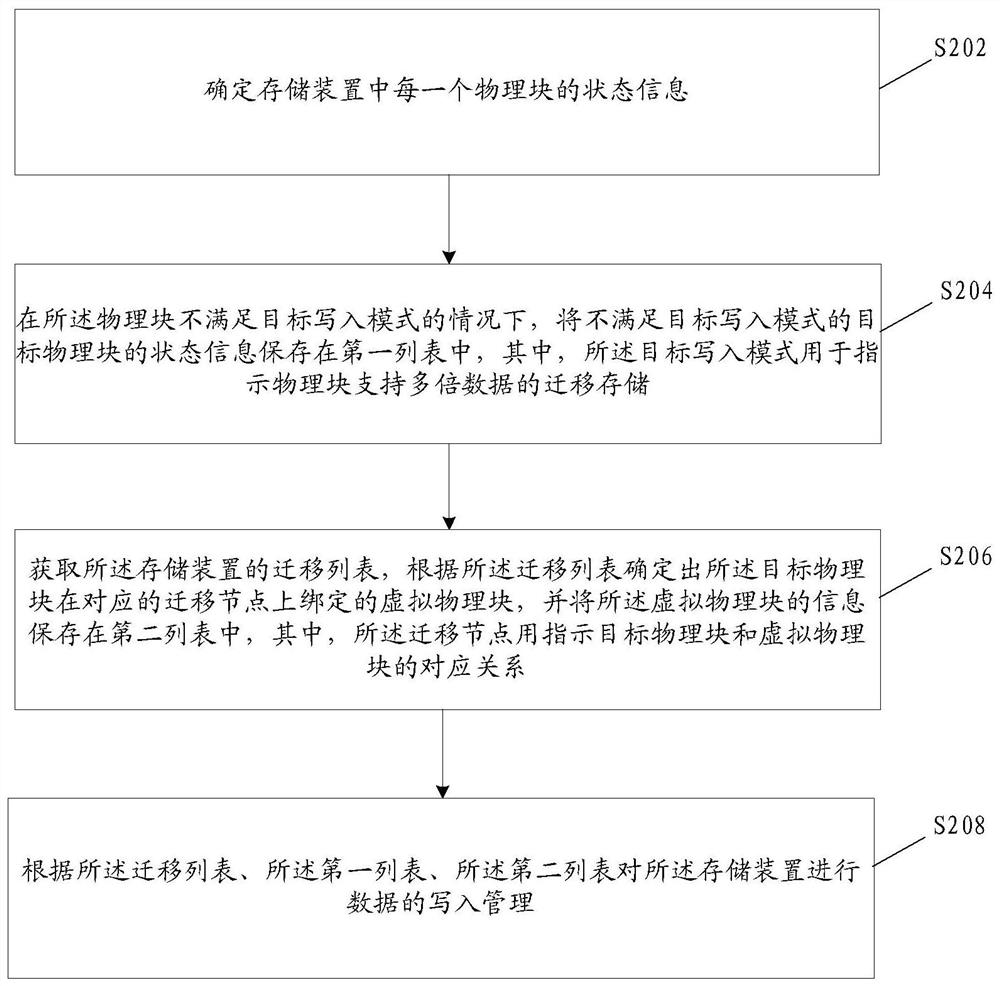

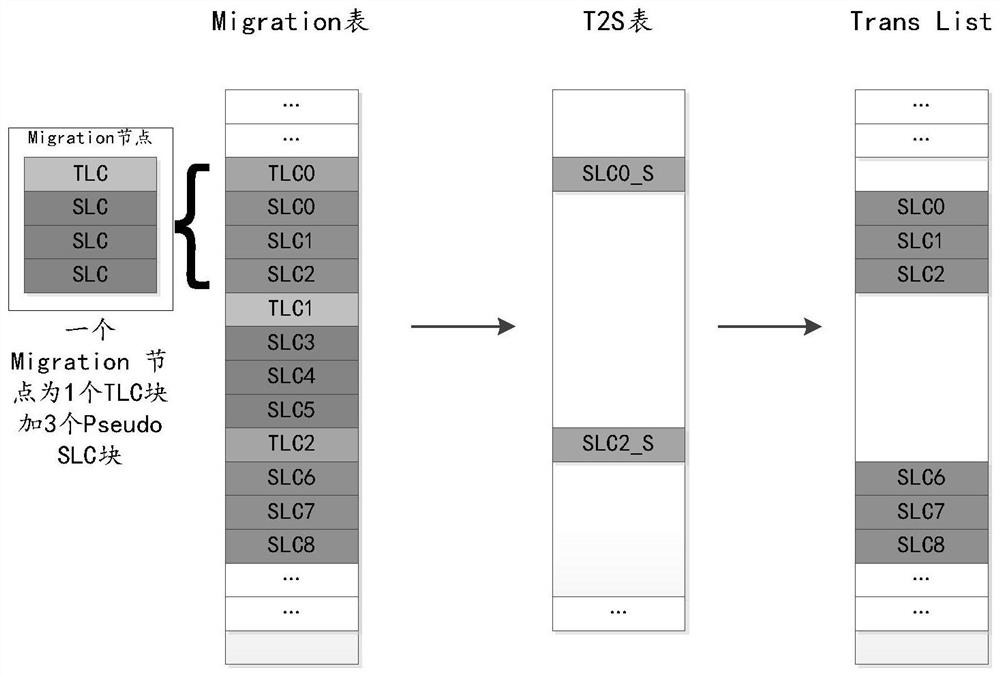

Data management method and device, storage medium and electronic device

PendingCN113703680AOptimize the writing processImprove writing efficiencyInput/output to record carriersComputer hardwareData management

The invention provides a data management method and device, a storage medium and an electronic device. The method comprises the steps that: state information of each physical block in the storage device is determined; under the condition that the physical blocks do not meet the target write-in mode, state information of the target physical blocks which do not meet the target write-in mode is stored in a first list, wherein the target write-in mode is used for indicating that the physical blocks support migration storage of multiple data; a migration list of the storage device is obtained, a virtual physical block bound to a target physical block on a corresponding migration node is determined according to the migration list, and information of the virtual physical block is stored in a second list, wherein the migration node is used for indicating the corresponding relation between the target physical block and the virtual physical block; and data writing management is performed on the storage device according to the migration list, the first list and the second list. The problem that the cost cannot be reduced while the reliability of the storage device is ensured in the prior art is solved.

Owner:ZHEJIANG HUAYIXIN TECH CO LTD

Correlator circuit for global positioning system

ActiveCN101109801BReduce consumptionReduce areaPosition fixationSatellite radio beaconingProcessor registerControl signal

The invention discloses a circuit for a correlator of a global positioning system, which comprises a 6-bit full adder, a register set, a latch set and a clock generating circuit. The 6-bit full adder is connected with the register set, which is connected with the latch set. The first clock signal from the clock generating circuit is taken as the switch controlling signal of the register set, the second clock signal from the clock generating circuit is taken as the reset signal of the register set and the switch controlling signal of the latch set. Between the 6-bit full adder and the latch set, a 14-bit counter is provided. The function control end C of the 14-bit counter is connected with the carry-over signal end of the highest place of the 6-bit full adder; the 14 output ends of the 14-bit counter are correspondingly connected with the 7th to 20th input end of the latch set. The first clock signal from the clock generating circuit is also used as the clock signal of the 14-bit counter, the second clock signal from the clock generating circuit forms a third clock signal after delaying by the delay unit, and the third clock signal is used as the reset signal of the 14-bit counter.

Owner:NANJING LOW POWER IC TECH INST CO LTD

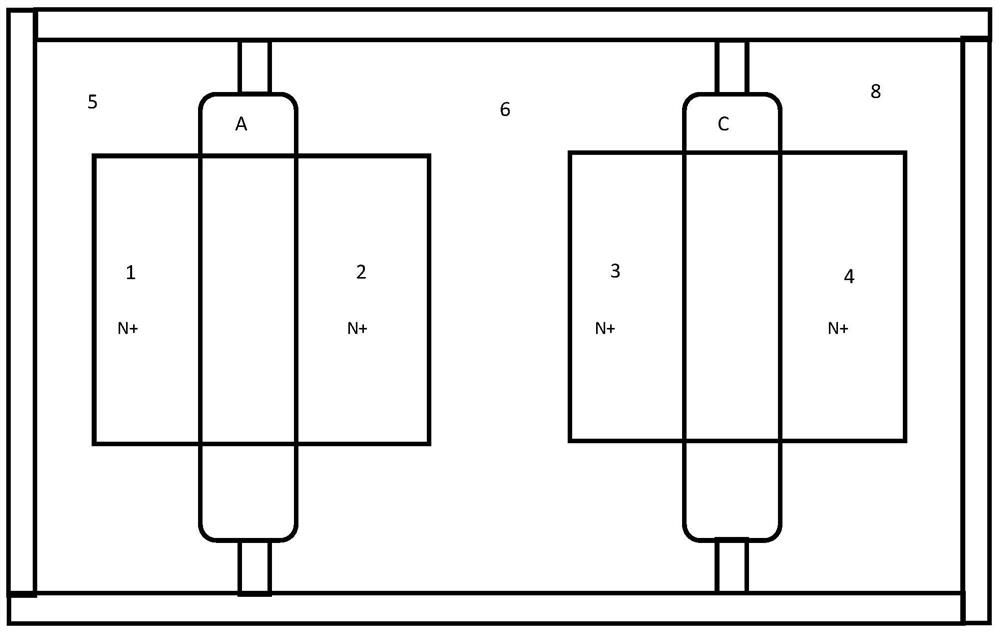

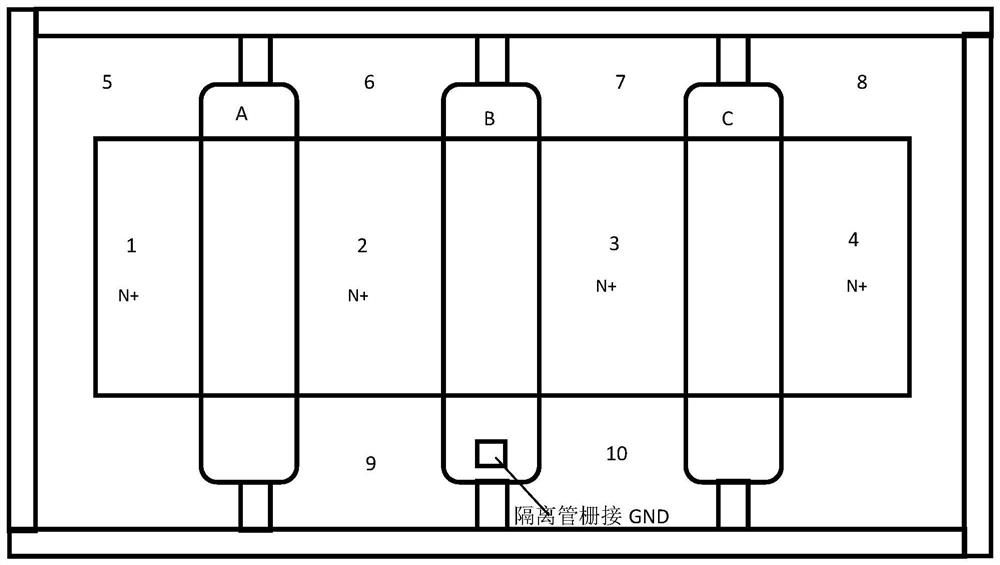

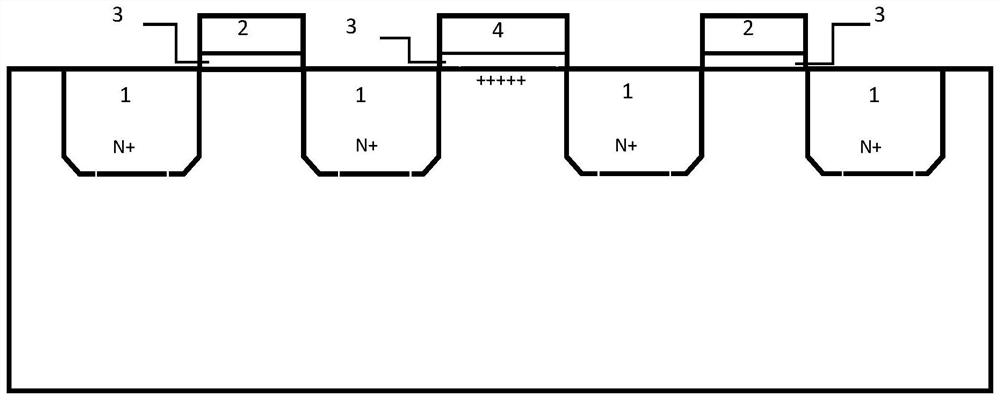

SRAM memory cell reinforcing method based on DICE structure and SRAM memory array

ActiveCN112131819ASolve flipSolve the latch problemComputer aided designSpecial data processing applicationsMemory cellSoftware engineering

The invention relates to the technical field of integrated circuits, in particular to an SRAM memory cell reinforcing method based on a DICE structure and an SRAM memory array. The method comprises the following steps: on the basis of designing a double-interlock storage unit DICE structure in a circuit, adding an NMOS isolation tube between NMOS tubes which cannot share a source end and a drain end and play a switching role, and connecting a grid electrode of the added NMOS isolation tube with GND. The problem that in the prior art, leakage current can be generated between adjacent NMOS tubesunder total dose radiation is solved. Cross layout is carried out on sensitive MOS tubes in circuit design in the aspect of layout, and the distance between sensitive nodes is increased, so that theprobability of circuit overturning during single-particle radiation is greatly reduced. The effect of enabling the SRAM memory cell and the array to have the anti-radiation capability on the premise of not influencing the function is achieved.

Owner:58TH RES INST OF CETC

A Flipping Hardening Method for Spaceborne Digital Signal Processor

ActiveCN103218272BImprove Inherent ReliabilityReduce the probability of single event eventsRedundant data error correctionStatic random-access memoryProgrammable read-only memory

Owner:XIAN INSTITUE OF SPACE RADIO TECH

sram storage unit reinforcement method and sram storage array based on dice structure

ActiveCN112131819BSolve the impact of leakageAdd gate to GNDComputer aided designSpecial data processing applicationsMemory cellHemt circuits

Owner:58TH RES INST OF CETC

A layout structure of well-isolated anti-SEU multi-node flipping memory cells

ActiveCN105609504BIncrease distanceSolve the problem of poor reliability of the flip effectSolid-state devicesSemiconductor devicesMemory cellCell region

A well-isolated anti-SEU multi-node inversion memory cell layout structure, comprising well isolation regions (201), (202), (203), DICE unit regions (101), (103), (105), (107), DICE units (102), (104), (106), (108). The well isolation region is arranged crosswise between the two DICE cell regions. Compared with the prior art, the present invention further increases the distance between sensitive node pairs while effectively separating all sensitive node pairs in the DICE memory cell structure, and the well isolation structure is also beneficial to reduce the distance between sensitive node pairs. The parasitic bipolar transistor effect and the charge sharing effect greatly suppress the multi-node turnover caused by SEU in the DICE unit, and greatly improve the anti-SEU performance of the radiation-resistant SRAM.

Owner:BEIJING MXTRONICS CORP +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com