A Parallel Scrambling Method Against Spatial Single Event Flip

A single-event flipping and spatial technology, applied in the field of data transmission, can solve the problems of reducing device speed and inapplicability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described in detail below through specific embodiments in conjunction with the accompanying drawings.

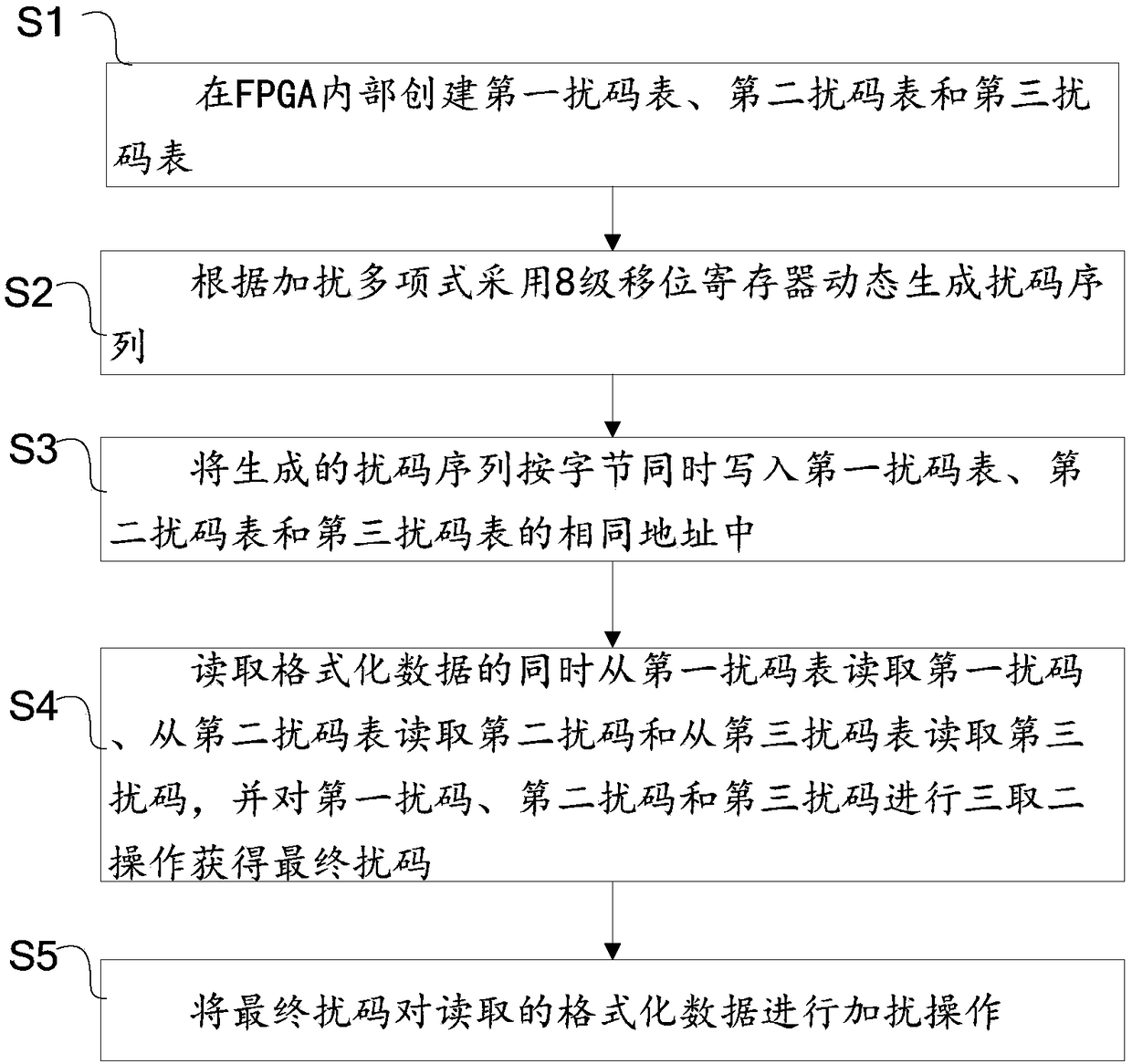

[0024] This example provides a parallel scrambling method against spatial single event flipping. The flow chart is as follows figure 1 As shown, it specifically includes the following steps:

[0025] S1: Create a first scrambling code table, a second scrambling code table and a third scrambling code table inside the FPGA.

[0026] Wherein, the first scrambling code table, the second scrambling code table and the third scrambling code table are three identical scrambling code tables, for example, the write data width is 8 bits, the depth is 1024, and the read data width is 64 bits, The depth is 128.

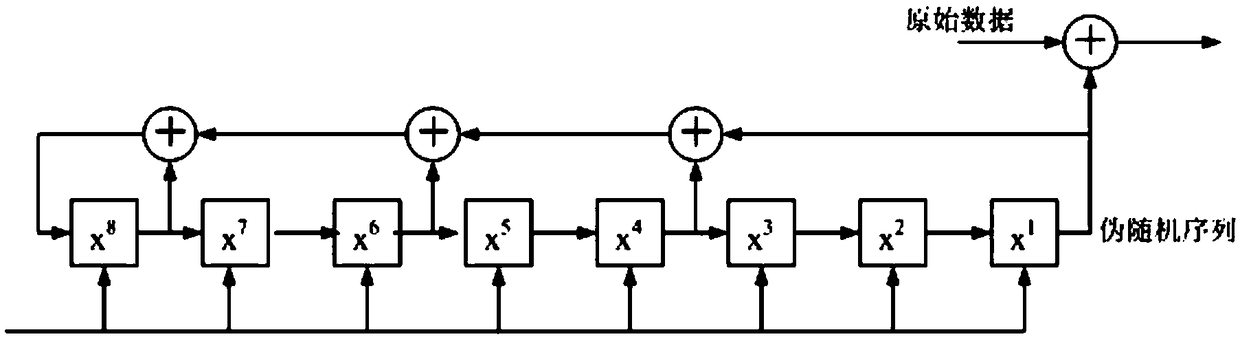

[0027] S2: Dynamically generate a scrambling code sequence by using an 8-stage shift register according to the scrambling polynomial.

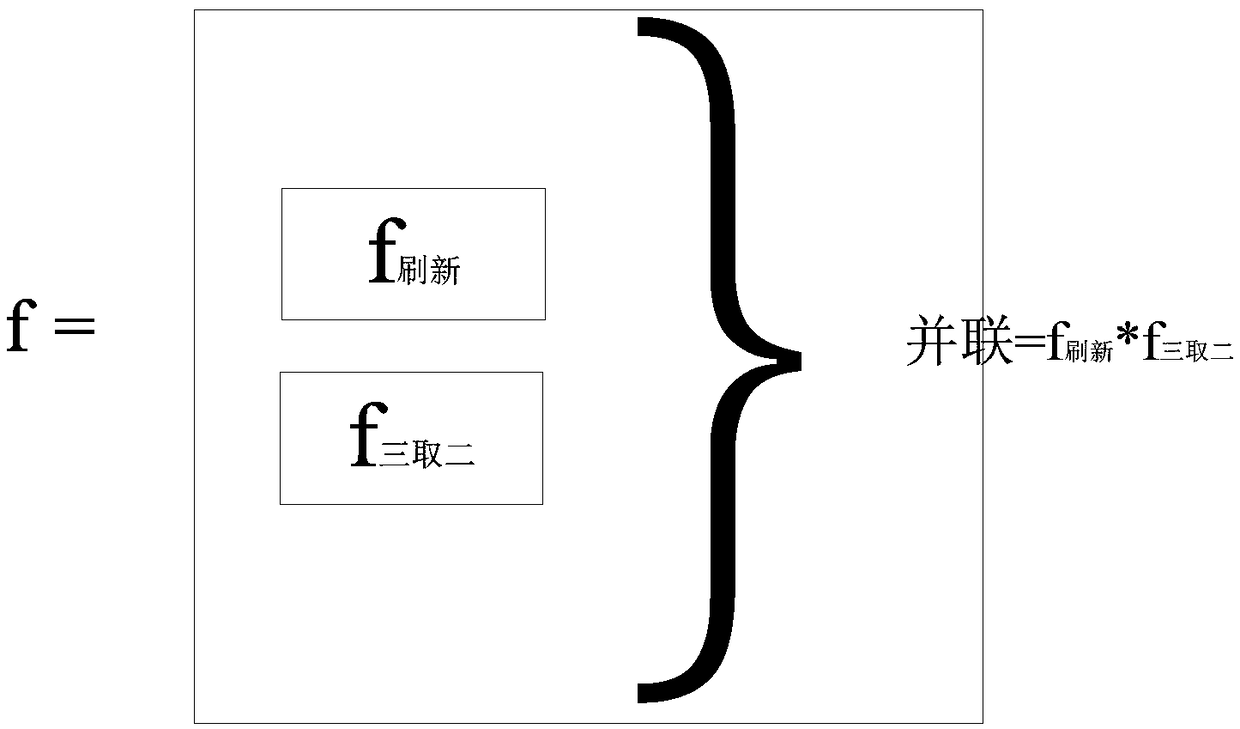

[0028] In this example, a scrambler composed of an 8-stage shift register is used, and a scramb...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com