Anti-radiation D flip-flop circuit based on three mutual-latching units

A unit circuit, interlocking technology, applied in the direction of electrical pulse generator circuits, electrical components, electrical pulse generation, etc., can solve the problem of low reliability, increased circuit area and power consumption, and irrespective of the correlation of sensitive nodes. Tolerance differences, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] A radiation-resistant D flip-flop circuit based on a triple-interlock unit of the present invention will be further described in detail below in conjunction with the drawings and embodiments. The accompanying drawings constituting this application are used to provide a further understanding of the present invention, and the schematic embodiments of the present invention and their descriptions are used to explain the present invention, and do not constitute improper limitations to the present invention.

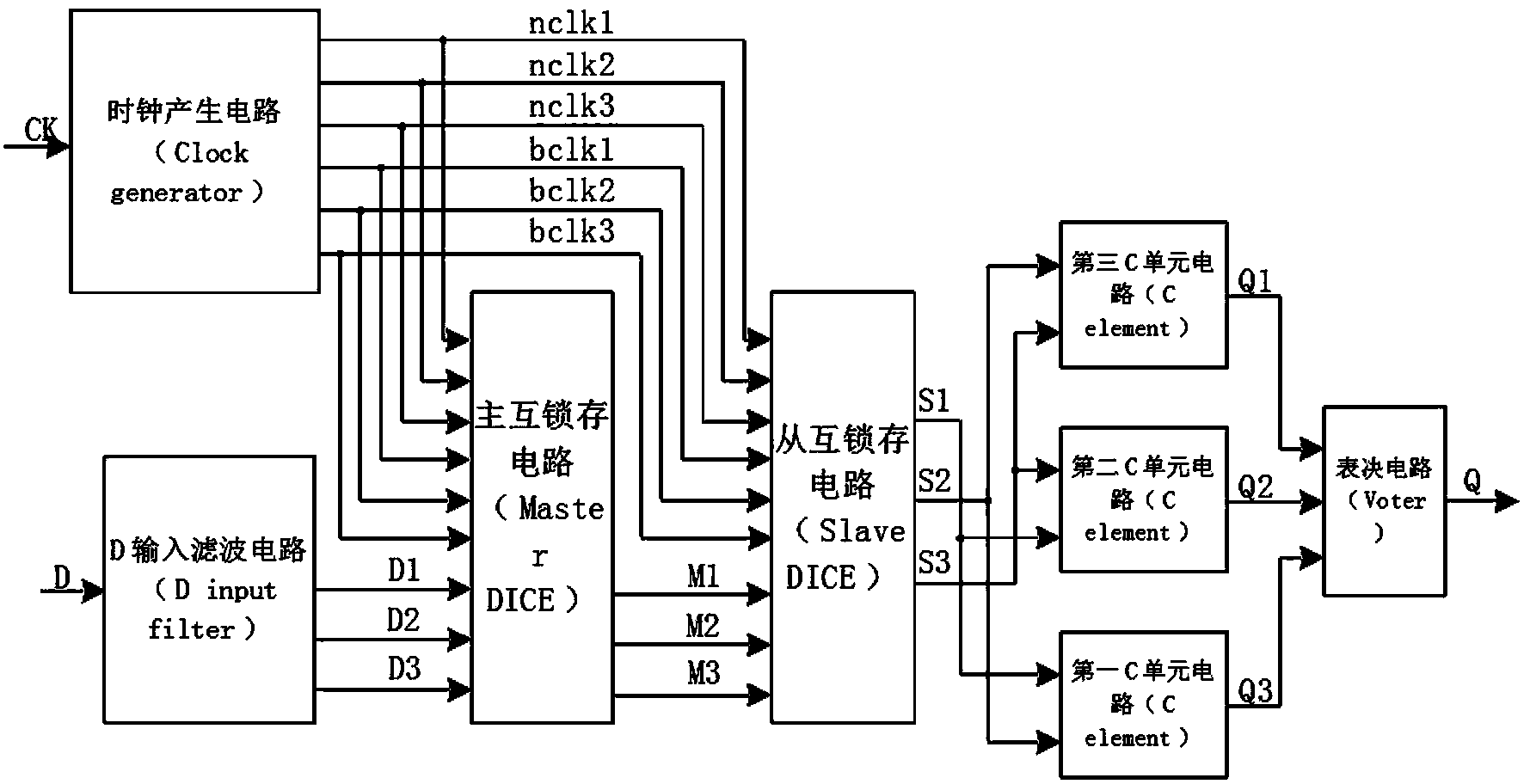

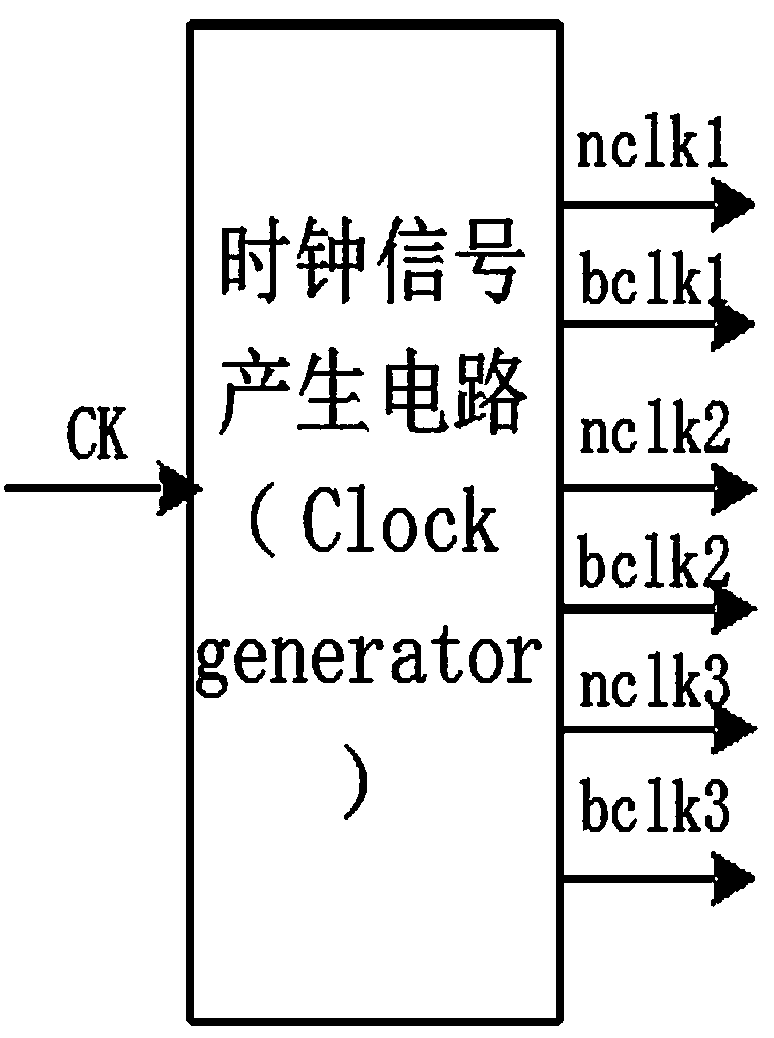

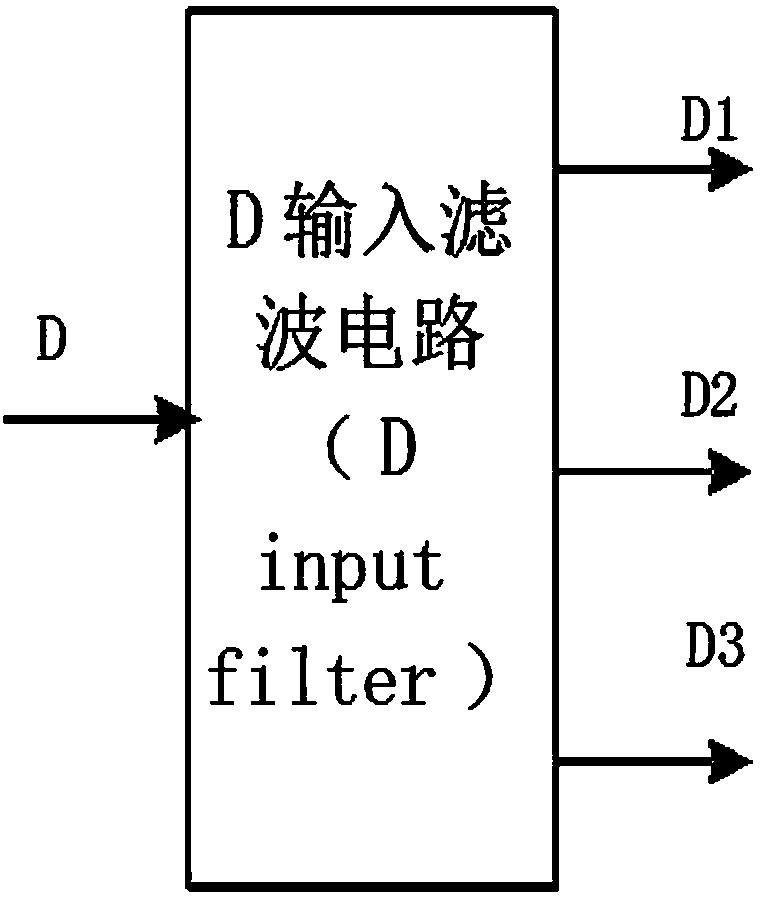

[0025] Depend on figure 1 , figure 2 , image 3 , Figure 4 , Figure 5 , Image 6 , Figure 7 , Figure 8 It can be seen that a radiation-resistant D flip-flop circuit based on Triple Interlocked storage Cell (DICE) in this embodiment is composed of a clock signal generation circuit (Clock generator), a D input filter circuit (D input filter), C unit circuit (C element) and voting circuit (voter), master interlock circuit (Master DICE) and slave interlock circu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com